A210 Datasheet

Copyright

Copyright © 2026 Zhihe Computing Technology (Shanghai) Co., Ltd. All rights reserved.

This document is the property of Zhihe Computing Technology (Shanghai) Co., Ltd. (“Company”) and may not be disclosed, given or transferred to any third party without the Company's agreement or written consent. If this clause is violated and caused loss to the Company shall be liable for compensation.

Contacts

Zhihe Computing Technology (Shanghai) Co., Ltd.

Address: 12F, Building 3, Xingchuang Technology Plaza, Lane 5005, Shenjiang Road, Pudong New District, Shanghai

Email: business@zhcomputing.com

Telephone: 0571-87208790

Overview

Features

Microprocessor

-

Octa-core RISC-V 64GCV processor (4×C920 + 4×C908)

-

RISC-V 64GCV C920@1.9 GHz

-

9 to 12 stage deep pipeline architecture

-

Superscalar architecture with 3-issue, 8-execution units (fully transparent to software)

-

In-order instruction fetch, out-of-order issue, out-of-order completion, and in-order retirement

-

64 KB I Cache and 64 KB D Cache for each core

-

1 MB L2 cache shared by 4 cores

-

Supports 588 GFlops@INT8/294 GFlops@FP16 vector operations

-

-

RISC-V 64GCV C908@1.9 GHz

-

9 stage pipeline architecture

-

In-order instruction fetch, in-order dual-issue, in-order execution, and in-order retirement

-

32 KB I Cache and 32 KB D Cache for each core

-

512 KB L2 Cache shared by 4 cores

-

Supports 121.6 GFlops@INT8/60.8 GFlops@FP16 vector operations

-

-

Each core supports vector operations, implementing the RISC-V V Extension.

-

Supports vector operations in FP16/BF16/FP32/FP64 formats

-

Supports integer operations in INT8/INT16/INT32/INT64 formats

-

128-bit vector register width

-

-

Little-endian mode

-

TEE and REE support

-

Supports independent executable domains

-

Provides isolation between zones

-

Provides isolation between applications, and between applications and kernels within a zone

-

Supports shared memory access across zones

-

Trusted communication between zones

-

The TEE environment is compliant with the Global Platform (GP) specification

-

-

SV39 Mode support

-

Two-level TLB MMU performs virtual-to-physical address translation and memory management

-

Floating-Point Unit (FPU) Support: half-precision (FP16), single-precision (FP32), and double-precision (FP64) floating-point operations

-

Supports DVFS

Neural Processing Unit

-

12TOPS@INT8

-

DeepSeek-7B can reach 8 tokens/s

-

4-Die multi-chip cascading DeepSeek-7B can reach 25 tokens/s

-

Supports INT4, INT8, INT16, FP8, FP16 and BF16

-

2MB SRAM

-

Supports CNN, and RNN

-

Supports deep learning frameworks: TensorFlow, Caffe, HuggingFace, ONNX, etc.

-

Supports Transformer acceleration and LLM

-

Lossless weight data compression

-

Supports mixed-precision (INT4/FP16) computation

Graphics Processing Unit

-

Available APIs:

-

Vulkan 1.1/1.2

-

OpenCL 1.1/1.2/2.0

-

OpenGL ES 1.1/2.0/3.0/3.1/3.2

-

-

Tile-based 3D graphic rendering with parallel processing

-

Programmable high-quality anti-aliasing

-

Advanced DMA operations to reduce main CPU load

-

Compressed texture encoding

-

Lossless data compression

-

Dedicated firmware execution processor

-

Performance:

-

50.34 GFLOPS operation

-

3D graphics acceleration engine: 3.14 GPixel@786MHz

-

64x F32 operations per cycle

-

128x F16 operations per cycle

-

32x integer operations per cycle

-

Geometric operations: 1 triangle operation per 4 clock cycles

-

Power Management Unit

-

1× RISC-V E902@100MHz

-

1× RTC

-

1× POR

-

1× Watchdog

-

Integrated Power Management Controller (PMC)

Memory Interface

-

LPDDR4/LPDDR4X

-

2× 32-bit LPDDR4/LPDDR4X with a maximum data rate of 4266 Mbps

-

JEDEC standards LPDDR4-2133/LPDDR4-3200/LPDDR4-3733/LPDDR4-4266/LPDDR4X-2133/LPDDR4X-3200/LPDDR4X-3733/LPDDR4X-4266 SDRAM

-

Dual channels, 32-bit data width per channel

-

Up to 16GB for LPDDR4/4x

-

Supports configurable timing parameters across various LPDDR4/LPDDR4X SDRAMs

-

Command reordering and scheduling to maximize the bandwidth utilization

-

Programmable On-Die Termination (ODT), and dynamic PVT compensation

-

-

SPI NOR/NAND Flash interface

-

Dual QSPI and dual SPI, up to 52.625MHz

-

Data bus width: 1-bit, 2-bit or 4-bit

-

-

eMMC5.1 interface

-

JEDEC standards eMMC 5.1 and eMMC 5.0

-

Supports boot from eMMC

-

8-bit data buses with HS400 (200MHz DDR) support

-

8-bit data buses with HS200 (200MHz SDR) support

-

8-bit data buses with DDR52 (52MHz DDR) support

-

Data bus width: 1-bit, 4-bit or 8-bit

-

-

SD 3.0 interface

-

Compliant with SD 3.0 specification

-

Single SD interface configurable as SD/SDIO with a maximum data bandwidth of 100 MB/s

-

Data bus width: 1-bit or 4-bit

-

Image Signal Processor

-

Supports up to 4 sensor inputs

-

Supports RAW 8/10/12-bit input

-

Supports up to 12 MPixel resolution

-

Supports LSC and Defect Pixel Correction (DPC)

-

Supports 3A (AE/AWB/AF) statistics output

-

Supports 2DNR, 3DNR and image sharpening

-

Supports distortion correction/fisheye correction

-

Supports True Wide Dynamic Range (WDR)

Dewarp Processor

-

Video scaling

-

Supports downscaling with a maximum reduction factor of 128x

-

Supports upscaling with a maximum magnification factor of 4x

-

Supports YUV and RGB888 output

-

Three scaling engines(SE) operating in parallel: SE0 (4K max output) + SE1 (1080P max output)+ SE2 (1080P max output)

-

-

Distortion correction, including fisheye correction, wide angle distortion correction, keystone correction, barrel distortion correction, etc.

Video Codec

-

Video decoding

-

H.265/HEVC decoding

-

Main/Main 10 Profile@level 5.2 with a maximum resolution of 4096x2160

-

Maximum decoding performance: 4K@120fps/16x1080P@30fps

-

-

H.264/AVC decoding

-

Baseline/Main/Main 10/High 10 Profile@level 5.2 with a maximum resolution of 4096x2160

-

Maximum decoding performance: 4K@120fps/16x1080P@30fps

-

-

AV1 decoding

-

AV1 Level 5.3 with a maximum resolution of 4096x2160

-

Maximum decoding performance: 4K@120fps/16x1080P@30fps

-

-

VP9 Profile0/2 with a maximum decoding performance of up to 4K@60fps

-

AVS2.0 Profile0/2 with a maximum decoding performance of up to 4K@60fps

-

VP6/7/8/AVS/AVS+/VC1/MPEG4 with a maximum decoding performance of up to 1920x1080@60fps

-

-

JPEG decoding

-

Compliant with ITU-T81 Baseline Profile

-

Supports JPEG decoding in YUV 4:0:0/YUV 4:2:0/YUV 4:2:2/YUV 4:4:4 formats

-

Supports decoding in sequential formats

-

Supports DCT-based JPEG decoding

-

Supports interlaced scan formats

-

Motion-JPEG is supported

-

-

Supported resolution range from 48x48 to 32768x32768

-

Maximum decoding performance for YUV4:2:0: 1080P@576fps

-

-

Video encoding

-

H.265/HEVC Main Profile with a maximum resolution of 4K

-

Motion Compensation: 1/2, 1/4 pixel precision

-

PU size in inter prediction: 64x64, 32x32, 16x16, 8x8

-

PU size in intra prediction: 32x32, 16x16, 8x8, 4x4

-

TU size: 32x32, 16x16, 8x8, 4x4

-

Entropy coding: CABAC

-

Supports Sample Adaptive Offset (SAO)

-

-

H.264 Baseline/Main/High Profile@level 4.2 with a maximum resolution of 4K

-

Motion Compensation: 1/2, 1/4 pixel precision

-

Inter prediction: sub-block types of 16x16, 16x8, and 8x16

-

Intra prediction: Intra4x4, Intra8x8, Intra16x16

-

Supports Trans4x4, Trans8x8

-

Entropy coding: CABAC, CAVLC

-

-

De-blocking filtering

-

Supports I/P frame encoding, and long-term reference frame

-

Supports Smart264/Smart 265 encoding

-

Supports QPMap/SkipMap

-

8 Regions of Interest (ROI)

-

Bitrate Control mode: CBR/VBR/FIXQP/QPMAP

-

Maximum encoding performance: 4K@60fps

-

-

JPEG encoding

-

Compliant with ISO/IEC 10918-1(CCITT T.81) Baseline Process(DCT Sequential)

-

Supported JPEG encoding formats: Semi-Planar YUV 4:2:0, Semi-Planar YUV 4:2:2, Monochrome (YUV 4:0:0)

-

Supported resolution range from 32x32 to 16384x16384, with both width and height being multiples of 2

-

Maximum encoding resolution: 1080P@312fps

-

MJPEG encoding with an output bitrate range from 2kbps to 600Mbps

-

-

On-screen display (OSD) overlay is supported before the encoding stage

2D Graphics Accelerator

-

Input/Output

-

Supported format: 8/10-bit YUV 4:2:2/YUV 4:2:0, RGB444/RGB565/RGB888/RGB101010, ARGB4444/ARGB1555/ARGB8888/ARGB2101010

-

The data storage format is compatible with processing modules such as ISP, VENC, VDEC, NPU, DPU, and GPU

-

-

2D operations

-

bitBlit

-

stretchBlit

-

rect fill & clear

-

filterblit

-

Alpha Blending

-

90/180/270 rotation

-

scale/crop

-

line

-

RGB2YUV

-

YUV2RGB

-

-

Multi-src blit

-

Supports blending of up to 8 rectangular sources with different sizes

-

Enable independent rotation and scaling parameters for each source

-

Display Processing Unit

-

Multi-screen heterogeneous display: DP0 (up to 4K@60fps) + DP1 (1080P@60fps) + DP2 (720P@60fps)

-

DP0/DP1 channel

-

each has 1 cursor layer and 1 video layer

-

4 shared layers can be assigned arbitrarily to DP0 or DP1

-

Supports dithering and Gamma correction lookup tables

-

Supports single-source mirror display/single-source scaling mirror display

-

-

DP2 channel exclusively reads data from system memory and outputs it directly

Video Interface

-

Video interface input

-

4-lane MIPI CSI2 D-PHY interface, with flexible Lane Configurations of 2×4lane/4×2lane/1×4lane+2×2lane

-

Compliant with MIPI D-PHY v1.1/v1.2

-

Maximum speed: 2.5Gbps/lane

-

Input format: RAW10/RAW12

-

Maximum input resolution: 12 MPixel

-

-

Display interface

-

HDMI TX interface

-

Compliant with HDMI 1.4/2.0

-

Total bandwidth is up to 18 Gbps

-

Maximum output resolution: 4K@60fps

-

Supports audio output

-

Supports up to 10-bit YUV/RGB output

-

Supports HDCP 1.4

-

Supports Hot Plug Detection(HPD)

-

-

MIPI DSI interface

-

1x 4-lane MIPI DSI D-PHY with a maximum resolution of 4K@60fps

-

Compliant with MIPI D-PHY v1.1/v1.2

-

Maximum speed: 2.5 Gbps/lane

-

Supports up to 8bit YUV/RGB output

-

-

USB3.1/DP/eDP combo interface

-

1x USB3.1/DP 1.4/eDP1.5 combo interface

-

Supports USB 3.1 output via a Type-C interface

-

Supports USB 3.1+2 lane DP via a Type-C interface

-

Supports USB 2.0+4 lane DP output via a Type-C interface

-

Supports USB 3.1 output via a Type-A interface +2-lane DP/eDP interface

-

Supports USB 2.0 output via a Type-A/C interface +4-lane DP/eDP interface

-

-

DP/eDP features

-

DP/eDP output with a maximum resolution of 4K@60fps

-

Supports audio output

-

Supports up to 10-bit YUV/RGB output

-

Supports HDCP 1.3

-

-

Supports Hot Plug Detection(HPD)

-

-

Audio Interface

-

1x 8-lane I2S/PCM interface

-

Supports full-duplex for RX/TX

-

Supports sample rate up to 384kHz

-

Audio resolution: 16bit, 24bit, and 32bit

-

Supports master mode

-

Supports 3 I2S formats (normal, left-Justified, right-Justified)

-

-

3x 2-lane I2S/PCM interface

-

Supports full-duplex for RX/TX

-

Supports sample rate up to 384kHz

-

Audio resolution: 16bit, 24bit, and 32bit

-

Supports master mode

-

Supports 3 I2S formats (normal, left-Justified, right-Justified)

-

-

1x PDM interface

-

Up to 8 channels

-

Supports sample rate up to 192kHz

-

Audio resolution: 16bit, 24bit

-

-

1x TDM/PCM interface

-

Supports TDM input

-

Up to 8 channels

-

Supports sample rate up to 192kHz

-

Audio resolution: 16bit, 24bit, and 32bit

-

Supports master/slave mode

-

Security

-

Dual-layer security: TEE+REE

-

Encryption algorithm

-

Symmetrical algorithms: AES, TDES, DES, SM4

-

Asymmetrical algorithms: RSA1024/2048/3072/4096, SM2

-

HASH algorithms: SHA-1/224/256/384/512, SM3, MD5

-

-

Hardware random number generator (HRNG)

-

Hardware-enforced isolation

-

Supports secure boot

Connectivity

-

Supports POR

-

Supports external reset

-

Internal RTC

-

4-channel ADC

-

10x UART ports

-

10x I2C ports

-

2x QSPI ports and 2x SPI ports

-

2x GMAC ports with RGMII/RMII support

-

3x 6-channel PWM ports

-

1x eMMC5.0/5.1 port

-

1x SD3.0/SDIO3.0 port

-

1x USB3.1/DP1.4/eDP1.5 Combo interface. The USB 3.1 interface can be configured as host or device mode

-

2x USB 2.0 interfaces can be configured as host or device mode

-

1x PCIe3.1/SATA3.0 Combo interface, supports the following configurations:

-

1 x4 RC/EP

-

1 x2 RC/EP+1 x1 RC

-

1 x2 RC/EP+2 SATA

-

1 x1 RC/EP+1 x1 RC+2 SATA

-

-

Integrated JTAG, GPIO, etc.

-

3x CAN interfaces, supporting CAN-FD

-

Integrated chip cascade interface, supporting board-level interconnection

Physical Specifications

-

Power consumption

- Multi-level low-power mode

-

Operating voltage

-

Voltage for core: 0.8V

-

Voltage for IO: 1.8V

-

Voltage for LPDDR4 IO: 1.1V

-

Voltage for LPDDR4x IO: 0.6V

-

-

Package

- RoHS, FC-BGA

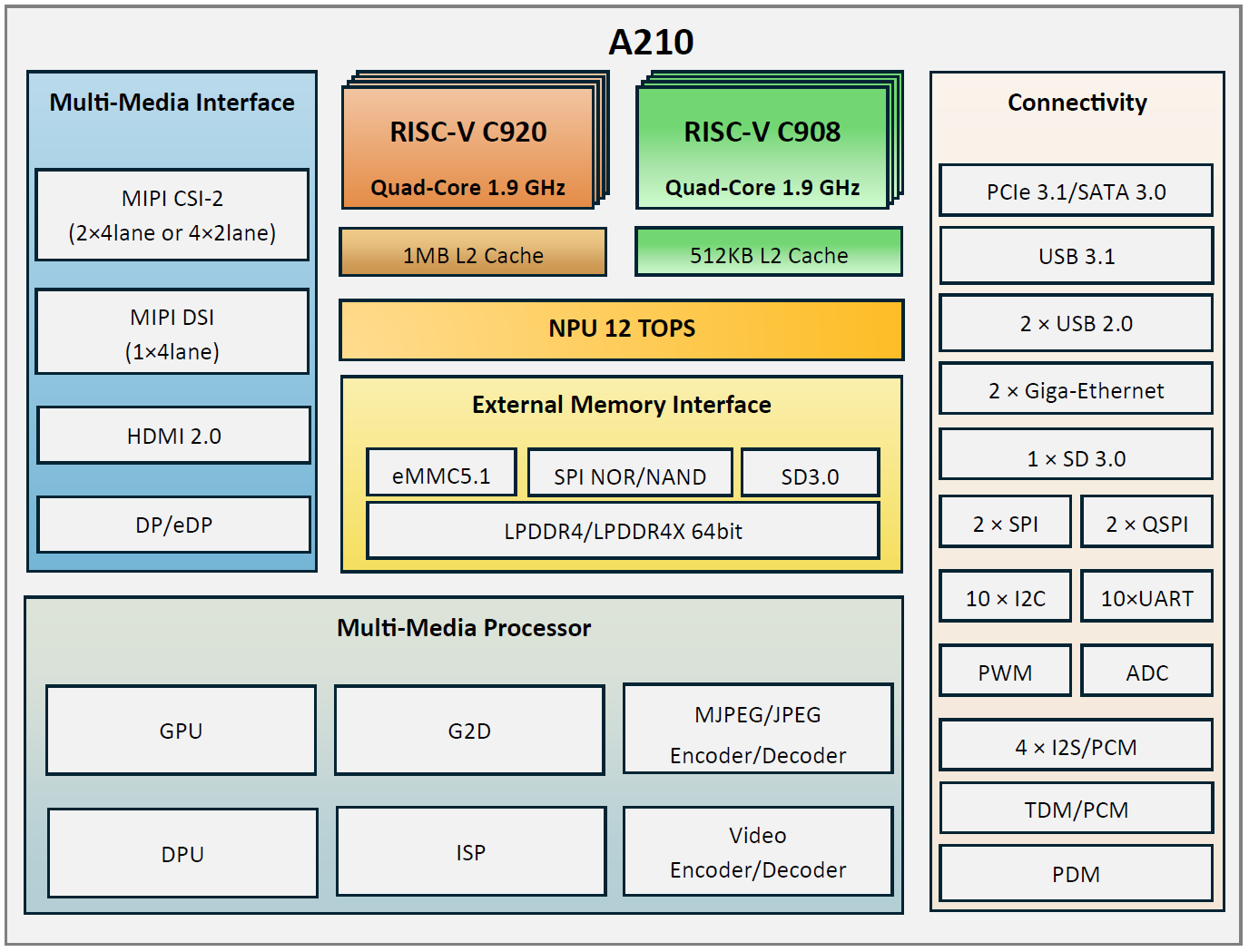

Block Diagram

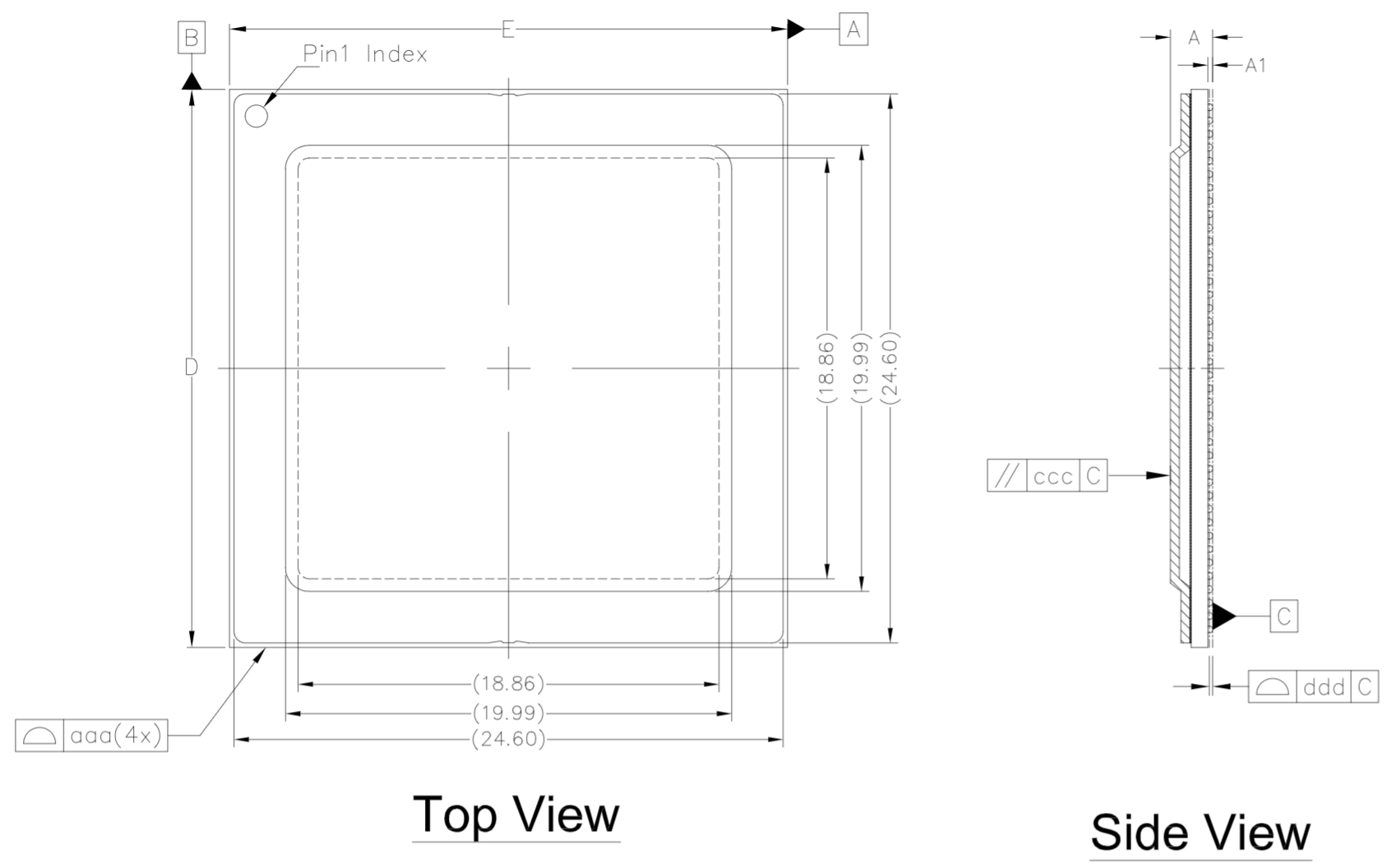

Package Information

Package Dimension

| Axis | Symbol | Common Dimensions | |||

|---|---|---|---|---|---|

| MIN. | NOM. | MAX. | |||

| Body Size: | X | E | 24.800 | 25.000 | 25.200 |

| Y | D | 24.800 | 25.000 | 25.200 | |

| Ball Pitch: | e | 0.6 | |||

| Total Thickness: | A | 1.768 | 1.889 | 2.010 | |

| Lid Height: | 0.875 Ref. | ||||

| Substrate Thickness: | 0.644 | 0.754 | 0.864 | ||

| Ball Diameter: | 0.300 | ||||

| Stand Off: | A1 | 0.160 | 0.210 | 0.260 | |

| Ball Width: | b | 0.260 | 0.310 | 0.360 | |

| Package Edge Tolerance: | aaa | 0.200 | |||

| Lid Flatness: | ccc | 0.050 | |||

| Coplanarity: | ddd | 0.150 | |||

| Ball Offset (Package): | eee | 0.200 | |||

| Ball Offset (Ball): | fff | 0.080 | |||

| Ball Count: | n | 1373 | |||

| Edge Ball Center to Center: | X | E1 | 23.400 | ||

| Y | D1 | 23.400 | |||

| Edge Ball Center to Package Edge: | X | g | 0.800 Ref. | ||

| Y | f | 0.800 Ref. | |||

Note:

PKG total thickness (A) does not include the warpage value.

Top Marking

Thermal Management

| Symbol | Parameter | Typical | Unit |

|---|---|---|---|

| θJA | Junction-to-ambient thermal resistance Airflow velocity: 0 m/s (still air) | 7.53 | °C/W |

| θJB | Junction-to-board thermal resistance Airflow velocity: 0 m/s (still air) | 2.86 | °C/W |

| θJC | Junction-to-case thermal resistance Airflow velocity: 0 m/s (still air) | 0.31 | °C/W |

Note:

The thermal resistance parameters are specified per the JESD51-2 standard. Their actual values depend on specific conditions such as PCB design, dimensions, thickness, materials, and other physical factors, and require evaluation based on the actual application.

MSL Information

Moisture sensitivity Level(MSL): 4

Pin Description

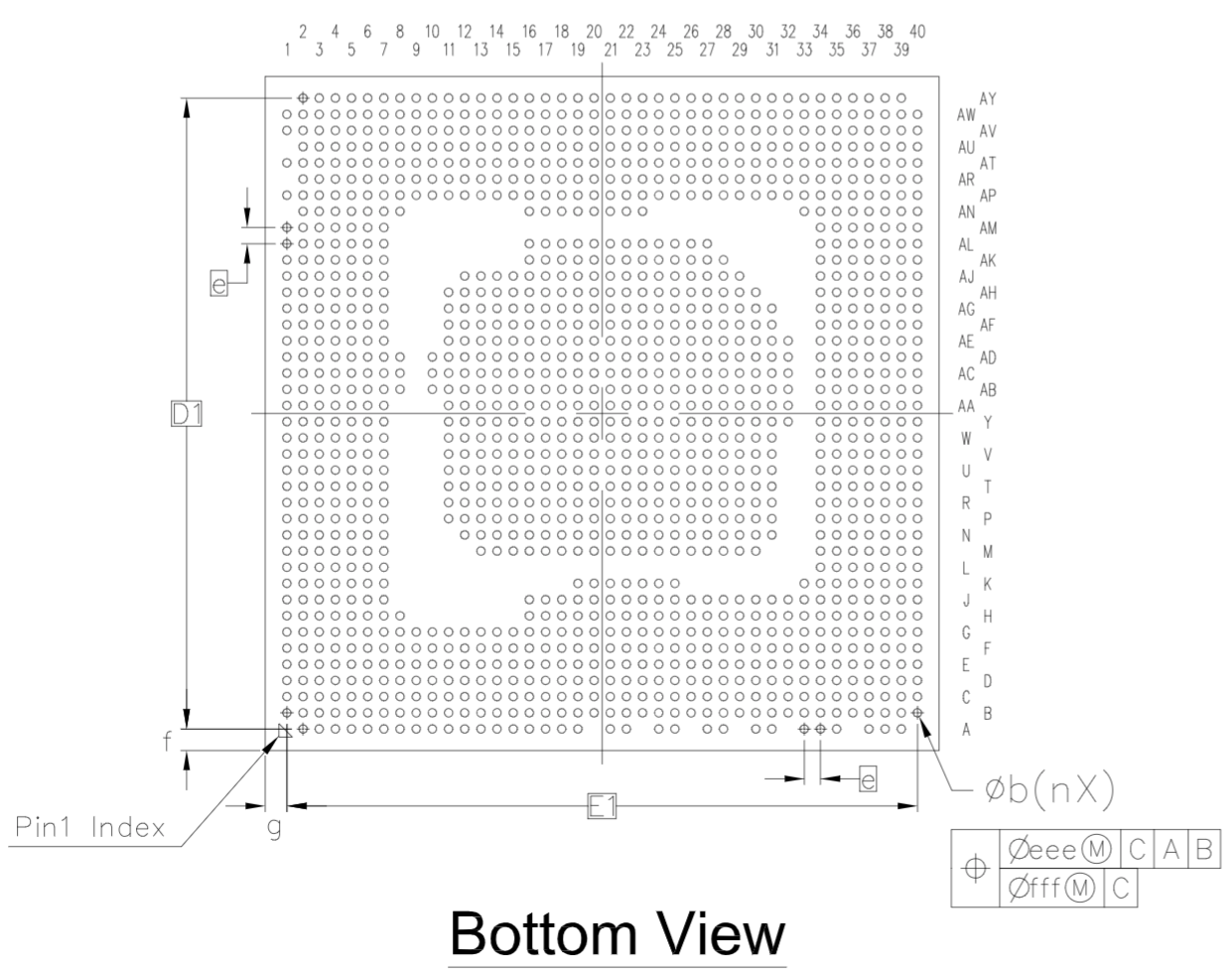

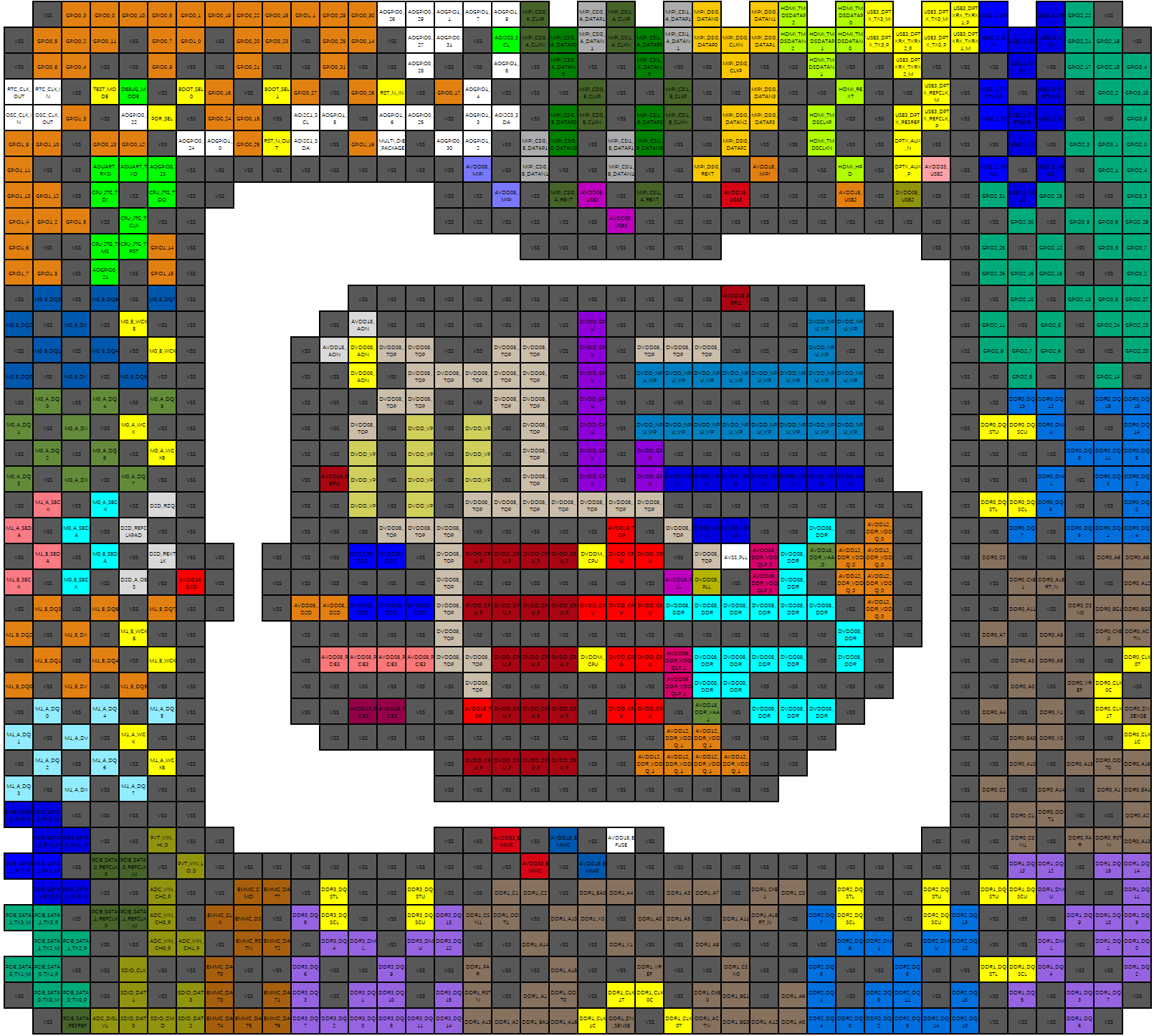

Ball Map

Pin Number List

| Pin | Pin Name | Pin | Pin Name | Pin | Pin Name |

|---|---|---|---|---|---|

| A2 | VSS | AF16 | DVDD08_TOP | AP17 | VSS |

| A3 | GPIO0_3 | AF17 | DVDD08_TOP | AP18 | VSS |

| A4 | GPIO0_0 | AF18 | DVDD_CPU_P | AP19 | AVDD33_EMMC |

| A5 | GPIO0_10 | AF19 | DVDD_CPU_P | AP20 | VSS |

| A6 | GPIO0_8 | AF20 | DVDD_CPU_P | AP21 | AVDD18_EMMC |

| A7 | GPIO0_1 | AF21 | DVDDM_CPU | AP22 | VSS |

| A8 | GPIO0_19 | AF22 | DVDD_CPU | AP23 | VSS |

| A9 | GPIO0_22 | AF23 | DVDD_CPU | AP24 | VSS |

| A10 | GPIO0_18 | AF24 | AVDD06_DDR_VDDQLP_1 | AP25 | VSS |

| A11 | GPIO1_1 | AF25 | DVDD08_DDR | AP26 | VSS |

| A12 | GPIO0_29 | AF26 | DVDD08_DDR | AP27 | VSS |

| A13 | GPIO0_30 | AF27 | DVDD08_DDR | AP28 | VSS |

| A14 | AOGPIO0_26 | AF28 | DVDD08_DDR | AP29 | VSS |

| A15 | AOGPIO0_29 | AF29 | VSS | AP30 | VSS |

| A16 | AOGPIO1_1 | AF30 | DVDD08_DDR | AP31 | VSS |

| A17 | AOGPIO1_7 | AF31 | VSS | AP32 | VSS |

| A18 | AOGPIO1_9 | AF34 | VSS | AP33 | VSS |

| A19 | MIPI_CSI0_A_CLKP | AF35 | VSS | AP34 | VSS |

| A21 | MIPI_CSI0_A_DATAP1 | AF36 | DDR0_A3 | AP35 | VSS |

| A22 | MIPI_CSI1_A_CLKP | AF37 | DDR0_A5 | AP36 | DDR1_DQ13 |

| A24 | MIPI_CSI1_A_DATAP1 | AF38 | VSS | AP37 | DDR1_DQ12 |

| A25 | MIPI_DSI0_DATAN0 | AF39 | VSS | AP38 | VSS |

| A27 | MIPI_DSI0_DATAN1 | AF40 | DDR0_CLK0T | AP39 | DDR1_DQ15 |

| A28 | HDMI_TMDSDATAP2 | AG1 | M1_B_DQ0 | AP40 | DDR1_DQ14 |

| A30 | HDMI_TMDSDATAP0 | AG2 | VSS | AR2 | PCIE_SATA_1_RX3_P |

| A31 | USB3_DPTX_TX3_M | AG3 | M1_B_DV | AR3 | PCIE_SATA_1_RX3_M |

| A33 | USB3_DPTX_TX0_M | AG4 | VSS | AR4 | VSS |

| A34 | USB3_DPTXRX_TXRX1_P | AG5 | M1_B_DQ5 | AR5 | VSS |

| A35 | USB2_2_DP | AG6 | VSS | AR6 | ADC_VIN_CH2_P |

| A37 | USB2_0_DP | AG7 | VSS | AR7 | VSS |

| A38 | GPIO2_22 | AG11 | VSS | AR8 | VSS |

| A39 | VSS | AG12 | VSS | AR9 | EMMC_CMD |

| AA1 | M1_A_SBDA | AG13 | VSS | AR10 | EMMC_DAT7 |

| AA2 | VSS | AG14 | VSS | AR11 | VSS |

| AA3 | M0_A_SBDA | AG15 | VSS | AR12 | DDR3_DQSTL |

| AA4 | VSS | AG16 | VSS | AR13 | VSS |

| AA5 | D2D_REFCLKPAD | AG17 | DVDD08_TOP | AR14 | VSS |

| AA6 | VSS | AG18 | VSS | AR15 | DDR3_DQSTU |

| AA7 | VSS | AG19 | VSS | AR16 | VSS |

| AA11 | VSS | AG20 | VSS | AR17 | VSS |

| AA12 | VSS | AG21 | VSS | AR18 | DDR1_C1 |

| AA13 | VSS | AG22 | VSS | AR19 | DDR1_C2 |

| AA14 | DVDD08_TOP | AG23 | VSS | AR20 | VSS |

| AA15 | DVDD08_TOP | AG24 | AVDD06_DDR_VDDQLP_1 | AR21 | DDR1_BA0 |

| AA16 | DVDD08_TOP | AG25 | DVDD08_DDR | AR22 | DDR1_A4 |

| AA17 | VSS | AG26 | DVDD08_DDR | AR23 | VSS |

| AA18 | VSS | AG27 | VSS | AR24 | DDR1_A3 |

| AA19 | VSS | AG28 | VSS | AR25 | DDR1_A7 |

| AA20 | VSS | AG29 | VSS | AR26 | VSS |

| AA21 | VSS | AG30 | VSS | AR27 | DDR1_CKE1 |

| AA22 | AVDD18_TOP | AG31 | VSS | AR28 | DDR1_C0 |

| AA23 | VSS | AG34 | VSS | AR29 | VSS |

| AA24 | DVDD08_TOP | AG35 | VSS | AR30 | DDR2_DQSTL |

| AA25 | DVDD_NPU | AG36 | DDR0_A0 | AR31 | VSS |

| AA26 | DVDD_NPU | AG37 | VSS | AR32 | VSS |

| AA27 | VSS | AG38 | DDR0_VREF | AR33 | DDR2_DQSTU |

| AA28 | VSS | AG39 | DDR0_CLK0C | AR34 | VSS |

| AA29 | DVDD08_DDR | AG40 | VSS | AR35 | DDR1_DQSTU |

| AA30 | VSS | AH1 | VSS | AR36 | DDR1_DQSCU |

| AA31 | AVDD12_DDR_VDDQ_0 | AH2 | M1_A_DQ0 | AR37 | DDR1_DMU |

| AA32 | VSS | AH3 | VSS | AR38 | VSS |

| AA34 | VSS | AH4 | M1_A_DQ4 | AR39 | VSS |

| AA35 | VSS | AH5 | VSS | AR40 | DDR1_DQ11 |

| AA36 | DDR0_DQ7 | AH6 | M1_A_DQ5 | AT1 | PCIE_SATA_1_TX3_M |

| AA37 | VSS | AH7 | VSS | AT2 | PCIE_SATA_1_TX3_P |

| AA38 | DDR0_DQ5 | AH11 | VSS | AT3 | VSS |

| AA39 | DDR0_DQ1 | AH12 | VSS | AT4 | PCIE_SATA_1_REFCLK_P |

| AA40 | DDR0_DQ4 | AH13 | AVDD18_PCIE3 | AT5 | PCIE_SATA_1_REFCLK_M |

| AB1 | VSS | AH14 | AVDD18_PCIE3 | AT6 | ADC_VIN_CH3_P |

| AB2 | M1_B_SBDA | AH15 | VSS | AT7 | VSS |

| AB3 | VSS | AH16 | VSS | AT8 | EMMC_CLK |

| AB4 | M0_B_SBDA | AH17 | AVDD18_TOP | AT9 | EMMC_DS |

| AB5 | VSS | AH18 | DVDD_CPU_P | AT10 | VSS |

| AB6 | D2D_REXT1K | AH19 | DVDD_CPU_P | AT11 | DDR3_DQ5 |

| AB7 | VSS | AH20 | DVDD_CPU_P | AT12 | DDR3_DQSCL |

| AB8 | VSS | AH21 | VSS | AT13 | VSS |

| AB10 | VSS | AH22 | DVDD_CPU | AT14 | VSS |

| AB11 | VSS | AH23 | DVDD_CPU | AT15 | DDR3_DQSCU |

| AB12 | VSS | AH24 | VSS | AT16 | DDR3_DQ13 |

| AB13 | DVDD08_D2D | AH25 | AVDD18_DDR_VAA_1 | AT17 | DDR1_CSN1 |

| AB14 | DVDD08_D2D | AH26 | VSS | AT18 | DDR1_ODT1 |

| AB15 | VSS | AH27 | DVDD08_DDR | AT19 | VSS |

| AB16 | DVDD08_TOP | AH28 | DVDD08_DDR | AT20 | DDR1_A10 |

| AB17 | DVDD_CPU_P | AH29 | DVDD08_DDR | AT21 | DDR1_X0 |

| AB18 | DVDD_CPU_P | AH30 | VSS | AT22 | VSS |

| AB19 | DVDD_CPU_P | AH34 | VSS | AT23 | DDR1_A0 |

| AB20 | DVDD_CPU_P | AH35 | DDR0_A4 | AT24 | DDR1_A5 |

| AB21 | DVDDM_CPU | AH36 | VSS | AT25 | VSS |

| AB22 | DVDD_CPU | AH37 | DDR0_X1 | AT26 | DDR1_A11 |

| AB23 | DVDD_CPU | AH38 | VSS | AT27 | DDR1_ALERT_N |

| AB24 | VSS | AH39 | DDR0_CLK1T | AT28 | VSS |

| AB25 | DVDD08_TOP | AH40 | DDR0_ZN_SENSE | AT29 | DDR2_DQ7 |

| AB26 | AVSS_PLL | AJ1 | M1_A_DQ1 | AT30 | DDR2_DQSCL |

| AB27 | AVDD06_DDR_VDDQLP_0 | AJ2 | VSS | AT31 | VSS |

| AB28 | DVDD08_DDR | AJ3 | M1_A_DV | AT32 | VSS |

| AB29 | AVDD18_DDR_VAA_0 | AJ4 | VSS | AT33 | DDR2_DQSCU |

| AB30 | AVDD12_DDR_VDDQ_0 | AJ5 | M1_A_WCK | AT34 | DDR2_DQ13 |

| AB31 | AVDD12_DDR_VDDQ_0 | AJ6 | VSS | AT35 | VSS |

| AB32 | VSS | AJ7 | VSS | AT36 | VSS |

| AB34 | VSS | AJ12 | VSS | AT37 | VSS |

| AB35 | DDR0_C0 | AJ13 | VSS | AT38 | DDR1_DQ9 |

| AB36 | VSS | AJ14 | VSS | AT39 | DDR1_DQ10 |

| AB37 | VSS | AJ15 | VSS | AT40 | DDR1_DQ8 |

| AB38 | VSS | AJ16 | VSS | AU2 | PCIE_SATA_1_TX2_M |

| AB39 | DDR0_A6 | AJ17 | VSS | AU3 | PCIE_SATA_1_TX2_P |

| AB40 | DDR0_A8 | AJ18 | VSS | AU4 | VSS |

| AC1 | M1_B_SBCK | AJ19 | VSS | AU5 | VSS |

| AC2 | VSS | AJ20 | VSS | AU6 | ADC_VIN_CH0_P |

| AC3 | M0_B_SBCK | AJ21 | VSS | AU7 | ADC_VIN_CH1_P |

| AC4 | VSS | AJ22 | VSS | AU8 | VSS |

| AC5 | D2D_A_OBS | AJ23 | VSS | AU9 | EMMC_RSTN |

| AC6 | VSS | AJ24 | AVDD12_DDR_VDDQ_1 | AU10 | EMMC_DAT2 |

| AC7 | AVDD18_D2D | AJ25 | AVDD12_DDR_VDDQ_1 | AU11 | VSS |

| AC8 | VSS | AJ26 | VSS | AU12 | DDR3_DQ4 |

| AC10 | VSS | AJ27 | VSS | AU13 | DDR3_DML |

| AC11 | VSS | AJ28 | VSS | AU14 | VSS |

| AC12 | VSS | AJ29 | VSS | AU15 | DDR3_DMU |

| AC13 | VSS | AJ34 | VSS | AU16 | DDR3_DQ12 |

| AC14 | VSS | AJ35 | VSS | AU17 | VSS |

| AC15 | VSS | AJ36 | DDR0_BA0 | AU18 | VSS |

| AC16 | DVDD08_TOP | AJ37 | DDR0_X0 | AU19 | DDR1_A14 |

| AC17 | VSS | AJ38 | VSS | AU20 | VSS |

| AC18 | VSS | AJ39 | VSS | AU21 | VSS |

| AC19 | VSS | AJ40 | DDR0_CLK1C | AU22 | DDR1_X1 |

| AC20 | VSS | AK1 | VSS | AU23 | VSS |

| AC21 | VSS | AK2 | M1_A_DQ2 | AU24 | VSS |

| AC22 | VSS | AK3 | VSS | AU25 | DDR1_A9 |

| AC23 | VSS | AK4 | M1_A_DQ6 | AU26 | VSS |

| AC24 | AVDD18_PLL | AK5 | VSS | AU27 | VSS |

| AC25 | DVDD08_PLL | AK6 | M1_A_WCKB | AU28 | VSS |

| AC26 | VSS | AK7 | VSS | AU29 | VSS |

| AC27 | AVDD06_DDR_VDDQLP_0 | AK16 | VSS | AU30 | DDR2_DQ6 |

| AC28 | DVDD08_DDR | AK17 | DVDD_CPU_P | AU31 | DDR2_DML |

| AC29 | VSS | AK18 | DVDD_CPU_P | AU32 | VSS |

| AC30 | AVDD12_DDR_VDDQ_0 | AK19 | DVDD_CPU_P | AU33 | DDR2_DMU |

| AC31 | AVDD12_DDR_VDDQ_0 | AK20 | DVDD_CPU_P | AU34 | DDR2_DQ12 |

| AC32 | VSS | AK21 | VSS | AU35 | VSS |

| AC34 | VSS | AK22 | VSS | AU36 | VSS |

| AC35 | VSS | AK23 | AVDD12_DDR_VDDQ_1 | AU37 | DDR1_DML |

| AC36 | DDR0_CKE1 | AK24 | AVDD12_DDR_VDDQ_1 | AU38 | VSS |

| AC37 | DDR0_ALERT_N | AK25 | AVDD12_DDR_VDDQ_1 | AU39 | DDR1_DQ1 |

| AC38 | VSS | AK26 | AVDD12_DDR_VDDQ_1 | AU40 | DDR1_DQ0 |

| AC39 | VSS | AK27 | VSS | AV1 | PCIE_SATA_0_TX1_M |

| AC40 | DDR0_A12 | AK28 | VSS | AV2 | PCIE_SATA_0_TX1_P |

| AD1 | VSS | AK34 | VSS | AV3 | VSS |

| AD2 | M1_B_DQ3 | AK35 | VSS | AV4 | VSS |

| AD3 | VSS | AK36 | DDR0_A10 | AV5 | SDIO_CLK |

| AD4 | M1_B_DQ6 | AK37 | VSS | AV6 | VSS |

| AD5 | VSS | AK38 | DDR0_A15 | AV7 | VSS |

| AD6 | M1_B_DQ7 | AK39 | DDR0_ODT0 | AV8 | EMMC_DAT0 |

| AD7 | VSS | AK40 | DDR0_A16 | AV9 | VSS |

| AD8 | VSS | AL1 | M1_A_DQ3 | AV10 | VSS |

| AD10 | VSS | AL2 | VSS | AV11 | DDR3_DQ6 |

| AD11 | AVDD08_D2D | AL3 | M1_A_DX | AV12 | VSS |

| AD12 | AVDD08_D2D | AL4 | VSS | AV13 | VSS |

| AD13 | DVDD08_D2D | AL5 | M1_A_DQ7 | AV14 | DDR3_DQ9 |

| AD14 | DVDD08_D2D | AL6 | VSS | AV15 | VSS |

| AD15 | DVDD08_D2D | AL7 | VSS | AV16 | VSS |

| AD16 | DVDD08_TOP | AL16 | VSS | AV17 | DDR1_PAR |

| AD17 | DVDD_CPU_P | AL17 | VSS | AV18 | VSS |

| AD18 | DVDD_CPU_P | AL18 | VSS | AV19 | VSS |

| AD19 | DVDD_CPU_P | AL19 | VSS | AV20 | DDR1_A15 |

| AD20 | DVDD_CPU_P | AL20 | VSS | AV21 | VSS |

| AD21 | DVDD_CPU | AL21 | VSS | AV22 | VSS |

| AD22 | DVDD_CPU | AL22 | VSS | AV23 | DDR1_VREF |

| AD23 | DVDD_CPU | AL23 | VSS | AV24 | VSS |

| AD24 | DVDD08_DDR | AL24 | VSS | AV25 | VSS |

| AD25 | DVDD08_DDR | AL25 | VSS | AV26 | DDR1_CSN0 |

| AD26 | DVDD08_DDR | AL26 | VSS | AV27 | VSS |

| AD27 | DVDD08_DDR | AL27 | VSS | AV28 | VSS |

| AD28 | DVDD08_DDR | AL34 | VSS | AV29 | DDR2_DQ5 |

| AD29 | DVDD08_DDR | AL35 | DDR0_C2 | AV30 | VSS |

| AD30 | VSS | AL36 | VSS | AV31 | VSS |

| AD31 | AVDD12_DDR_VDDQ_0 | AL37 | DDR0_A14 | AV32 | DDR2_DQ8 |

| AD32 | VSS | AL38 | VSS | AV33 | VSS |

| AD34 | VSS | AL39 | DDR0_A1 | AV34 | VSS |

| AD35 | VSS | AL40 | DDR0_BA1 | AV35 | DDR1_DQSTL |

| AD36 | DDR0_A11 | AM1 | PCIE_SATA_0_RX0_P | AV36 | DDR1_DQSCL |

| AD37 | VSS | AM2 | PCIE_SATA_0_RX0_M | AV37 | DDR1_DQ4 |

| AD38 | DDR0_CSN0 | AM3 | VSS | AV38 | VSS |

| AD39 | DDR0_BG1 | AM4 | VSS | AV39 | VSS |

| AD40 | DDR0_BG0 | AM5 | VSS | AV40 | DDR1_DQ2 |

| AE1 | M1_B_DQ2 | AM6 | VSS | AW1 | VSS |

| AE2 | VSS | AM7 | VSS | AW2 | PCIE_SATA_0_TX0_M |

| AE3 | M1_B_DX | AM34 | VSS | AW3 | PCIE_SATA_0_TX0_P |

| AE4 | VSS | AM35 | VSS | AW4 | VSS |

| AE5 | M1_B_WCKB | AM36 | DDR0_C1 | AW5 | SDIO_DAT1 |

| AE6 | VSS | AM37 | DDR0_ODT1 | AW6 | VSS |

| AE7 | VSS | AM38 | VSS | AW7 | SDIO_DAT3 |

| AE11 | VSS | AM39 | VSS | AW8 | EMMC_DAT3 |

| AE12 | VSS | AM40 | DDR0_A2 | AW9 | VSS |

| AE13 | VSS | AN2 | PCIE_SATA_0_RX1_P | AW10 | EMMC_DAT1 |

| AE14 | VSS | AN3 | PCIE_SATA_0_RX1_M | AW11 | DDR3_DQ3 |

| AE15 | VSS | AN4 | VSS | AW12 | VSS |

| AE16 | DVDD08_TOP | AN5 | VSS | AW13 | DDR3_DQ1 |

| AE17 | VSS | AN6 | PVT_VIN_HI_0 | AW14 | DDR3_DQ10 |

| AE18 | VSS | AN7 | VSS | AW15 | VSS |

| AE19 | VSS | AN8 | VSS | AW16 | DDR3_DQ15 |

| AE20 | VSS | AN16 | VSS | AW17 | DDR1_RSTN |

| AE21 | VSS | AN17 | VSS | AW18 | VSS |

| AE22 | VSS | AN18 | AVDD33_EMMC | AW19 | DDR1_A1 |

| AE23 | VSS | AN19 | VSS | AW20 | DDR1_ODT0 |

| AE24 | VSS | AN20 | AVDD18_EMMC | AW21 | VSS |

| AE25 | VSS | AN21 | VSS | AW22 | DDR1_CLK1T |

| AE26 | VSS | AN22 | AVDD18_EFUSE | AW23 | DDR1_CLK0C |

| AE27 | VSS | AN23 | VSS | AW24 | VSS |

| AE28 | VSS | AN33 | VSS | AW25 | DDR1_CKE0 |

| AE29 | VSS | AN34 | VSS | AW26 | DDR1_BG1 |

| AE30 | DVDD08_DDR | AN35 | VSS | AW27 | VSS |

| AE31 | VSS | AN36 | DDR0_CSN1 | AW28 | DDR1_A6 |

| AE32 | VSS | AN37 | VSS | AW29 | DDR2_DQ1 |

| AE34 | VSS | AN38 | DDR0_PAR | AW30 | VSS |

| AE35 | DDR0_A7 | AN39 | DDR0_RSTN | AW31 | DDR2_DQ3 |

| AE36 | VSS | AN40 | DDR0_A13 | AW32 | DDR2_DQ11 |

| AE37 | DDR0_A9 | AP1 | PCIE_SATA_1_RX2_P | AW33 | VSS |

| AE38 | VSS | AP2 | PCIE_SATA_1_RX2_M | AW34 | DDR2_DQ15 |

| AE39 | DDR0_CKE0 | AP3 | VSS | AW35 | VSS |

| AE40 | DDR0_ACTN | AP4 | PCIE_SATA_0_REFCLK_P | AW36 | DDR1_DQ5 |

| AF1 | VSS | AP5 | PCIE_SATA_0_REFCLK_M | AW37 | VSS |

| AF2 | M1_B_DQ1 | AP6 | VSS | AW38 | DDR1_DQ3 |

| AF3 | VSS | AP7 | PVT_VIN_LO_0 | AW39 | DDR1_DQ7 |

| AF4 | M1_B_DQ4 | AP8 | VSS | AW40 | VSS |

| AF5 | VSS | AP9 | VSS | AY2 | VSS |

| AF6 | M1_B_WCK | AP10 | VSS | AY3 | PCIE_SATA_RESREF |

| AF7 | VSS | AP11 | VSS | AY4 | ADC_DISLVL |

| AF11 | VSS | AP12 | VSS | AY5 | SDIO_DAT0 |

| AF12 | AVDD08_PCIE3 | AP13 | VSS | AY6 | SDIO_CMD |

| AF13 | AVDD08_PCIE3 | AP14 | VSS | AY7 | SDIO_DAT2 |

| AF14 | AVDD08_PCIE3 | AP15 | VSS | AY8 | EMMC_DAT4 |

| AF15 | AVDD08_PCIE3 | AP16 | VSS | AY9 | EMMC_DAT5 |

| AY10 | EMMC_DAT6 | F39 | GPIO3_1 | P23 | DVDD08_TOP |

| AY11 | DDR3_DQ7 | F40 | GPIO2_0 | P24 | DVDD08_TOP |

| AY12 | DDR3_DQ2 | G1 | GPIO1_11 | P25 | DVDD08_TOP |

| AY13 | DDR3_DQ0 | G2 | VSS | P26 | VSS |

| AY14 | DDR3_DQ8 | G3 | VSS | P27 | VSS |

| AY15 | DDR3_DQ11 | G4 | AOUART_RXD | P28 | VSS |

| AY16 | DDR3_DQ14 | G5 | AOUART_TXD | P29 | DVDD_NPU_VIP |

| AY17 | DDR1_A13 | G6 | AOGPIO0_23 | P30 | VSS |

| AY18 | DDR1_A2 | G7 | VSS | P31 | VSS |

| AY19 | DDR1_BA1 | G8 | VSS | P34 | VSS |

| AY20 | DDR1_A16 | G9 | VSS | P35 | GPIO2_9 |

| AY21 | DDR1_CLK1C | G10 | VSS | P36 | GPIO2_7 |

| AY22 | DDR1_ZN_SENSE | G11 | VSS | P37 | GPIO2_6 |

| AY23 | VSS | G12 | VSS | P38 | VSS |

| AY24 | DDR1_CLK0T | G13 | VSS | P39 | VSS |

| AY25 | DDR1_ACTN | G14 | VSS | P40 | GPIO2_20 |

| AY26 | DDR1_BG0 | G15 | VSS | R1 | M0_B_DQ0 |

| AY27 | DDR1_A12 | G16 | VSS | R2 | VSS |

| AY28 | DDR1_A8 | G17 | AVDD08_MIPI | R3 | M0_B_DV |

| AY29 | DDR2_DQ4 | G18 | VSS | R4 | VSS |

| AY30 | DDR2_DQ0 | G19 | MIPI_CSI0_B_DATAN1 | R5 | M0_B_DQ5 |

| AY31 | DDR2_DQ2 | G20 | VSS | R6 | VSS |

| AY32 | DDR2_DQ9 | G21 | VSS | R7 | VSS |

| AY33 | DDR2_DQ14 | G22 | MIPI_CSI1_B_DATAN1 | R11 | VSS |

| AY34 | DDR2_DQ10 | G23 | VSS | R12 | VSS |

| AY35 | VSS | G24 | VSS | R13 | DVDD08_AON |

| AY36 | VSS | G25 | MIPI_DSI0_REXT | R14 | VSS |

| AY37 | VSS | G26 | VSS | R15 | DVDD08_TOP |

| AY38 | DDR1_DQ6 | G27 | AVDD18_MIPI | R16 | DVDD08_TOP |

| AY39 | VSS | G28 | VSS | R17 | DVDD08_TOP |

| B1 | VSS | G29 | VSS | R18 | DVDD08_TOP |

| B2 | GPIO0_5 | G30 | HDMI_HPD | R19 | DVDD08_TOP |

| B3 | GPIO0_2 | G31 | VSS | R20 | VSS |

| B4 | GPIO0_11 | G32 | DPTX_AUX_P | R21 | DVDD_GPU |

| B5 | VSS | G33 | AVDD33_USB2 | R22 | VSS |

| B6 | GPIO0_7 | G34 | VSS | R23 | DVDD_NPU_VIP |

| B7 | GPIO1_0 | G35 | USB2_2_VBUS | R24 | DVDD_NPU_VIP |

| B8 | VSS | G36 | VSS | R25 | DVDD_NPU_VIP |

| B9 | GPIO0_20 | G37 | USB2_0_VBUS | R26 | DVDD_NPU_VIP |

| B10 | GPIO0_23 | G38 | VSS | R27 | DVDD_NPU_VIP |

| B11 | VSS | G39 | GPIO2_1 | R28 | DVDD_NPU_VIP |

| B12 | GPIO0_28 | G40 | GPIO2_4 | R29 | DVDD_NPU_VIP |

| B13 | GPIO0_14 | H1 | GPIO1_13 | R30 | DVDD_NPU_VIP |

| B14 | VSS | H2 | GPIO1_12 | R31 | VSS |

| B15 | AOGPIO0_27 | H3 | VSS | R34 | VSS |

| B16 | AOGPIO0_31 | H4 | CPU_JTG_TDI | R35 | VSS |

| B17 | VSS | H5 | VSS | R36 | GPIO2_5 |

| B18 | AOI2C0_SCL | H6 | CPU_JTG_TDO | R37 | VSS |

| B19 | MIPI_CSI0_A_CLKN | H7 | VSS | R38 | VSS |

| B20 | MIPI_CSI0_A_DATAP0 | H8 | VSS | R39 | GPIO2_14 |

| B21 | MIPI_CSI0_A_DATAN1 | H16 | VSS | R40 | VSS |

| B22 | MIPI_CSI1_A_CLKN | H17 | VSS | T1 | VSS |

| B23 | MIPI_CSI1_A_DATAP0 | H18 | AVDD08_MIPI | T2 | M0_A_DQ0 |

| B24 | MIPI_CSI1_A_DATAN1 | H19 | VSS | T3 | VSS |

| B25 | MIPI_DSI0_DATAP0 | H20 | MIPI_CSI0_A_REXT | T4 | M0_A_DQ4 |

| B26 | MIPI_DSI0_CLKN | H21 | AVDD08_USB3 | T5 | VSS |

| B27 | MIPI_DSI0_DATAP1 | H22 | VSS | T6 | M0_A_DQ5 |

| B28 | HDMI_TMDSDATAN2 | H23 | MIPI_CSI1_A_REXT | T7 | VSS |

| B29 | HDMI_TMDSDATAP1 | H24 | VSS | T11 | VSS |

| B30 | HDMI_TMDSDATAN0 | H25 | VSS | T12 | VSS |

| B31 | USB3_DPTX_TX3_P | H26 | AVDD18_USB3 | T13 | VSS |

| B32 | USB3_DPTXRX_TXRX2_P | H27 | VSS | T14 | DVDD08_TOP |

| B33 | USB3_DPTX_TX0_P | H28 | VSS | T15 | DVDD08_TOP |

| B34 | USB3_DPTXRX_TXRX1_M | H29 | VSS | T16 | VSS |

| B35 | USB2_2_DM | H30 | AVDD18_USB2 | T17 | VSS |

| B36 | USB2_1_DP | H31 | VSS | T18 | DVDD08_TOP |

| B37 | USB2_0_DM | H32 | DVDD08_USB2 | T19 | DVDD08_TOP |

| B38 | GPIO2_21 | H33 | VSS | T20 | VSS |

| B39 | GPIO2_19 | H34 | VSS | T21 | DVDD_GPU |

| B40 | VSS | H35 | GPIO2_31 | T22 | VSS |

| C1 | VSS | H36 | USB2_1_VBUS | T23 | VSS |

| C2 | GPIO0_6 | H37 | GPIO2_28 | T24 | VSS |

| C3 | GPIO0_4 | H38 | VSS | T25 | VSS |

| C4 | VSS | H39 | VSS | T26 | VSS |

| C5 | VSS | H40 | GPIO3_3 | T27 | VSS |

| C6 | GPIO0_9 | J1 | GPIO1_4 | T28 | VSS |

| C7 | VSS | J2 | GPIO1_2 | T29 | VSS |

| C8 | VSS | J3 | GPIO1_5 | T30 | VSS |

| C9 | GPIO0_21 | J4 | VSS | T31 | VSS |

| C10 | VSS | J5 | CPU_JTG_TCLK | T34 | VSS |

| C11 | VSS | J6 | VSS | T35 | VSS |

| C12 | GPIO0_31 | J7 | VSS | T36 | DDR0_DQ13 |

| C13 | VSS | J16 | VSS | T37 | DDR0_DQ12 |

| C14 | VSS | J17 | VSS | T38 | VSS |

| C15 | AOGPIO0_28 | J18 | VSS | T39 | DDR0_DQ15 |

| C16 | VSS | J19 | VSS | T40 | DDR0_DQ10 |

| C17 | VSS | J20 | VSS | U1 | M0_A_DQ1 |

| C18 | AOGPIO1_8 | J21 | VSS | U2 | VSS |

| C19 | VSS | J22 | AVDD08_USB3 | U3 | M0_A_DV |

| C20 | MIPI_CSI0_A_DATAN0 | J23 | VSS | U4 | VSS |

| C21 | VSS | J24 | VSS | U5 | M0_A_WCK |

| C22 | VSS | J25 | VSS | U6 | VSS |

| C23 | MIPI_CSI1_A_DATAN0 | J26 | VSS | U7 | VSS |

| C24 | VSS | J27 | VSS | U11 | VSS |

| C25 | VSS | J28 | VSS | U12 | VSS |

| C26 | MIPI_DSI0_CLKP | J29 | VSS | U13 | DVDD08_TOP |

| C27 | VSS | J30 | VSS | U14 | VSS |

| C28 | VSS | J31 | VSS | U15 | DVDD_VP |

| C29 | HDMI_TMDSDATAN1 | J32 | VSS | U16 | VSS |

| C30 | VSS | J33 | VSS | U17 | DVDD_VP |

| C31 | VSS | J34 | VSS | U18 | VSS |

| C32 | USB3_DPTXRX_TXRX2_M | J35 | VSS | U19 | DVDD08_TOP |

| C33 | VSS | J36 | GPIO2_30 | U20 | VSS |

| C34 | VSS | J37 | VSS | U21 | DVDD_GPU |

| C35 | VSS | J38 | GPIO3_9 | U22 | VSS |

| C36 | USB2_1_DM | J39 | GPIO3_6 | U23 | DVDD_NPU_VIP |

| C37 | VSS | J40 | GPIO2_29 | U24 | DVDD_NPU_VIP |

| C38 | GPIO2_17 | K1 | GPIO1_6 | U25 | DVDD_NPU_VIP |

| C39 | GPIO2_18 | K2 | VSS | U26 | DVDD_NPU_VIP |

| C40 | GPIO3_4 | K3 | VSS | U27 | DVDD_NPU_VIP |

| D1 | RTC_CLK_OUT | K4 | CPU_JTG_TMS | U28 | DVDD_NPU_VIP |

| D2 | RTC_CLK_IN | K5 | CPU_JTG_TRST | U29 | DVDD_NPU_VIP |

| D3 | VSS | K6 | GPIO1_14 | U30 | DVDD_NPU_VIP |

| D4 | TEST_MODE | K7 | VSS | U31 | VSS |

| D5 | DEBUG_MODE | K19 | VSS | U34 | VSS |

| D6 | VSS | K20 | VSS | U35 | DDR0_DQSTU |

| D7 | BOOT_SEL0 | K21 | VSS | U36 | DDR0_DQSCU |

| D8 | GPIO0_16 | K22 | VSS | U37 | DDR0_DMU |

| D9 | VSS | K23 | VSS | U38 | VSS |

| D10 | BOOT_SEL1 | K24 | VSS | U39 | VSS |

| D11 | GPIO0_27 | K25 | VSS | U40 | DDR0_DQ14 |

| D12 | VSS | K33 | VSS | V1 | VSS |

| D13 | GPIO0_26 | K34 | VSS | V2 | M0_A_DQ2 |

| D14 | RST_N_IN | K35 | GPIO2_25 | V3 | VSS |

| D15 | VSS | K36 | VSS | V4 | M0_A_DQ6 |

| D16 | GPIO0_17 | K37 | GPIO2_12 | V5 | VSS |

| D17 | AOGPIO1_4 | K38 | VSS | V6 | M0_A_WCKB |

| D18 | VSS | K39 | GPIO3_5 | V7 | VSS |

| D19 | VSS | K40 | GPIO3_7 | V11 | VSS |

| D20 | VSS | L1 | GPIO1_7 | V12 | VSS |

| D21 | MIPI_CSI0_B_CLKP | L2 | GPIO1_8 | V13 | DVDD_VP |

| D22 | VSS | L3 | VSS | V14 | VSS |

| D23 | VSS | L4 | AOGPIO0_21 | V15 | DVDD_VP |

| D24 | MIPI_CSI1_B_CLKP | L5 | VSS | V16 | VSS |

| D25 | VSS | L6 | GPIO1_15 | V17 | DVDD_VP |

| D26 | VSS | L7 | VSS | V18 | VSS |

| D27 | MIPI_DSI0_DATAN3 | L34 | VSS | V19 | DVDD08_TOP |

| D28 | VSS | L35 | GPIO2_26 | V20 | VSS |

| D29 | VSS | L36 | GPIO2_16 | V21 | DVDD_GPU |

| D30 | HDMI_REXT | L37 | GPIO2_15 | V22 | VSS |

| D31 | VSS | L38 | VSS | V23 | DVDD_GPU |

| D32 | VSS | L39 | VSS | V24 | VSS |

| D33 | USB3_DPTX_REFCLK_M | L40 | GPIO3_2 | V25 | VSS |

| D34 | VSS | M1 | VSS | V26 | VSS |

| D35 | USB2_2_TXRTUNE | M2 | M0_B_DQ3 | V27 | VSS |

| D36 | VSS | M3 | VSS | V28 | VSS |

| D37 | USB2_0_TXRTUNE | M4 | M0_B_DQ6 | V29 | VSS |

| D38 | VSS | M5 | VSS | V30 | VSS |

| D39 | GPIO2_2 | M6 | M0_B_DQ7 | V31 | VSS |

| D40 | GPIO3_10 | M7 | VSS | V34 | VSS |

| E1 | OSC_CLK_IN | M13 | VSS | V35 | VSS |

| E2 | OSC_CLK_OUT | M14 | VSS | V36 | VSS |

| E3 | GPIO1_3 | M15 | VSS | V37 | VSS |

| E4 | VSS | M16 | VSS | V38 | DDR0_DQ8 |

| E5 | AOGPIO0_22 | M17 | VSS | V39 | DDR0_DQ11 |

| E6 | POR_SEL | M18 | VSS | V40 | DDR0_DQ9 |

| E7 | VSS | M19 | VSS | W1 | M0_A_DQ3 |

| E8 | GPIO0_24 | M20 | VSS | W2 | VSS |

| E9 | GPIO0_15 | M21 | VSS | W3 | M0_A_DX |

| E10 | VSS | M22 | VSS | W4 | VSS |

| E11 | AOI2C1_SCL | M23 | VSS | W5 | M0_A_DQ7 |

| E12 | AOGPIO1_5 | M24 | VSS | W6 | VSS |

| E13 | VSS | M25 | VSS | W7 | VSS |

| E14 | AOGPIO1_6 | M26 | AVDD18_PERI2 | W11 | VSS |

| E15 | AOGPIO0_25 | M27 | VSS | W12 | AVDD18_PERI1 |

| E16 | VSS | M28 | VSS | W13 | DVDD_VP |

| E17 | AOGPIO1_3 | M29 | VSS | W14 | VSS |

| E18 | AOI2C0_SDA | M30 | VSS | W15 | DVDD_VP |

| E19 | VSS | M34 | VSS | W16 | VSS |

| E20 | MIPI_CSI0_B_DATAP0 | M35 | VSS | W17 | DVDD_VP |

| E21 | MIPI_CSI0_B_CLKN | M36 | GPIO2_10 | W18 | VSS |

| E22 | VSS | M37 | VSS | W19 | DVDD08_TOP |

| E23 | MIPI_CSI1_B_DATAP0 | M38 | GPIO2_13 | W20 | VSS |

| E24 | MIPI_CSI1_B_CLKN | M39 | GPIO3_8 | W21 | DVDD_GPU |

| E25 | VSS | M40 | GPIO2_27 | W22 | VSS |

| E26 | MIPI_DSI0_DATAN2 | N1 | M0_B_DQ2 | W23 | DVDD_GPU |

| E27 | MIPI_DSI0_DATAP3 | N2 | VSS | W24 | DVDD_NPU |

| E28 | VSS | N3 | M0_B_DX | W25 | DVDD_NPU |

| E29 | HDMI_TMDSCLKP | N4 | VSS | W26 | DVDD_NPU |

| E30 | VSS | N5 | M0_B_WCKB | W27 | DVDD_NPU |

| E31 | VSS | N6 | VSS | W28 | DVDD_NPU |

| E32 | USB3_DPTX_RESREF | N7 | VSS | W29 | DVDD_NPU |

| E33 | USB3_DPTX_REFCLK_P | N12 | VSS | W30 | DVDD_NPU |

| E34 | VSS | N13 | AVDD18_AON | W31 | VSS |

| E35 | USB2_2_ID | N14 | VSS | W34 | VSS |

| E36 | USB2_1_TXRTUNE | N15 | VSS | W35 | VSS |

| E37 | USB2_0_ID | N16 | VSS | W36 | VSS |

| E38 | VSS | N17 | VSS | W37 | DDR0_DML |

| E39 | VSS | N18 | VSS | W38 | VSS |

| E40 | GPIO3_0 | N19 | VSS | W39 | DDR0_DQ3 |

| F1 | GPIO1_9 | N20 | VSS | W40 | DDR0_DQ2 |

| F2 | GPIO1_10 | N21 | DVDD_GPU | Y1 | VSS |

| F3 | VSS | N22 | VSS | Y2 | M1_A_SBCK |

| F4 | GPIO0_13 | N23 | VSS | Y3 | VSS |

| F5 | GPIO0_12 | N24 | VSS | Y4 | M0_A_SBCK |

| F6 | VSS | N25 | VSS | Y5 | VSS |

| F7 | AOGPIO0_24 | N26 | VSS | Y6 | D2D_RZQ |

| F8 | AOGPIO1_0 | N27 | VSS | Y7 | VSS |

| F9 | GPIO0_25 | N28 | VSS | Y11 | VSS |

| F10 | RST_N_OUT | N29 | DVDD_NPU_VIP | Y12 | VSS |

| F11 | AOI2C1_SDA | N30 | DVDD_NPU_VIP | Y13 | DVDD_VP |

| F12 | VSS | N31 | VSS | Y14 | VSS |

| F13 | GPIO1_16 | N34 | VSS | Y15 | DVDD_VP |

| F14 | MULTI_DIE_PACKAGE | N35 | GPIO2_11 | Y16 | VSS |

| F15 | VSS | N36 | VSS | Y17 | DVDD08_TOP |

| F16 | AOGPIO0_30 | N37 | GPIO2_8 | Y18 | DVDD08_TOP |

| F17 | AOGPIO1_2 | N38 | VSS | Y19 | DVDD08_TOP |

| F18 | VSS | N39 | GPIO2_24 | Y20 | DVDD08_TOP |

| F19 | MIPI_CSI0_B_DATAP1 | N40 | GPIO2_23 | Y21 | DVDD08_TOP |

| F20 | MIPI_CSI0_B_DATAN0 | P1 | VSS | Y22 | DVDD08_TOP |

| F21 | VSS | P2 | M0_B_DQ1 | Y23 | DVDD08_TOP |

| F22 | MIPI_CSI1_B_DATAP1 | P3 | VSS | Y24 | VSS |

| F23 | MIPI_CSI1_B_DATAN0 | P4 | M0_B_DQ4 | Y25 | VSS |

| F24 | VSS | P5 | VSS | Y26 | VSS |

| F25 | VSS | P6 | M0_B_WCK | Y27 | VSS |

| F26 | MIPI_DSI0_DATAP2 | P7 | VSS | Y28 | VSS |

| F27 | VSS | P11 | VSS | Y29 | VSS |

| F28 | VSS | P12 | AVDD18_AON | Y30 | VSS |

| F29 | HDMI_TMDSCLKN | P13 | DVDD08_AON | Y31 | VSS |

| F30 | VSS | P14 | DVDD08_TOP | Y32 | VSS |

| F31 | VSS | P15 | DVDD08_TOP | Y34 | VSS |

| F32 | DPTX_AUX_N | P16 | VSS | Y35 | DDR0_DQSTL |

| F33 | VSS | P17 | VSS | Y36 | DDR0_DQSCL |

| F34 | VSS | P18 | DVDD08_TOP | Y37 | DDR0_DQ6 |

| F35 | VSS | P19 | DVDD08_TOP | Y38 | VSS |

| F36 | USB2_1_ID | P20 | VSS | Y39 | VSS |

| F37 | VSS | P21 | DVDD_GPU | Y40 | DDR0_DQ0 |

| F38 | GPIO2_3 | P22 | VSS |

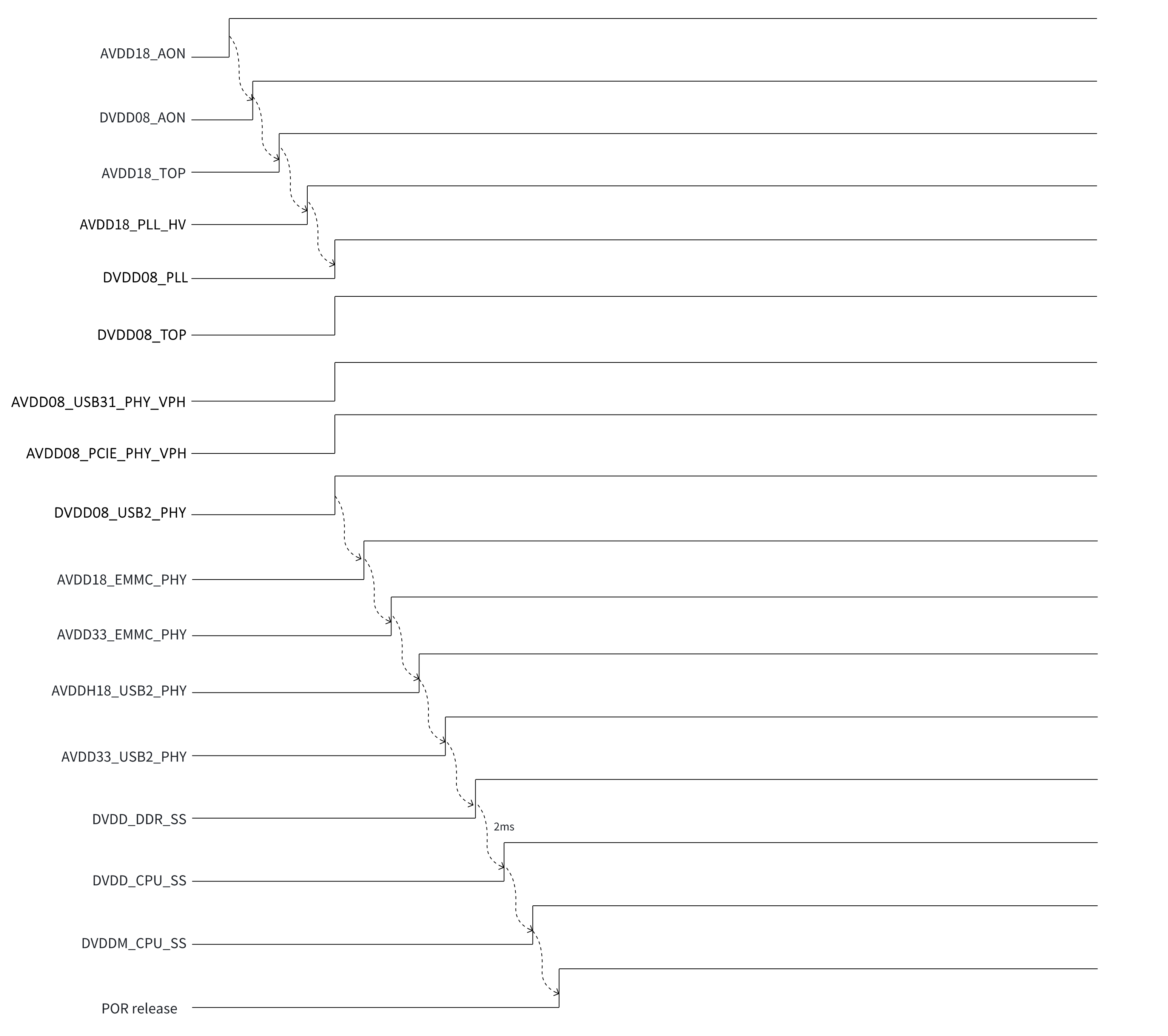

Power On/Off Sequence

Power On Sequence

The parameters in the table below represent the time required for the pins to enable the power supply in sequence.

| Parameter (Power on Time Interval) | Typical | Unit |

|---|---|---|

| AVDD18_AON | 1000 | ms |

| AVDD18_AON to DVDD08_AON | 2 | ms |

| DVDD08_AON to AVDD18_TOP | 2 | ms |

| AVDD18_TOP to AVDD18_PLL_HV | 2 | ms |

| AVDD18_PLL_HV to DVDD08_PLL | 2 | ms |

| DVDD08_USB2_PHY to AVDD18_EMMC_PHY | 2 | ms |

| AVDD18_EMMC_PHY to AVDD33_EMMC_PHY | 2 | ms |

| AVDD33_EMMC_PHY to AVDDH18_USB2_PHY | 2 | ms |

| AVDDH18_USB2_PHY to AVDD33_USB2_PHY | 2 | ms |

| AVDD33_USB2_PHY to DVDD_DDR_SS | 2 | ms |

| DVDD_DDR_SS to DVDD_CPU_SS | 2 | ms |

| DVDD_CPU_SS to DVDDM_CPU_SS | 2 | ms |

| DVDDM_CPU_SS to POR release | 2 | ms |

| POR release | 6 | ms |

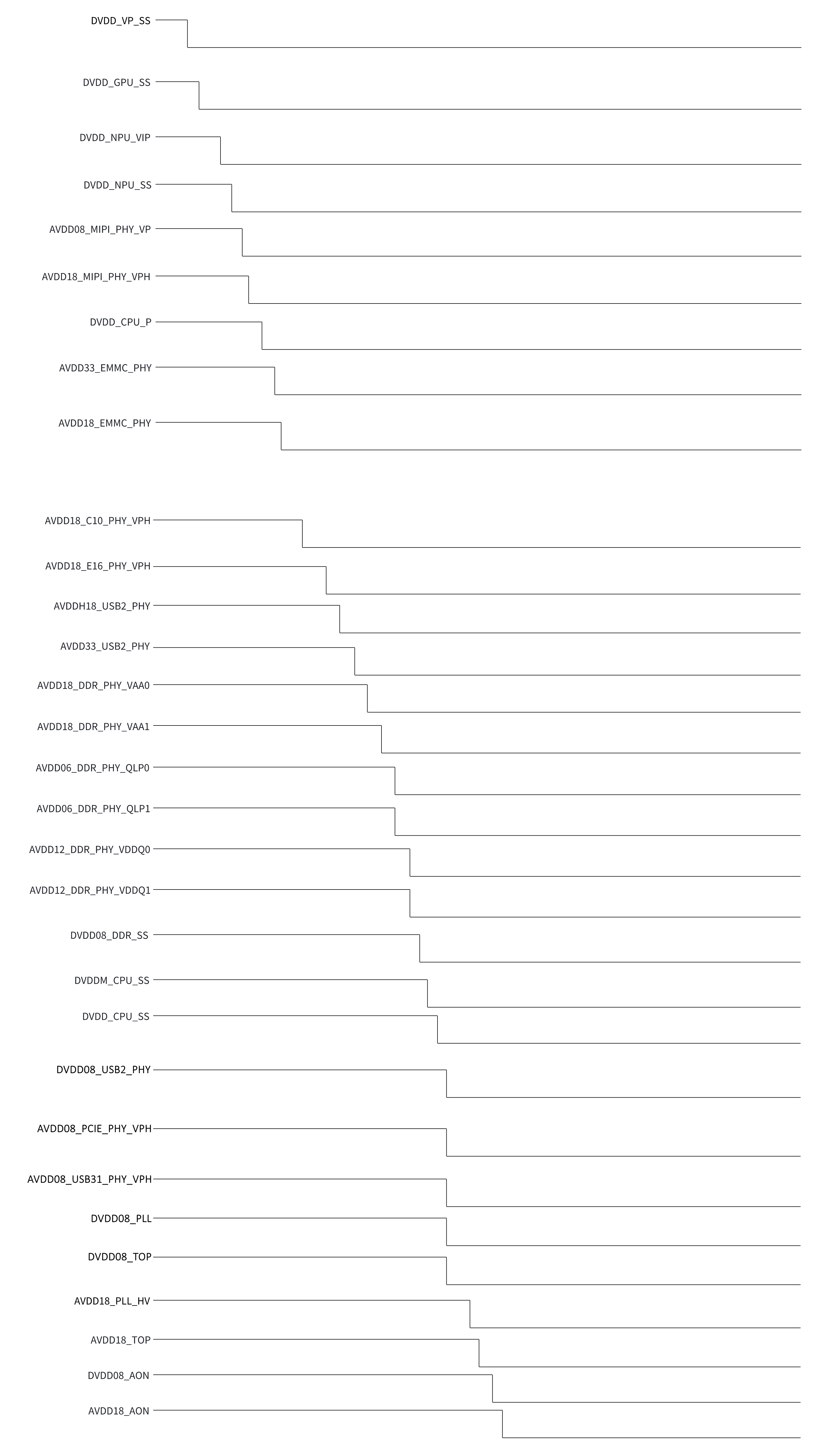

Power Off Sequence

The parameters in the table below represent the time required for the pins to cut off the power supply in sequence.

| Parameter (Power Down Time Interval) | Typical | Unit |

|---|---|---|

| DVDD_VP_SS to DVDD_GPU_SS | 2 | ms |

| DVDD_GPU_SS to DVDD_NPU_VIP | 2 | ms |

| DVDD_NPU_VIP to DVDD_NPU_SS | 2 | ms |

| DVDD_NPU_SS to AVDD08_MIPI_PHY_VP | 2 | ms |

| AVDD08_MIPI_PHY_VP to AVDD18_MIPI_PHY_VPH | 2 | ms |

| AVDD18_MIPI_PHY_VPH to DVDD_CPU_P | 2 | ms |

| DVDD_CPU_P to AVDD33_EMMC_PHY | 2 | ms |

| AVDD33_EMMC_PHY to AVDD18_EMMC_PHY | 2 | ms |

| AVDD18_EMMC_PHY to AVDD18_C10_PHY_VPH | 2 | ms |

| AVDD18_C10_PHY_VPH to AVDD18_E16_PHY_VPH | 2 | ms |

| AVDD18_E16_PHY_VPH to AVDDH18_USB2_PHY | 2 | ms |

| AVDDH18_USB2_PHY to AVDD33_USB2_PHY | 2 | ms |

| AVDD33_USB2_PHY to AVDD18_DDR_PHY_VAA0 | 2 | ms |

| AVDD18_DDR_PHY_VAA0 to AVDD18_DDR_PHY_VAA1 | 2 | ms |

| AVDD18_DDR_PHY_VAA1 to AVDD06_DDR_PHY_QLP0 | 2 | ms |

| AVDD06_DDR_PHY_QLP0 to AVDD06_DDR_PHY_QLP1 | 2 | ms |

| AVDD06_DDR_PHY_QLP1 to AVDD12_DDR_PHY_VDDQ0 | 2 | ms |

| AVDD12_DDR_PHY_VDDQ0 to AVDD12_DDR_PHY_VDDQ1 | 2 | ms |

| AVDD12_DDR_PHY_VDDQ1 to DVDD08_DDR_SS | 2 | ms |

| DVDD08_DDR_SS to DVDDM_CPU_SS | 2 | ms |

| DVDDM_CPU_SS to DVDD_CPU_SS | 2 | ms |

| DVDD_CPU_SS to DVDD08_USB2_PHY | 2 | ms |

| DVDD08_TOP to AVDD18_PLL_HV | 2 | ms |

| AVDD18_PLL_HV to AVDD18_TOP | 2 | ms |

| AVDD18_TOP to DVDD08_AON | 2 | ms |

| DVDD08_AON to AVDD18_AON | 2 | ms |

| AVDD18_AON | 2 | ms |