原理图设计建议

最小系统设计

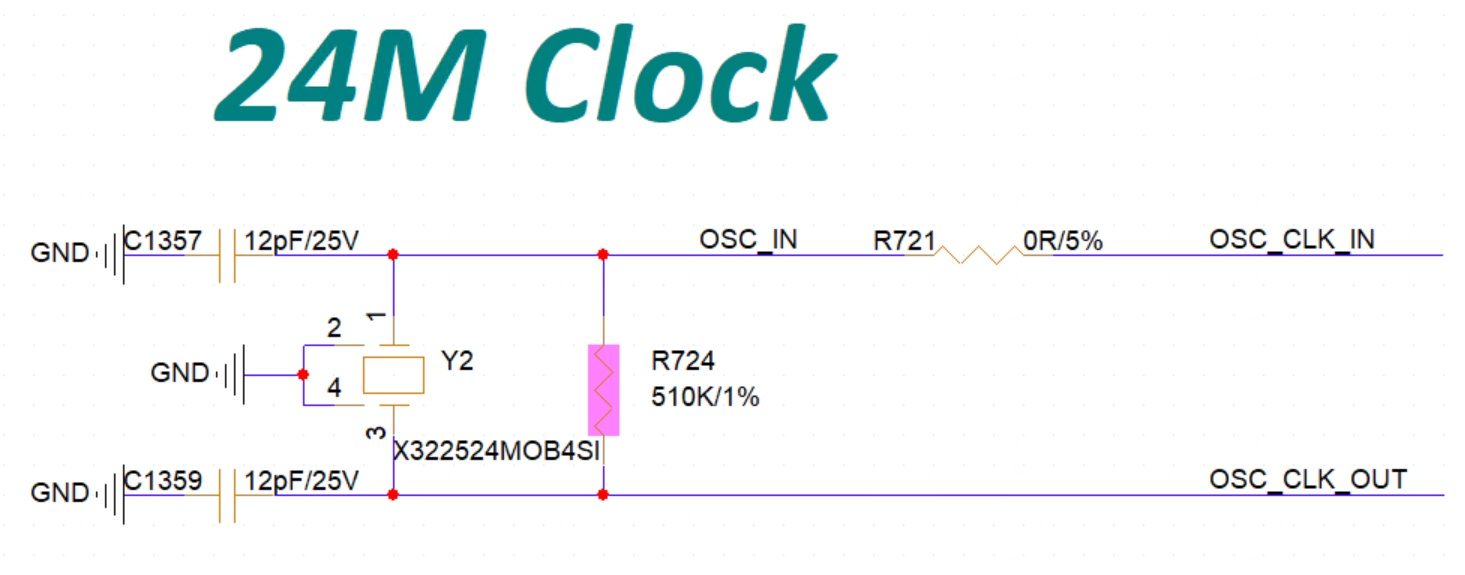

时钟电路

系统时钟

A210芯片内部的振荡器电路与外置的 24MHz 晶体一起构成系统时钟,如下图所示。OSC_CLK_IN 和 OSC_CLK_OUT 网络之间预留 510Kohm, 1% Feedback 电阻,默认不焊接。

说明

- 选用晶体的激励功率值不超过 100uW,ESR 小于 80ohm。

- 晶体负载电容请根据实际使用的晶体的 CL 电容值选择,并控制常温下的频率容限在 30ppm 以内。

- 12pF 为我司选用晶体所对应容值,并不为通用值,负载电容材质建议采用 C0G 或 NP0。

- 建议采用贴片 4Pin 晶体,其中 2 个 GND 管脚与 PCB 板的地充分连接,加强时钟抗 ESD 干扰能力。

系统时钟还可以直接由外部的有源晶体电路产生时钟,时钟幅度为 1.8V。工作情况下,时钟通过 OSC_CLK_IN 脚输入,OSC_CLK_OUT 管脚悬空。时钟参数如下表所示。

| 参数 | 规范 | 描述 | ||

|---|---|---|---|---|

| 最小 | 最大 | 单位 | ||

| 频率 | 24.000000 | MHz | ||

| 频偏 | ±30 | ppm | ||

| 时钟幅度 | 1.8 | V | 峰峰值 | |

| 工作温度 | -20 | 80 | ℃ | |

| ESR | / | 80 | Ohm | |

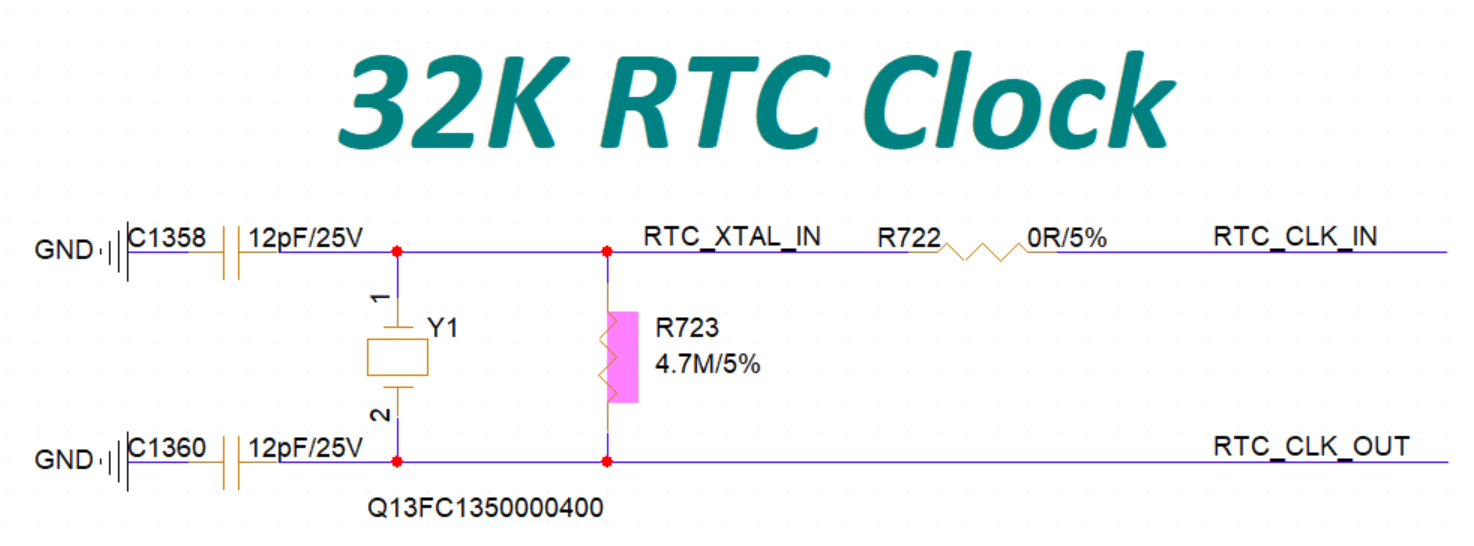

RTC 时钟

A210 芯片内部的振荡器电路与外置的 32.768KHz 晶体一起构成 RTC 时钟,如下图所示。RTC_CLK_IN 和 RTC_CLK_OUT 网络之间预留 4.7Mohm 电阻,默认不焊接。

说明:

- 选用晶体的激励功率值不超过 1uW,ESR小于 70Kohm。

- 晶体负载电容请根据实际使用的晶体的 CL 电容值选择,并控制常温下的频率容限在 30ppm 以内。

- 12pF 为我司选用晶体所对应容值,并不为通用值,负载电容材质建议采用 C0G 或 NP0。

RTC时钟还可以直接由外部时钟源输入,时钟幅度为 0.8V。工作情况下,时钟通过 RTC_CLK_IN 脚输入,RTC_CLK_OUT 管脚悬空,时钟参数如下表所示。

| 参数 | 规范 | 描述 | ||

|---|---|---|---|---|

| 最小 | 最大 | 单位 | ||

| 频率 | 32.768000 | KHz | ||

| 频偏 | ±30 | ppm | ||

| 时钟幅度 | 0.8 | V | 峰峰值 | |

| 占空比 | 45 | 55 | % | |

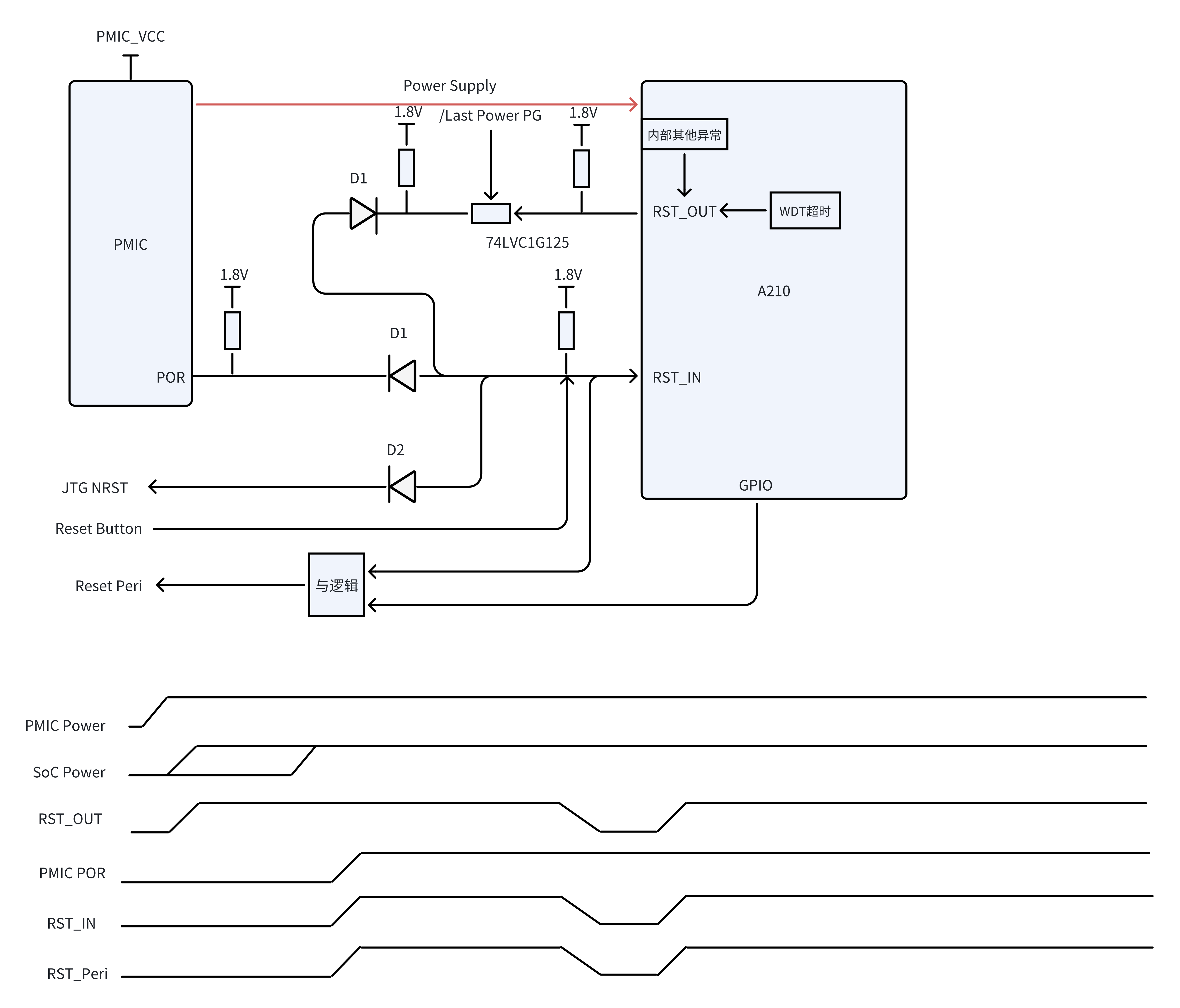

复位/看门狗

A210 复位相关主要涉及复位选择管脚 POR_SEL(Pin E6),复位输入管脚 RST_N_IN(Pin D14)和 Watchdog 输出管脚 RST_N_OUT(Pin F10),其功能描述如下表所示。

| 管脚 | 名称 | 功能 | 说明 |

|---|---|---|---|

| E6 | POR_SEL | 内外部复位选择 | 在上电时的状态选择内部复位或外部复位。

|

| D14 | RST_N_IN | 复位输入 | 芯片内部将 RST_N_IN 与内部 POR 进行与操作后,再用来复位 SOC,因此 RST_N_IN 任何时候都可以控制 A210 复位。POR 的复位时间由 CPU_JTG_TDO 的上下拉来确定。

|

| F10 | RST_N_OUT | Watchdog 输出 | 该信号可以通过逻辑电路连接到 PMIC 的复位输入端或者开关机输入端,控制 PMIC 下电然后再上电。 常态输出高电平。当 A210 在 DVS 调节时内部出现异常或者内部 WDT 超时时,该信号拉低,此时整个芯片复位,需要 PMIC 将电源电压全部恢复到 boot 电压,并且重新复位 A210。 |

A210 的系统复位电路设计如下。

-

若 RST_N_OUT 有效时,若不考虑复位 PMIC 重新上电,则复位电路建议如下。

当 Reset Button、PMIC POR、JTG NRST 和 RST_N_OUT 拉低都会复位 SoC 和外设,当然 A210 也可以通过 IO 来单独控制外设复位。

-

若 RST_N_OUT 有效时需要复位 PMIC 重新上电。当 PMIC 有单独的复位输入管脚,则复位电路建议和上电/异常复位时序如下。

BOOT 设置

A210 的启动通过管脚 BOOT_SEL[2:0] 进行设置。

对应设置如下表所示。表中 1 为 4.7K 电阻上拉,0 为 1K 电阻下拉。

| BOOT_SEL[2] | BOOT_SEL[1] | BOOT_SEL[0] | BOOT MODE |

|---|---|---|---|

| 0 | 0 | 0 | USB Fastboot(先检测 CCTboot,超时 1s 则自动进入 USB Fastboot) |

| 0 | 0 | 1 | eMMC, 8 bit default |

| 0 | 1 | 0 | QSPI1 NOR Flash Boot, CS0 |

| 0 | 1 | 1 | QSPI1 NAND Flash Boot,CS0 |

| 1 | 0 | 0 | 强制 CCTBoot |

| 1 | 0 | 1 | SD Card Boot, SDIO0 |

| 1 | 1 | 0 | QSPI0 NOR Flash, CS0 |

| 1 | 1 | 1 | QSPI0 NAND Flash, CS0 |

系统初始化配置信号

A210 中有一些 STRAP 信号会影响系统的启动配置。SOC 内部复位信号是 RST_IN 和内部 POR 信号相与之后的输出,释放后大约 4ms 会去采样 STRAP 管脚的状态。因此在 RST_IN 释放前后的 10ms 内, STRAP 管脚的电平需要保持为稳定状态。

STRAP 管脚的信号可以使用上下拉电阻进行配置,其中上拉建议为 4.7K,下拉建议为 1K,所有 STRAP 信号上拉电源为 AVDD18_AON。

TEST_MODE 设计

TEST_MODE 管脚,用于 Test mode 选择。

具体说明及设计建议见下表。

| 信号 | 功能说明 | 设计建议 |

|---|---|---|

| TEST_MODE | TEST Mode选择管脚。0:Normal mode,1:Test mode。 | 下拉,默认功能模式 |

POR_SEL 设计

POR_SEL 管脚,用于内外部复位选择。

具体说明及设计建议见下表。

| 信号 | 功能说明 | 设计建议 |

|---|---|---|

| POR_SEL | 复位选择管脚。0:使用外部复位,1:使能内部复位。 | 预留电阻上拉但不上件,芯片内部默认下拉,默认关闭内部 POR。 |

DEBUG_MODE 设计

DEBUG_MODE 管脚,用于 debug mode 选择。

![]()

具体说明及设计建议见下表。

| 信号 | 功能说明 | 设计建议 |

|---|---|---|

| DEBUG_MODE | DEBUG Mode选择管脚。0:Normal mode,1:Debug mode。 | 下拉,默认为 Normal Mode。 |

MCM_EN & MCM_CHIP_ID 设计

MCM_EN 管脚,用于指示是单 DIE CHIP 还是多 DIE CHIP。

![]()

MCM_CHIP_ID[1:0] 管脚,用于 CHIP ID 识别。

具体说明及设计建议见下表。

| 信号 | 功能说明 | 设计建议 |

|---|---|---|

| MCM_EN | 用于指示是单 DIE CHIP还是多 DIE CHIP。 Bootrom 会根据该信号的不同电平执行不同的启动流程,对于单 DIE CHIP 设计,将该信号拉低,也可以通过软件配置使能单 DIE CHIP 的 D2D 功能。 | 单 Die 默认下拉,多 Die 上拉。 |

| MCM_CHIP_ID[1:0] | 多 Die CHIP 情况下用于表示 Chip ID 。 | 根据各芯片的 CHIP ID 号分别使用上下拉电阻。 |

注意:

在多 Die Chip 情况下,如下 IO 功能将被固定,无法修改。

GPIO 固定功能(多 Die 中不可配置) AOGPIO1_0 MCM_CHIP_ID0 AOGPIO1_1 MCM_TIM_TICK AOGPIO1_6 AO12C2_SCL AOGPIO1_7 AO12C2_SDA AOGPIO1_9 MCM_CHIP_ID1 GPIO0_14 OCD_RESP1 GPIO0_15 OCD_RESP2 GPIO0_16 OCD_RESP3 GPIO0_17 OCD_CMD GPIO1_16 OCD_CLK

PCIEX4_TYPE设计

PCIEX4_TYPE 管脚,用于 PCIE 模式选择。

![]()

具体说明及设计建议见下表。

| 信号 | 功能说明 | 设计建议 |

|---|---|---|

| PCIEX4_TYPE | PCIE TYPE 选择。0:EP,1:RC。 | 根据需求选择。 |

CPU_JTG_TDO设计

CPU_JTG_TDO 管脚,上电时用于内部 POR 复位时间选择。

![]()

具体说明及设计建议见下表。

| 信号 | 功能说明 | 设计建议 |

|---|---|---|

| CPU_JTG_TDO | 复位时间选择。0:20ms,1:80ms。 | 预留上拉电阻但不上件。芯片内部默认下拉,默认 20ms。 |

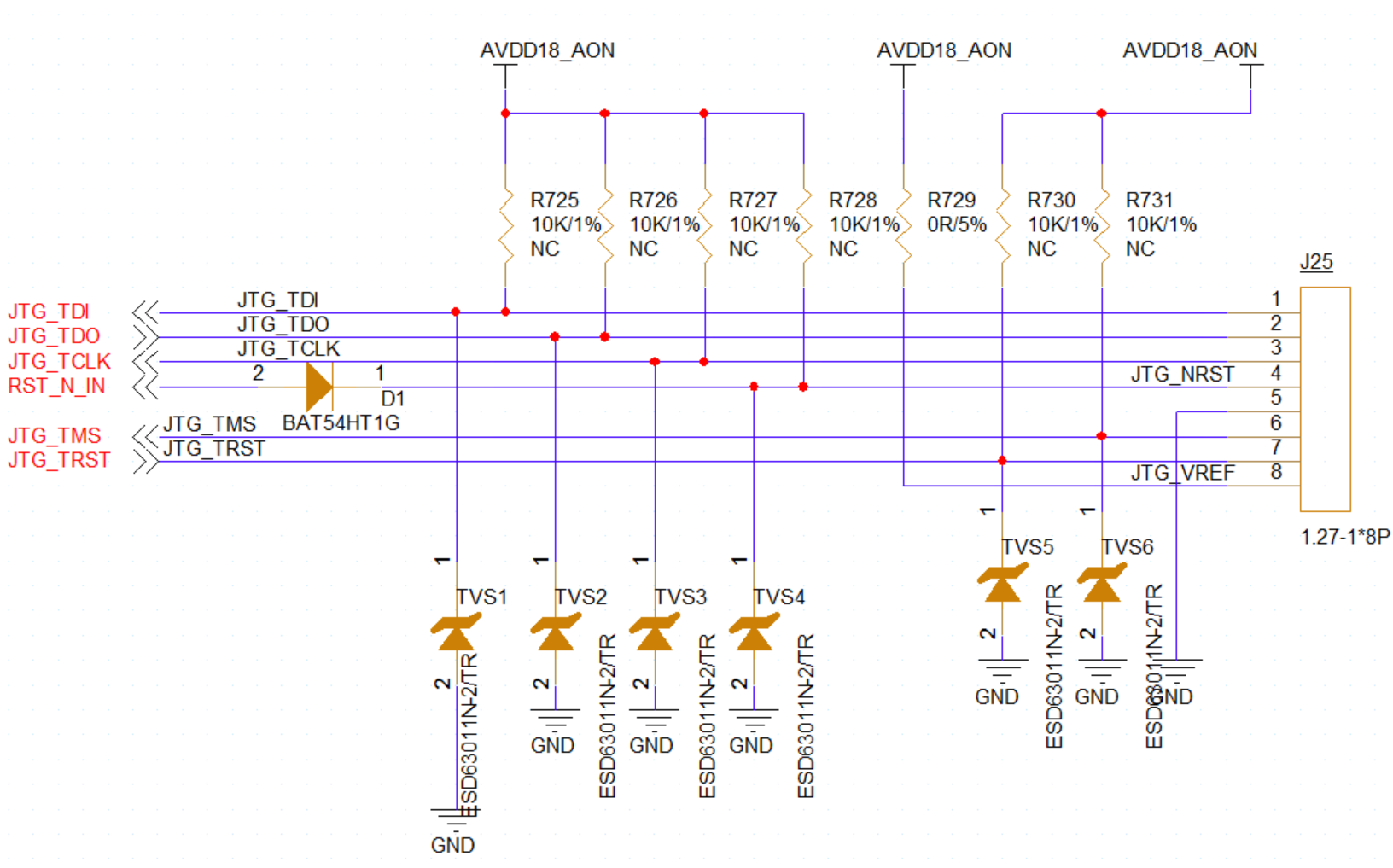

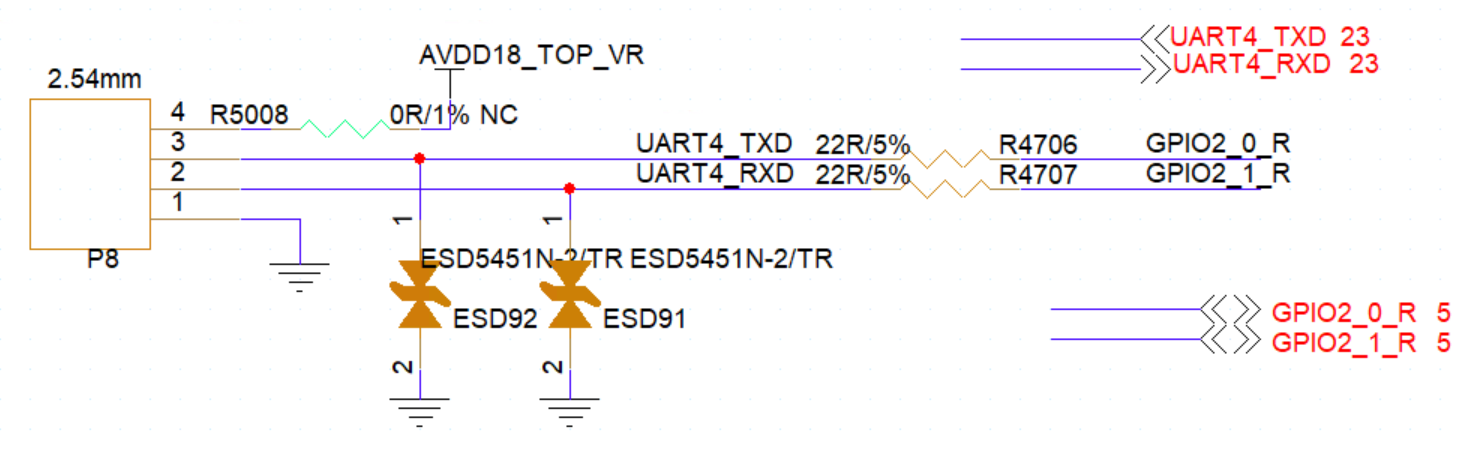

JTAG 和 UART Debug 电路

A210 芯片可以通过仿真器访问 CPU core。实际设计中建议预留 JTAG 电路,方便调试。预留电路参考如下。

JTAG设�计注意点见下表。

| 序号 | 推荐设计 | 备注 |

|---|---|---|

| 1 | E902,C908, C920 共用一个 CPU JTAG 调试接口。 | CPU JTAG IO 属于 AVDD18_AON 电源域。 |

| 2 | CPU JTAG 接口 TCLK,预留 10K 上拉,默认不上件。 | |

| 3 | CPU JTAG 接口 TMS,预留 10K 上拉,默认不上件。 | |

| 4 | CPU JTAG 接口 TDI,预留 10K 上拉,默认不上件。 | |

| 5 | CPU JTAG 接口 TDO,芯片内部已下拉,外部预留上拉电阻,默认不上件。 | |

| 6 | CPU JTAG 接口 TRST,芯片内部上拉,预留 10K 上拉,默认不上件。 | |

| 7 | 用于复位系统,可以通过二极管连接到系统复位输入端。 | |

| 8 | JTAG 调试接口 VREF 电源,电压值为 1.8V,预留 0 欧姆电阻位置,如果有漏电现象,则将其换成肖特基二极管,或者大阻值电阻。 | |

| 9 | 所有 JTAG 信号连接器附近需要放置 ESD 器件。 |

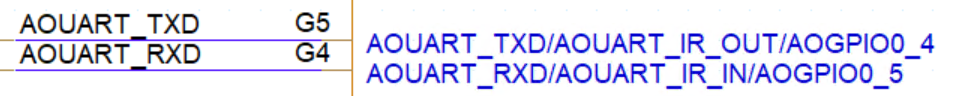

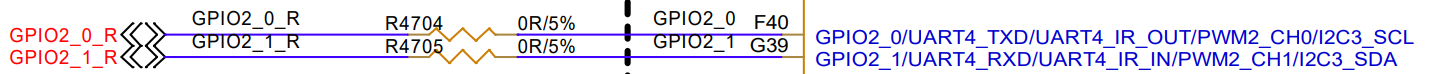

A210 的 UART debug 主要分为 E902 调试串口和 C908/C920 串口,E902 使用 AOUART,C908/C920 使用 UART4。

UART 接口增加 TVS 管,加强抗静电浪涌能力,防止开发过程损坏芯片管脚,实际设计中,尽量预留 2.54 插针金接口。如果无条件,建议使用 0.7mm 以上测试点,方便焊接。

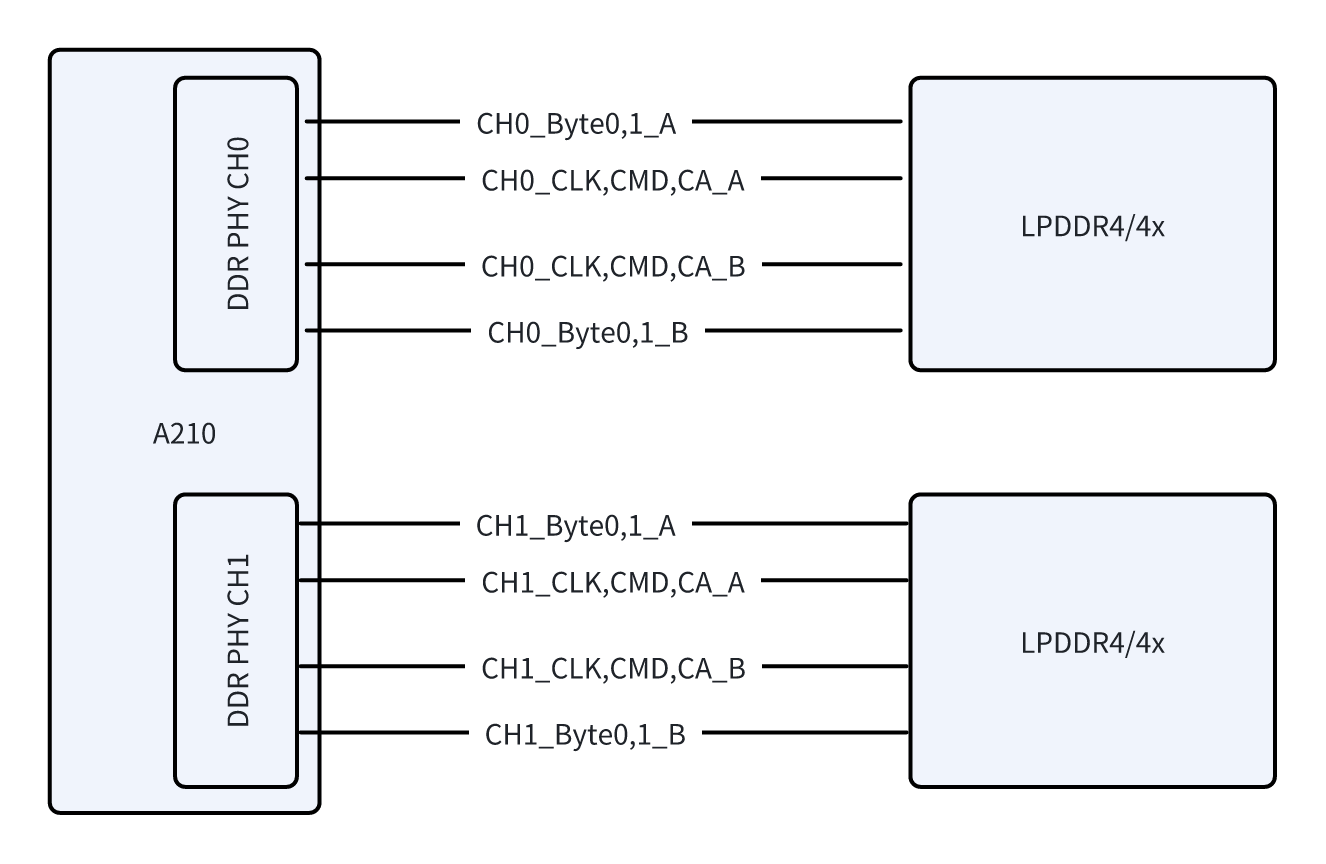

DDR 电路

DDR 控制器介绍

A210 DDR 控制器接口支持 JEDEC SDRAM 标准接口,控制器特点如下。

- 兼容 LPDDR4/LPDDR4X 标准。

- 最大支持 2Rank。

- 支持 2 通道,每通道支持 32bit。

- 支持 DDR4 3200Mbps。

- LPDDR4/4x 最大速率支持 4266Mbps。

- 支持 ECC。

- DDR4 最大支持 16GB 容量。

- LPDDR4/4x 最大支持 16GB 容量。

- 不支持 UDIMM。

电路设计建议

A210 DDR PHY 和各 DRAM 颗粒原理图需要和参考设计图一致,包含电源去耦电容。A210 可支持 DDR4/LPDDR4/4X,这些 DRAM 具有不同 I/O 信号,根据 DRAM 类型选择对应的信号。请参考对应的 DRAM 参考设计图。

设计时需注意。

- DQ,CA 顺序按参考原理图上分配,走线直接参考 ZH 提供的 Demo,不允许做修改。

- DDR PHY ZQ 必须接 240ohm 1% 到 DVDD06_DDR_VDDQLP 电源上。

DDR 颗粒外围电路设计

- LPDDR4/4x 的颗粒 ZQ 必须接 240ohm 1% 到 DVDD06_DDR_VDDQLP 电源上。

- LPDDR4/4x 的颗粒 ODT_CA 必须接 10Kohm 5% 到 DVDD11_DDR_VDDQ 电源上。

DDR 拓扑结构与匹配方式设计

-

LPDDR4/4x 2 颗 32bit 时,DQ/CA 采用点对点拓扑结构。

-

LPDDR4/4x DDR 1 颗 32bit 时,仅连接 DDR PHY CH0。

DDR 电源设计和要求

A210 DDR PHY 供电电源汇总如下。

| DDR PHY POWER | Min(V) | Typ(V) | Max(V) | |

|---|---|---|---|---|

| DDR PLL POWER | DVDD08_PLL | 0.72 | 0.8 | 0.96 |

| AVDD18_PLL | 1.62 | 1.8 | 1.98 | |

| DDR_PHY | DVDD_DDR | 0.74 | 0.8 | 0.88 |

| AVDD12_DDR_VDDQ_0 | 1.14/1.06 | 1.2/1.1 | 1.26/1.17 | |

| AVDD06_DDR_VDDQLP_0 | 0.57 | 0.6 | 0.65 | |

| AVDD18_DDR_VAA_0 | 1.67 | 1.8 | 1.98 | |

| AVDD12_DDR_VDDQ_1 | 1.14/1.06 | 1.2/1.1 | 1.26/1.17 | |

| AVDD06_DDR_VDDQLP_1 | 0.57 | 0.6 | 0.65 | |

| AVDD18_DDR_VAA_1 | 1.67 | 1.8 | 1.98 |

LPDDR4/4x 颗粒供电电源汇总如下。

| DDR 颗粒 POWER | LPDDR4 | LPDDR4x | |

|---|---|---|---|

| Core power 1 | VDD1 | 1.8 | 1.8 |

| Core power 2 | VDD2 | 1.1 | 1.1 |

| IO Buffer Power | VDDQ | 1.1 | 0.6 |

说明:

以上表格中电压值均为 Typ 值。

eMMC 电路

eMMC 控制器介绍

A210 提供 1 个 eMMC 控制器,具有如下特点。

- 兼容 5.1/5.0 规范。

- 支持 1bit、4bit、8bit 三种数据总线宽度。

- 支持 HS400 模式,向下兼容 HS200、DDR52 等模式。

支持从对应 eMMC Boot通过 BOOT_SEL[2:0] 进行设置,见下表。

| BOOT_SEL[2] | BOOT_SEL[1] | BOOT_SEL[0] | BOOT MODE |

|---|---|---|---|

| 0 | 0 | 1 | eMMC, 8 bit default |

eMMC 电路设计建议

eMMC 信号接法请按参考原理图,包含各路电源去耦电容。

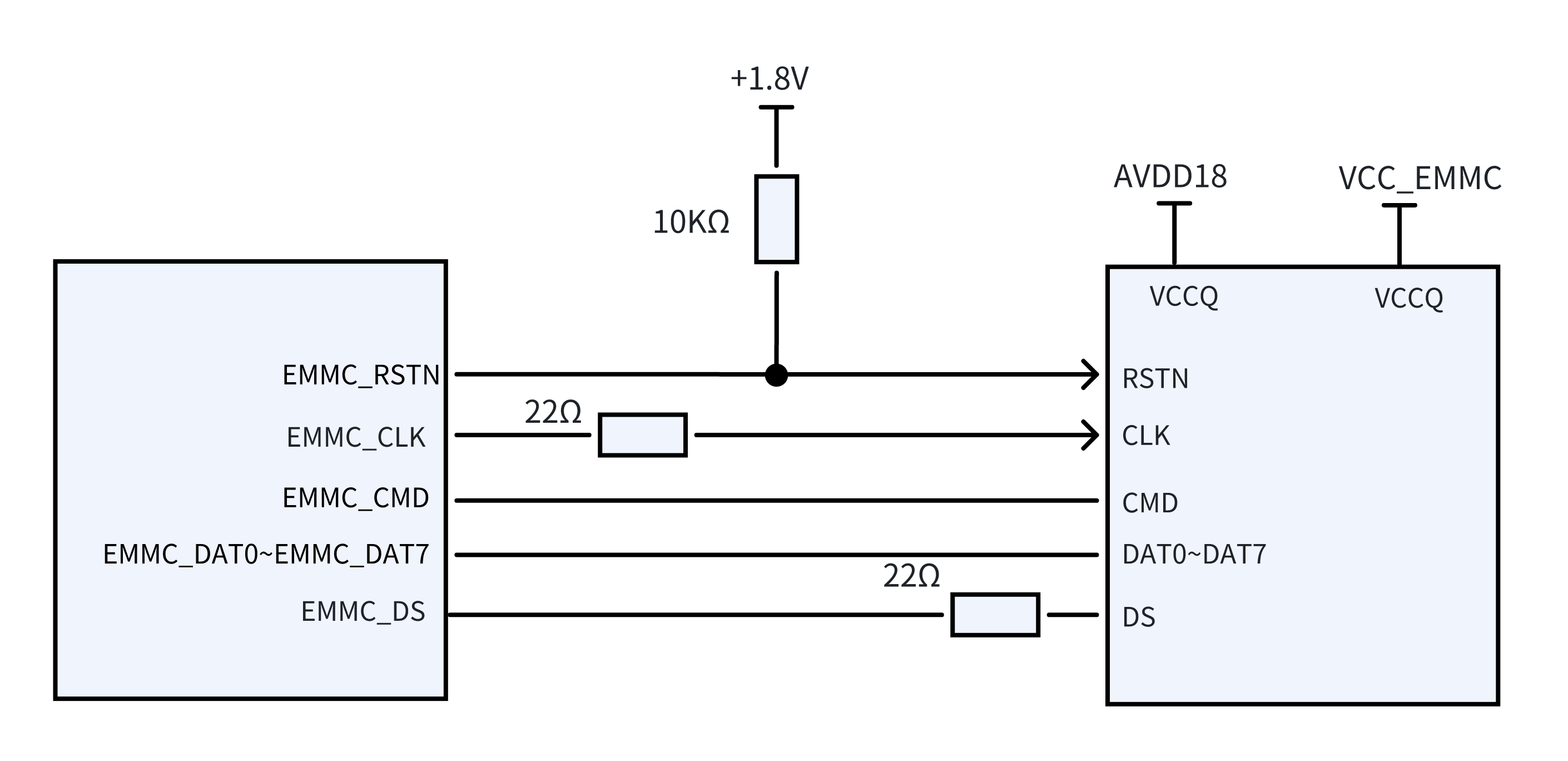

eMMC 拓扑结构与匹配方式设计

eMMC 的外部信号连接示意图。

eMMC接口设计推荐如下表所示。

| 信号 | 设计方法 |

|---|---|

| EMMC_CLK | SoC 端串联 22Ω 电阻。信号走线长度不超过 2inch。 |

| EMMC_CMD | 直接相连,信号走线长度不超过 2inch。 |

| EMMC_DAT0~7 | 直接相连,信号走线长度不超过 2inch。 |

| EMMC_DS | EMMC 端串联 22ohm,信号走线长度不超过 2inch。如果对接的 EMMC 器件无 DS 管脚,SoC 的 EMMC_DS 管脚可以悬空处理。 |

| EMMC_RSTN | 直接相连,10kΩ 上拉电阻。 |

eMMC 上电时序要求

A210 芯片 eMMC 接口有 AVDD33_EMMC 和 AVDD18_EMMC 两个电源。要求如下。

| eMMC PHY POWER | Min (V) | Typ (V) | Max (V) | |

|---|---|---|---|---|

| CORE | DVDD08_TOP | 0.72 | 0.8 | 0.88 |

| VDDIO33 | AVDD33_EMMC | 2.97 | 3.3 | 3.63 |

| VDDIO18 | AVDD18_EMMC | 1.62 | 1.8 | 1.98 |

QSPI Flash 电路

QSPI Flash(支持 Boot)接口介绍

A210 芯片有 2 个 QSPI 控制器用来连接 QSPI 设备。特点如下。

- 支持串行 NOR Flash,串行 Nand Flash。

- 支持 1 线,2 线以及 4 线模式。

当 QSPI0/1 接 Nor Flash 或 NAND Falsh 时,支持从对应 Flash Boot 通过 BOOT_SEL[2:0] 进行设置,见下表。

| BOOT_SEL[2] | BOOT_SEL[1] | BOOT_SEL[0] | BOOT MODE |

|---|---|---|---|

| 0 | 1 | 0 | QSPI1 NOR Flash Boot, CS0 |

| 0 | 1 | 1 | QSPI1 NAND Flash Boot,CS0 |

| 1 | 1 | 0 | QSPI0 NOR Flash, CS0 |

| 1 | 1 | 1 | QSPI0 NAND Flash, CS0 |

QSPI Flash 电路设计建议

在 QSPI Flash 接口设计时,QSPI Flash 信号接法请按参考原理图,包含各路电源去耦电容。

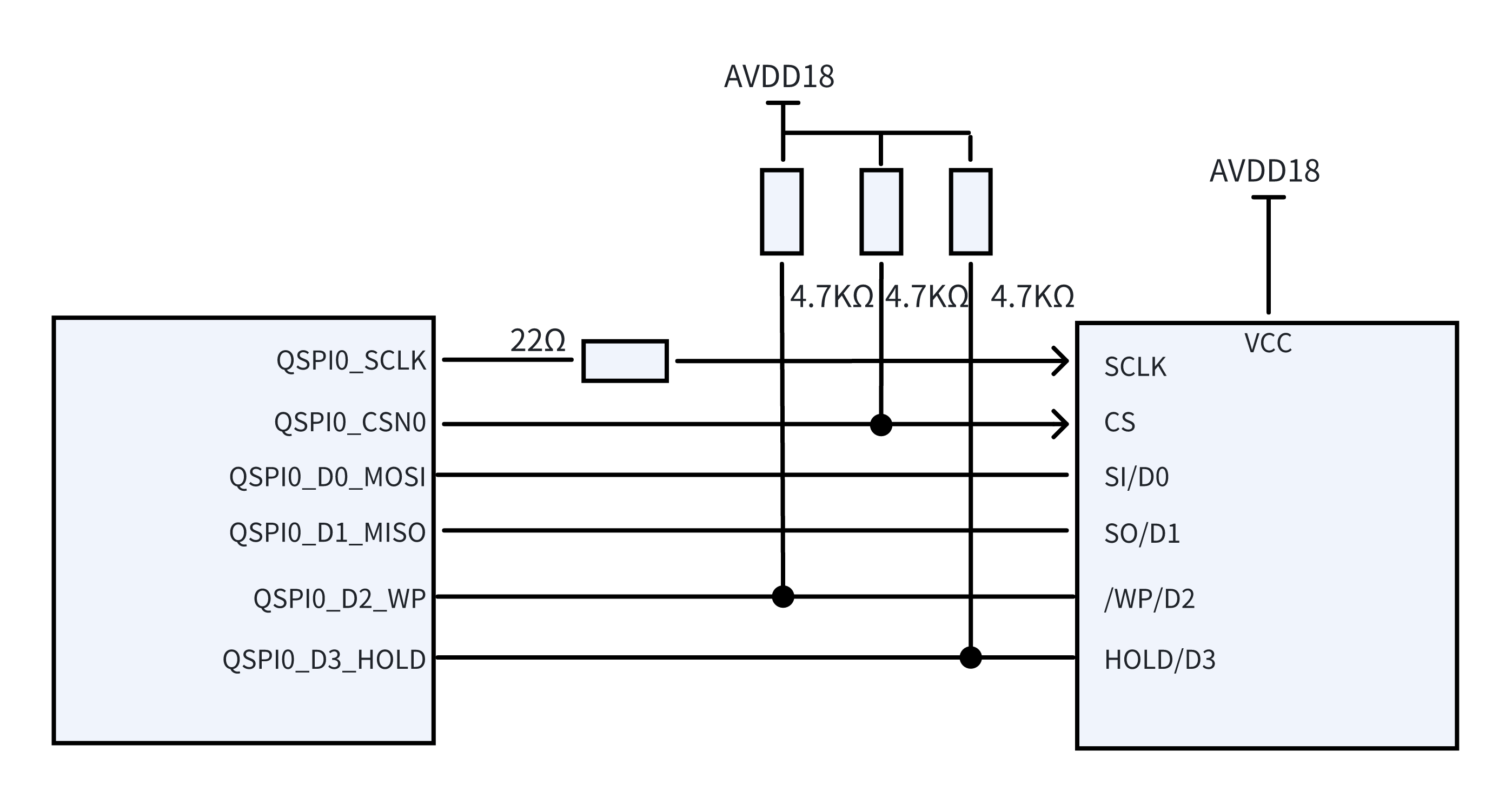

QSPI Flash 拓扑结构与匹配方式设计

以 QSPI0 为例,单片 SPI Flash 连接示意图如下,QSPI1 类似。

QSPI 接口设计推荐如下表所示。

| 信号 | 设计方法 |

|---|---|

| QSPI0_SCLK | SoC 端串接 22Ω 电阻。信号走线长度不超过 2inch。 |

| QSPI0_CSN0 | 直接相连,其中 QSPI0_D2_WP/QSPI0_D3_HOLD 和 QSPI0_CSN0 需要上拉,推荐上拉电阻阻值为 4.7kΩ。 信号走线长度不超过 2inch。 |

| QSPI0_D0_MOSI | |

| QSPI0_D1_MISO | |

| QSPI0_D2_WP | |

| QSPI0_D3_HOLD | |

| QSPI1_SCLK | SoC 端串接 22Ω 电阻。信号走线长度不超过 2inch。 |

| QSPI1_CSN0 | 直接相连,其中 QSPI1_D2_WP/QSPI1_D3_HOLD 和 QSPI1_CSN0 需要上拉,推荐上拉电阻阻值为 4.7kΩ。信号走线长度不超过 2inch。 |

| QSPI1_D0_MOSI | |

| QSPI1_D1_MISO | |

| QSPI1_D2_WP | |

| QSPI1_D3_HOLD |

QSPI 上电时序要求

A210 芯片 FSPI Flash 接口只有一组供电,并无时序要求。

SPI Flash 只有一路 1V8 电源,注意 Flash 的电平匹配。

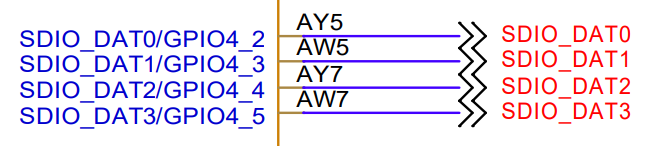

SDIO 接口

SDIO(支持 Boot)接口介绍

A210 芯片有 1 个 SDIO 控制器,可以用来连接 SDIO 设备。

- 支持 SD3.0/SDIO3.0。

- 支持 SDR12/SDR25/SDR50/SDR104 模式。

- 支持 1 位/4 位数据位宽。

- 支持 3.3V 和 1.8V 电压切换。

当外部接 SD card 时,支持从 SD card Boot 通过 BOOT_SEL[2:0] 进行设置,见下表。

| BOOT_SEL[2] | BOOT_SEL[1] | BOOT_SEL[0] | BOOT MODE |

|---|---|---|---|

| 1 | 0 | 1 | SD Card Boot, SDIO0 |

SD Card 电路设计建议

在 SDIO 接口设计时,SD Card 信号接法请按参考原理图,包含各路电源去耦电容。

SD Card 拓扑结构与匹配方式设计

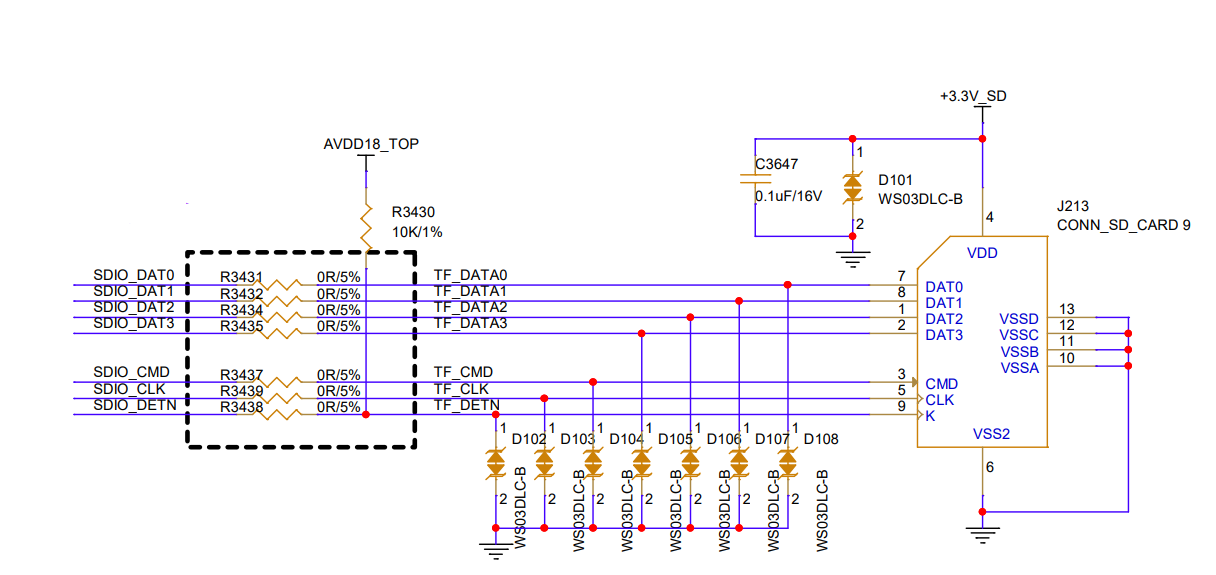

当外接 SD 卡时,参考原��理图如下。

推荐设计如下。

| 信号 | 设计方法 |

|---|---|

| SDIO0_CLK | 在 SOC 端串联 22Ω 电阻,距离源端小于 0.6inch,走线长度不能超过 4inch。 |

| SDIO0_CMD | 走线长度不能超过 4inch。 |

| SDIO0_DAT0~3 | 在 SOC 端串联 22Ω 电阻,距离源端小于 1inch。 |

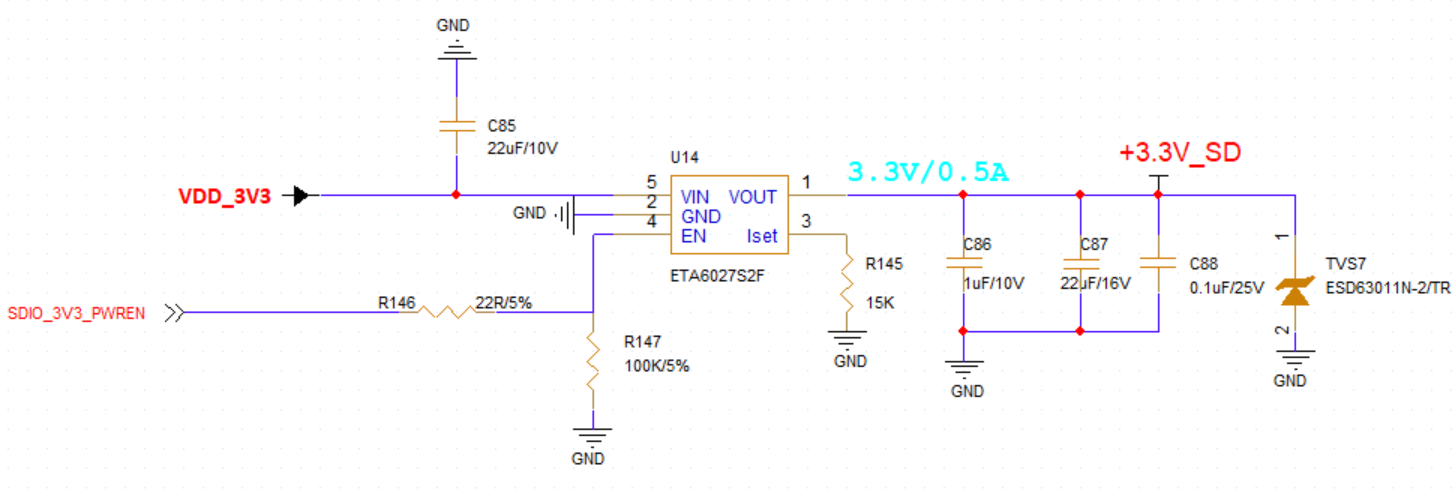

| SD 卡电源使能 | 因为 SD 卡没有复位信号,因此如果 SD 卡需要复位的时候,只能掉电再上电,因此可以使用 GPIO 来控制电源关闭和开启。 |

SDIO 接 Wi-Fi 时注意点

SDIO 接口除了接 SD card 以外,常用的还会接 Wi-Fi 模块。当接 Wi-Fi 模块时注意点如下。

- 请确保模组的 IO 电平与 CPU 的 IO 电平保持一致,否则需要做电平匹配处理。

- 晶体负载电容请根据实际使用的晶体的 CL 电容值选择,并控制常温下的频率容限在 10ppm 以内。

- 天线预留 π 型电路用于天线匹配调节。

GPIO 电路

A210 的所有 GPIO 均为 1.8V。其中命名为 AOGPIOx_x 的GPIO 为 AON 类 GPIO,可作为唤醒接口,此类 GPIO 电源域为 AVDD18_AON。

电源设计

A210电源介绍

A210芯片电源需求

| 模块 | 芯片管脚 | 电源描述 |

|---|---|---|

| TOP | DVDD08_TOP | TOP 数字电,同时包含:VI, VO, USB, PCIe, PERI 1/2/3, ADC, VT sensor。 |

| AVDD18_TOP | Peri 1/2 PAD, ADC, VT sensor。 | |

| C902 | DVDD08_AON | AON 数字电,同时包含:POR, RC。 |

| AVDD18_AON | AON PAD, POR, RC。 | |

| CPU | DVDD_CPU | CPU_SS/C908 数字电。 |

| DVDM_CPU | CPU_SS/C908 MEM 电。 | |

| DVDD_CPU_P | C920 数字电。 | |

| GPU | DVDD_GPU | GPU_SS 数字电。 |

| NPU | DVDD_NPU | NPU_SS 顶层数字电。 |

| DVDD_NPU_VIP | NPU_SS 计算核数字电,含:SLICE A/B/C, PPP。 | |

| PLL | DVDD08_PLL | 所有 PLL 的数字电。 |

| AVDD18_PLL | 所有 PLL 的模拟电。 | |

| VP | DVDD_VP | VP_SS 数字电,含:VENC, VDEC, G2D。 |

| DDR | DVDD08_DDR | DDR_SS 数字电,含:DDR CTRL, SLC。 |

| DDR_PHY | AVDD12_DDR_VDDQ_0 | DDR PHY IO 电。 |

| AVDD12_DDR_VDDQ_1 | ||

| AVDD06_DDR_VDDQLP_0 | DDR PHY IO 电。 | |

| AVDD06_DDR_VDDQLP_1 | ||

| AVDD18_DDR_VAA_0 | DDR PHY PLL 电。 | |

| AVDD18_DDR_VAA_1 | ||

| MIPI_PHY | AVDD08_MIPI | MIPI CSIO/1/2/3, MIPI DSI, HDMI PHY 的 0.8V 模拟电。 |

| AVDD18_MIPI | MIPI CSIO/1/2/3, MIPI DSI, HDMI PHY 的 1.8V 模拟电。 | |

| USB2_PHY | DVDD08_USB2 | USB2 0/1/2 的 0.8V 数字电。 |

| AVDD33_USB2 | USB2 0/1/2 的 3.3V 模拟电。 | |

| AVDD18_USB2 | USB2 0/1/2 的 1.8V 模拟电。 | |

| USB31_PHY | AVDD08_USB3 | USB31 的 0.8V 模拟电。 |

| AVDD18_USB3 | USB31 的 1.8V 模拟电。 | |

| PCIE_PHY | AVDD08_PCIE3 | PCIe0/1 的 0.8V 模拟电。 |

| AVDD18_PCIE3 | PCIe0/1 的 1.8V 模拟电。 | |

| EMMC_PHY | AVDD33_EMMC | eMMC/SD 的 3.3V 模拟电。 |

| AVDD18_EMMC | eMMC/SD 的 1.8V 模拟电。 | |

| EFUSE_QPS | AVDD18_EFUSE | EFUSE 烧写用电。 |

| D2D_PHY | DVDD08_D2D | D2D 数字电。 |

| AVDD18_D2D | D2D PHY 1.8V 模拟电。 | |

| AVDD08_D2D | D2D PHY 0.8V 模拟电。 | |

| VSS | VSS | 数字地。 |

| AVSS_PLL | AVSS_PLL | PLL 地。 |

说明: 无 C2C 应用时,D2D_PHY 电源可接地。

A210芯片上下电时序要求

| 上电 | 下电 | 电源管脚 |

|---|---|---|

| 1 | 13 | AVDD18_AON |

| 2 | 12 | DVDD08_AON |

| 3 | 11 | AVDD18_TOP |

| 4 | 10 | DVDD08_PLL |

| 4 | 10 | DVDD08_TOP |

| 4 | 10 | AVDD08_USB3 |

| 4 | 10 | AVDD08_PCIE3 |

| 4 | 10 | DVDD08_USB2 |

| 5 | 9 | AVDD18_EMMC |

| 5 | 9 | AVDD18_USB2 |

| 6 | 8 | AVDD33_EMMC |

| 6 | 8 | AVDD33_USB2 |

| 7 | 7 | DVDD08_DDR |

| 8 | 6 | DVDD11_DDR_VDDQ |

| 9 | 5 | DVDD06_DDR_VDDQLP |

| 10 | 4 | DVDD18_DDR_VAA |

| 11 | 3 | DVDD_CPU |

| 12 | 2 | DVDDM_CPU |

| 13 | 1 | POR release |

说明:

- DVDD08_PLL,DVDD08_TOP,AVDD08_USB3,AVDD08_PCIE3,DVDD08_USB2 务必保持同时上下电。(板级可电源合并)

- 最小系统有强时序需求,理论上不同模拟 PHY 模块间无时序要求,最后电压上电稳定后, POR 至少保持 10ms 才能释放。

以下为模块电源时序说明。

-

DDR_PHY

DDR_PHY 虽然无时序需求,但是一般设计 PHY 与 DDR 颗粒共用一个电源,需要遵循颗粒上下电时序。

相对时序 SOC_DDR 电源管脚 DDR 颗粒电源管脚 1 AVDD18_DDR_VAA VDD1 2 AVDD12_DDR_VDDQ0/1 VDD2 3 AVDD06_DDR_VDDQLP0/1 VDDQ -

CPU

CPU 上电时序如下,下电反之。

相对时序 SOC_CPU 电源管脚 1 DVDD_CPU 2 DVDM_CPU 3 DVDD_CPU_P -

MIPI_PHY

MIPI_PHY 上电时序如下,下电反之。

相对时序 SOC_MIPI 电源管脚 1 AVDD08_MIPI 2 AVDD18_MIPI -

PCIE_PHY

PCIE_PHY 上电时序如下,下电反之。

相对时序 SOC_PCIE 电源管脚 1 AVDD08_PCIE3 2 AVDD18_PCIE3 -

USB2_PHY

USB2_PHY 上电时序如下,下电反之。

相对时序 SOC_USB2 电源管脚 1 DVDD08_USB2 2 AVDD18_USB2 3 AVDD33_USB2 -

EMMC_PHY

EMMC_PHY 上电时序如下,下电反之。

相对时序 SOC_PCIE 电源管脚 1 AVDD08_PCIE3 2 AVDD18_PCIE3

说明:

其余未提到模块均无�时序需求,总体必须遵循最小系统上下电。

A210 电源设计建议

上电和待机电路方案

A210 第一次上电各模块供电情况如下表。

| 模块 | 芯片管脚 | 第一次上电供电要求 |

|---|---|---|

| TOP | DVDD08_TOP | 必须供电。 |

| AVDD18_TOP | 必须供电。 | |

| AON | DVDD08_AON | 必须供电。 |

| AVDD18_AON | 必须供电。 | |

| CPU | DVDD_CPU | 必须供电。 |

| DVDM_CPU | 必须供电。 | |

| DVDD_CPU_P | 可以不供电。 | |

| GPU | DVDD_GPU | 可以不供电。 |

| NPU | DVDD_NPU | 可以不供电。 |

| DVDD_NPU_VIP | 可以不供电。 | |

| PLL | DVDD08_PLL | 必须供电。 |

| AVDD18_PLL | 必须供电。 | |

| VP | DVDD_VP | 可以不供电。 |

| DDR | DVDD08_DDR | 必须供电。 |

| DDR_PHY | AVDD12_DDR_VDDQ_0 | 可以不供电。 |

| AVDD12_DDR_VDDQ_1 | 可以不供电。 | |

| AVDD06_DDR_VDDQLP_0 | 可以不供电。 | |

| AVDD06_DDR_VDDQLP_1 | 可以不供电。 | |

| AVDD18_DDR_VAA_0 | 可以不供电��。 | |

| AVDD18_DDR_VAA_1 | 可以不供电。 | |

| MIPI_PHY | AVDD08_MIPI | 可以不供电。 |

| AVDD18_MIPI | 可以不供电。 | |

| USB2_PHY | DVDD08_USB2 | 必须供电。 |

| AVDD33_USB2 | 必须供电。 | |

| AVDD18_USB2 | 必须供电。 | |

| USB31_PHY | AVDD08_USB3 | 必须供电。 |

| AVDD18_USB3 | 可以不供电。 | |

| PCIE_PHY | AVDD08_PCIE3 | 必须供电。 |

| AVDD18_PCIE3 | 可以不供电。 | |

| EMMC_PHY | AVDD33_EMMC | 必须供电。 |

| AVDD18_EMMC | 必须供电。 | |

| EFUSE_QPS | AVDD18_EFUSE | 可以不供电。 |

| D2D_PHY | DVDD08_D2D | 可以不供电。 |

| AVDD18_D2D | 可以不供电。 | |

| AVDD08_D2D | 可以不供电。 | |

| VSS | VSS | 必须供电。 |

| AVSS_PLL | AVSS_PLL | 必须供电。 |

A210 芯片可支持低功耗待机方案,进入待机模式时,供电和断电情况如下表。

| 模块 | 芯片管脚 | Deepsleep | Standby |

|---|---|---|---|

| TOP | DVDD08_TOP | 不需要供电。 | 需要供电。 |

| AVDD18_TOP | 不需要供电。 | 需要供电。 | |

| AON | DVDD08_AON | 需要供电。 | 需要供电。 |

| AVDD18_AON | 需要供电。 | 需要供电。 | |

| CPU | DVDD_CPU | 不需要供电。 | 需要供电。 |

| DVDM_CPU | 不需要供电。 | 需要供电。 | |

| DVDD_CPU_P | 不需要供电。 | 不需要供电。 | |

| GPU | DVDD_GPU | 不需要供电。 | 不需要供电。 |

| NPU | DVDD_NPU | 不需要供电。 | 不需要供电。 |

| DVDD_NPU_VIP | 不需要供电。 | 不需要供电。 | |

| PLL | DVDD08_PLL | 不需要供电。 | 需要供电。 |

| AVDD18_PLL | 不需要供电。 | 需要供电。 | |

| VP | DVDD_VP | 不需要供电。 | 不需要供电。 |

| DDR | DVDD08_DDR | 不需要供电。 | 需要供电。 |

| DDR_PHY | AVDD12_DDR_VDDQ_0 | 需要供电。 | 需要供电。 |

| AVDD12_DDR_VDDQ_1 | 需要供电。 | 需要供电。 | |

| AVDD06_DDR_VDDQLP_0 | 不需要供电。 | 需要供电。 | |

| AVDD06_DDR_VDDQLP_1 | 不需要供电。 | 需要供电。 | |

| AVDD18_DDR_VAA_0 | 不需要供电。 | 需要供电。 | |

| AVDD18_DDR_VAA_1 | 不需要供电。 | 需要供电。 | |

| MIPI_PHY | AVDD08_MIPI | 不需要供电。 | 不需要供电。 |

| AVDD18_MIPI | 不需要供电。 | 不需要供电。 | |

| USB2_PHY | DVDD08_USB2 | 不需要供电。 | 需要供电。 |

| AVDD33_USB2 | 不需要供电。 | 需要供电。 | |

| AVDD18_USB2 | 不需要供电。 | 需要供电。 | |

| USB31_PHY | AVDD08_USB3 | 不需要供电。 | 需要供电。 |

| AVDD18_USB3 | 不需要供电。 | 需要供电。 | |

| PCIE_PHY | AVDD08_PCIE3 | 不需要供电。 | 需要供电。 |

| AVDD18_PCIE3 | 不需要供电。 | 需要供电。 | |

| EMMC_PHY | AVDD33_EMMC | 不需要供电。 | 不需要供电。 |

| AVDD18_EMMC | 不需要供电。 | 不需要供电。 | |

| EFUSE_QPS | AVDD18_EFUSE | 不需要供电。 | 不需要供电。 |

| D2D_PHY | DVDD08_D2D | 不需要供电。 | 不需要供电。 |

| AVDD18_D2D | 不需要供电。 | 不需要供电。 | |

| AVDD08_D2D | 不需要供电。 | 不需要供电。 | |

| VSS | VSS | 需要供电。 | 需要供电。 |

| AVSS_PLL | AVSS_PLL | 需要供电。 | 需要供电。 |

说明:

deepsleep 模式待机下,只能支持 AON_GPIO,AON RTC唤醒。standby 模式待机下,额外支持除了 AON_GPIO 外的 GPIO,USB,PCIe 唤醒。

TOP 电源

A210 芯片 TOP 电源分为两部分,分别为 DVDD08_TOP 和 AVDD18_TOP。

A210 USB2 电源见下表。

| 电源名称 | deepsleep | Vboot电压(V) | 峰值电流(mA) |

|---|---|---|---|

| DVDD08_TOP | 不需要供电。 | 0.8 | 2151.75 |

| AVDD18_TOP | 不需要供电。 | 1.8 | 400 |

-

AVDD18_TOP 包含 ADC 供电,建议使用 LDO 供电。

-

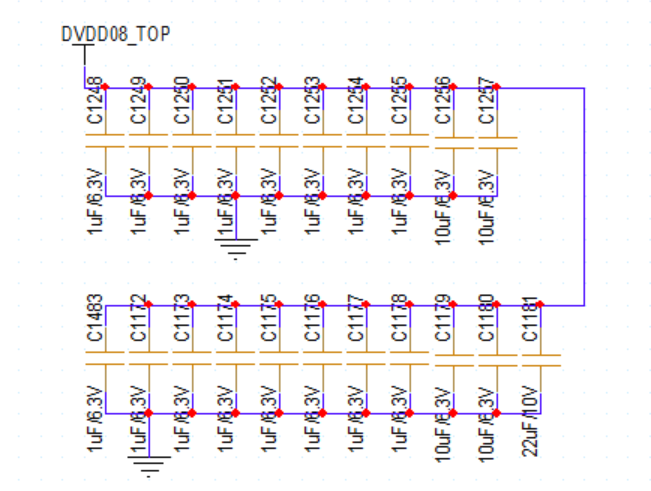

DVDD08_TOP 在参考设计中与 DVDD08_USB2,DVDD08_PLL,AVDD08_USB3,AVDD08_MIPI,AVDD08_PCIE 合并,DVDD08_TOP 去耦电容图如下。(图中为电源板级合并后的去耦电容总数)

-

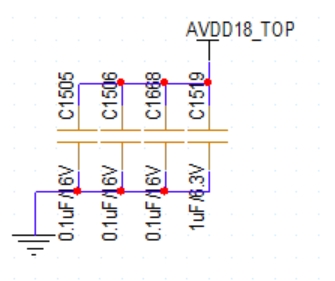

AVDD18_TOP 芯片管脚附近放置 1 个 1uF 和 3 个 0.1uF 电容。DVDD18_TOP 去耦电容图如下。

说明:

由于DVDD08_TOP 在参考设计中会和多个电源合并,所以其中 1uF 电容会分配到其他合并电源中去,总数不变。

PLL 电源

A210 芯片 PLL 电源分为两部分,分别为DVDD08_PLL和AVDD18_PLL。A210 PLL 电源表如下。

| 电源名称 | deepsleep | Vboot电压(V) | 峰值电流(mA) |

|---|---|---|---|

| DVDD08_PLL | 不需要供电。 | 0.8 | 14.25 |

| AVDD18_PLL | 不需要供电。 | 1.8 | 90.27 |

- AVDD18_PLL 建议使用 LDO 供电。

- DVDD08_PLL 有同时上下电的需求,在参考设计中与 DVDD08_TOP,DVDD08_USB2,AVDD08_USB3,AVDD08_MIPI,AVDD08_PCIE 电源合并,DVDD08_PLL 管脚附近放置 1 个 1uF 电容。

- AVDD18_PLL 芯片管脚附近放置 2 个 0.1uF 电容。

USB2 电源

A210 芯片 USB2 电源分为三部分,分别为DVDD08_USB2,AVDD18_USB2,AVDD33_USB2。A210 USB2 电源表如下。

| 电源名称 | deepsleep | Vboot电压(V) | 峰值电流(mA) |

|---|---|---|---|

| DVDD08_USB2 | 不需要供电。 | 0.8 | 36.53 |

| AVDD18_USB2 | 不需要供电。 | 1.8 | 58.68 |

| AVDD33_USB2 | 不需要供电。 | 3.3 | 10.53 |

-

AVDD18_USB2,AVDD33_USB2 建议使用 LDO 供电。

-

DVDD08_USB2 有同时上下电的需求,在参考设计中与 DVDD08_TOP,DVDD08_PLL,AVDD08_USB3,AVDD08_MIPI,AVDD08_PCIE 电源合并,DVDD08_USB2 芯片管脚附近放置 1 个 1uF 电容。

-

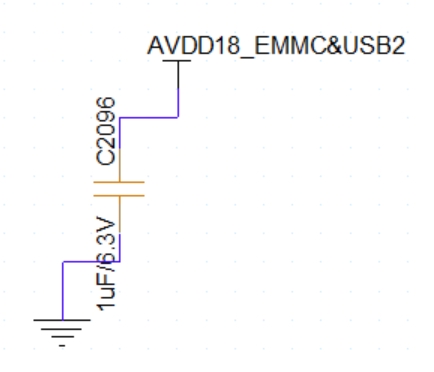

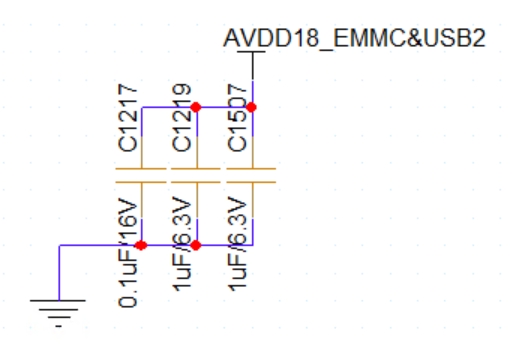

AVDD18_USB2 在参考设计中与 AVDD18_EMMC 电源合并,AVDD18_USB2 芯片管脚附近放置 1 个 1uF 电容。AVDD18_USB2 去耦电容图如下。

-

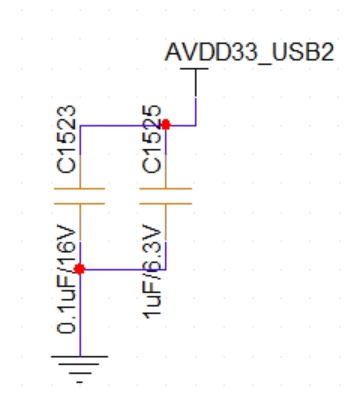

AVDD33_USB2 芯片管脚附近放置 1 个 1uF 和 1 个 0.1uF 的电容。AVDD33_USB2 去耦电容图如下。

USB3 电源

A210 芯片 USB3 电源分为两部分,分别为AVDD08_USB3,AVDD18USB3。

| 电源名称 | deepsleep | Vboot电压(V) | 峰值电流(mA) |

|---|---|---|---|

| AVDD08_USB3 | 不需要供电。 | 0.8 | 119.4 |

| AVDD18_USB3 | 不需要供电。 | 1.8 | 30.38 |

- AVDD18_USB3 建议使用 LDO 供电。

- AVDD08_USB3 在参考设计中与 DVDD08_TOP,DVDD08_USB2,DVDD08_PLL,AVDD08_MIPI,AVDD08_PCIE 电源合并,AVDD08_USB3 芯片管脚附近放置 1 个 1uF 电容。

- AVDD18_USB3 在参考设计中与 AVDD18_MIPI,AVDD18_EFUSE,AVDD18_PCIE 合并,AVDD18_USB3 芯片管脚附近放置 1 个 1uF 电容和 1 个 0.1uF 电容。

EMMC 电源

A210 芯片 EMMC 电源分为两部分,分别为AVDD18_EMMC,AVDD33_EMMC。

| 电源名称 | deepsleep | Vboot电压(V) | 峰值电流(mA) |

|---|---|---|---|

| AVDD18_EMMC | 不需要供电。 | 1.8 | 323.4 |

| AVDD33_EMMC | 不需要供电。 | 3.3 | 20.83 |

-

AVDD18_EMMC,AVDD33_EMMC 建议使用 LDO 供电。

-

AVDD18_EMMC 在参考设计中与 AVDD18_USB2 合并,AVDD18_EMMC 芯片管脚附近放置 2 个 1uF 电容与 1 个 0.1uF 电容。AVDD18_EMMC 去耦电容图如下。

-

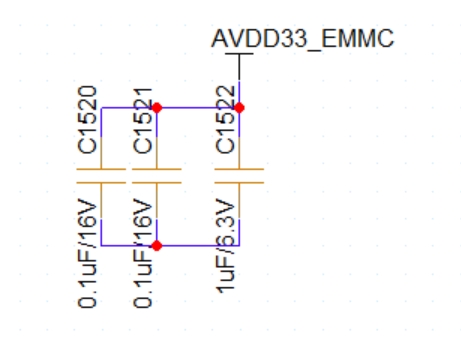

AVDD33_EMMC芯片管脚附近放置1个1uF电容和2个0.1uF电容。AVDD33_EMMC 去耦电容图如下。

AON 电源

A210 芯片 USB3 电源分为两部分,分别为AVDD18_AON,DVDD08_AON。

| 电源名称 | deepsleep | Vboot电压(V) | 峰值电流(mA) |

|---|---|---|---|

| DVDD08_AON | 需要供电。 | 0.8 | 100 |

| AVDD18_AON | 需要供电。 | 1.8 | 50 |

-

AVDD18_AON 建议使用 LDO 供电。

-

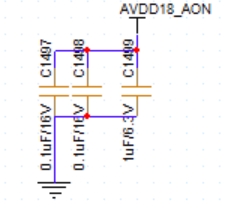

AVDD18_AON 芯片管脚附近放置 1 个 1uF 电容和 2 个0.1uF 电容。AVDD18_AON 去耦电容图如下。

-

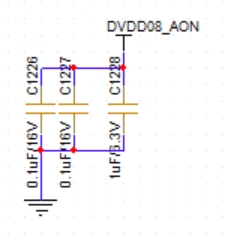

DVDD08_AON 芯片管脚附近放置 1 个 1uF 电容和 2 个 0.1uF 电容。DVDD08_AON 去耦电容图如下。

MIPI 电源

A210 芯片 MIPI 电源分为两部分,分别为AVDD08_MIPI,AVDD18_MIPI。

| 电源名称 | deepsleep | Vboot电压(V) | 峰值电流(mA) |

|---|---|---|---|

| AVDD08_MIPI | 不需要��供电。 | 0.8 | 144.3 |

| AVDD18_MIPI | 不需要供电。 | 1.8 | 43.86 |

-

AVDD18_MIPI 建议使用 LDO 供电。

-

AVDD08_MIPI 在参考设计中与 DVDD08_USB2,DVDD08_PLL,AVDD08_USB3,DVDD08_TOP,AVDD08_PCIE 合并,AVDD08_MIPI 芯片管脚附近放置 1 个 1uF 电容和 2 个 0.1uF 电容。AVDD08_MIPI 去耦电容图如下。

-

AVDD18_MIPI 在参考设计中与AVDD18_USB3,AVDD18_EFUSE,AVDD18_PCIE 合并,AVDD18_MIPI 芯片管脚附近放置 1 个 1uF 电容和 1 个 0.1uF 电容。

PCIE 电源

A210 芯片 PCIE 电源分为两部分,分别为 AVDD08_PCIE,AVDD18_PCIE。

| 电源名称 | deepsleep | Vboot电压(V) | 峰值电流(mA) |

|---|---|---|---|

| AVDD08_PCIE | 不需要供电。 | 0.8 | 348.26 |

| AVDD18_PCIE | 不需要供电。 | 1.8 | 165 |

-

AVDD18_PCIE 建议使用 LDO 供电。

-

AVDD08_PCIE 在参考设计中与 DVDD08_USB2,DVDD08_PLL,AVDD08_USB3,DVDD08_TOP,AVDD08_MIPI 合并,AVDD08_PCIE 芯片管脚附近放置 1 个 10uF 电容,1 个 1uF 电容和 2 个 0.1uF 电容。AVDD08_PCIE 去耦电容图如下。

-

AVDD18_PCIE 在参考设计中与 AVDD18_USB3,AVDD18_EFUSE,AVDD18_MIPI 合并,AVDD18_PCIE 芯片管脚附近放置 1 个 1uF 电容和 1 个 0.1uF 电容。

EFUSE 电源

A210 芯片 EFUSE 电源为 AVDD18_EFUSE。

| 电源名称 | deepsleep | Vboot电压(V) | 峰值电流(mA) |

|---|---|---|---|

| AVDD18_EFUSE | 不需要供电。 | 1.8 | 6 |

- AVDD18_EFUSE 建议使用 LDO 供电。

- AVDD18-EFUSE 在参考设计中与 AVDD18_USB3,AVDD18_PCIE,AVDD18_MIPI 合并,AVDD18-EFUSE 芯片管脚附近放置 1 个 1uF 电容和 1 个 0.1uF 电容。

D2D 电源

A210 芯片 D2D 电源分为三部分,分别为 AVDD08_D2D,DVDD08_D2D,AVDD18_D2D。

单 CHIP 应用时,D2D 电源可接地。

DDR 电源

A210 芯片 DDR 电源分为四部分,分别为 DVDD08_DDR,DVDD18_DDR_VAA,DVDD11_DDR_VDDQ,DVDD06_DDR_VDDQLP。

DVDD08_DDR为SLC时的电源。

DVDD18_DDR_VAA,DVDD11_DDR_VDDQ,DVDD06_DDR_VDDQLP 为 SOC DDR 控制器和 DDR 颗粒合并供电,DDR 颗粒侧请参考 DDR 电路。

| 电源名称 | deepsleep | Vboot电压(V) | 峰值电流(mA) |

|---|---|---|---|

| DVDD08_DDR | 不需要供电。 | 0.8 | 2193 |

| DVDD18_DDR_VAA | 不需要供电。 | 1.8 | 300 |

| DVDD11_DDR_VDDQ | 需要供电。 | 1.1 | 2017.28 |

| DVDD06_DDR_VDDQLP | 不需要供电。 | 0.6 | 1250 |

-

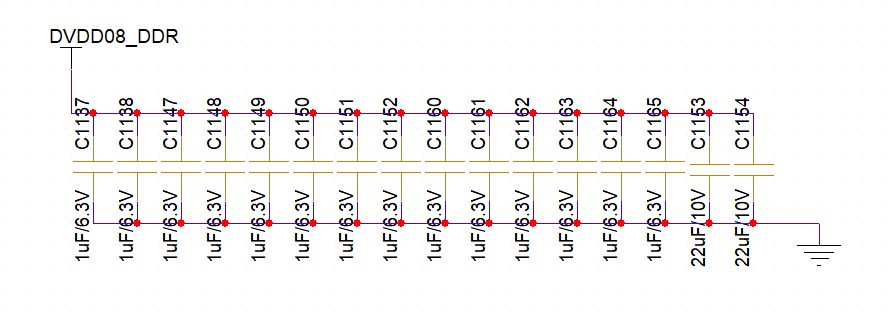

DVDD08_DDR 芯片管脚附近放置 14 个 1uF 电容和 2 个 22uF 电容。DVDD08_DDR 去耦电容图如下。

-

DVDD18_DDR_VAA 芯片管脚附近放置 2 个 1uF 电容和 2 个 0.1uF 电容。由于 DDR 控制器和 DDR 颗粒合并供电,DDR 颗粒侧的去耦电容请参考 DDR 电路。

-

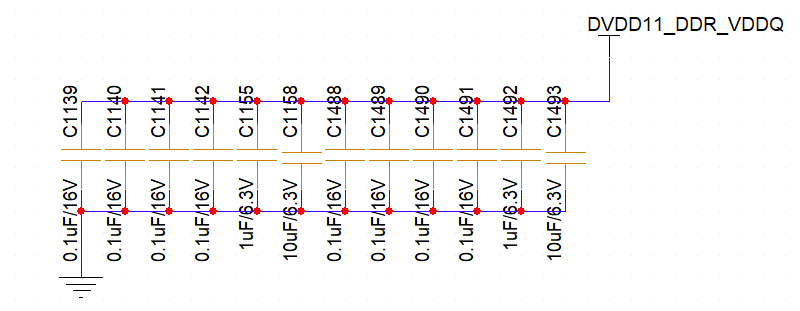

DVDD11_DDR_VDDQ 芯片管脚附近放置 8 个 0.1uF 电容,4 个 1uF 电容和 2 个 10uF 电容,建议把电容均匀分布与两个 DDR 通道的管脚。DVDD11_DDR_VDDQ 去耦电容图如下。

-

DVDD06_DDR_VDDQLP 芯片管脚附近放置 2 个 0.1uF 电容和 1 个 1uF 电容。DVDD06_DDR_VDDQLP去耦电容图如下。

VP 电源

A210 芯片 VP 电源部分为DVDD_VP。

| 电源名称 | deepsleep | Vboot电压(V) | 可支持电压(V) | 峰值电流(mA) |

|---|---|---|---|---|

| DVDD_VP | 不需要供电。 | 0.8 | 0.75/0.8/0.9 | 1500 |

- VP 电源支持 DVFS。

- DVDD_VP 芯片管脚附近放置 5 个 1uF 电容和 1 个 10uF 电容。DVDD_VP 去耦电容图如下。

GPU 电源

A210 芯片 GPU 电源部分为 DVDD_GPU。

| 电源名称 | deepsleep | Vboot电压(V) | 可支持电压(V) | 峰值电流(mA) |

|---|---|---|---|---|

| DVDD_GPU | 不需要供电。 | 0.8 | 0.75/0.8 | 1419 |

- GPU 电源支持 DVFS。

- DVDD_GPU 芯片管脚附近放置 7 个 1uF 电容。DVDD_GPU去耦电容图如下。

CPU 电源

A210 芯片 CPU 电源部分为三部分,DVDDM_CPU,DVDD_CPU,DVDD_CPU_P。

| 电源名称 | deepsleep | Vboot电压(V) | 可支持电压(V) | 峰值电流(mA) |

|---|---|---|---|---|

| DVDDM_CPU | 不需要供电。 | 0.8 | 0.55~1 | 300 |

| DVDD_CPU | 不需要供电。 | 0.8 | 0.55~1 | 3522.68 |

| DVDD_CPU_P | 不需要供电。 | 0.8 | 0.8~1 | 5547.9 |

-

DVDDM_CPU,DVDD_CPU_DVDD_CPU_P 支持 DVFS,DVFS 需遵循 DVDD_CPU 0.55V 时,DVDD_CPU_P 不能提压超过 0.9V,DVDD_CPU_P 1V 时,DVDD_CPU 不能降压小于 0.7V。

-

DVDDM_CPU 芯片管脚附近放置 3 个 1uF 电容。DVDDM_CPU 去耦电容图如下。

-

DVDD_CPU 芯片管脚附近放置放置 5 个 1uF 电容和 1 个 10uF 电容。DVDD_CPU 去耦电容图如下。

-

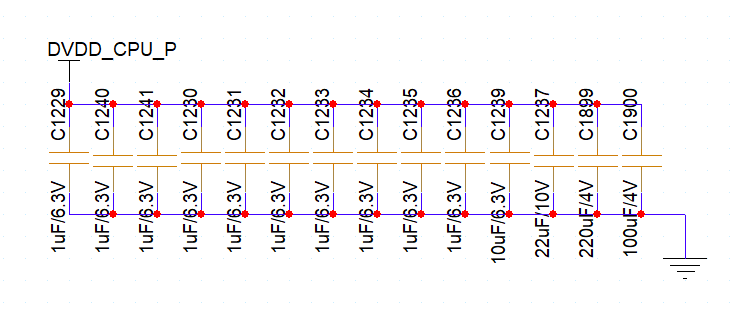

DVDD_CPU_P 芯片管脚附近放置 10 个 1uF 电容,1 个 10uF 电容,1 个 22uF 电容,1 个 100uF 电容和 1 个 220uF 电容。DVDD_CPU_P去耦电容图如下。

NPU 电源

A210 芯片 NPU 电源部分为两部分,DVDD_NPU,DVDD_NPU_VIP。

| 电源名称 | deepsleep | Vboot电压(V) | 可支持电压(V) | 峰值电流(mA) |

|---|---|---|---|---|

| DVDD_NPU | 不需要供电。 | 0.8 | 0.75/0.8/0.9 | 2258.4 |

| DVDD_NPU_VIP | 不需要供电/ | 0.8 | 0.75/0.8/0.9 | 13768.8 |

-

DVDD_NPU,DVDD_NPU_VI 支持 DVFS,在参考设计中两电源合并。

-

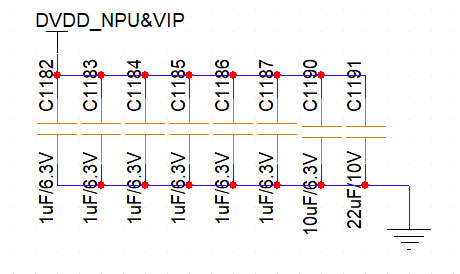

DVDD_NPU 芯片管脚附近放置 6 个 1uF 电容,1 个 10uF 电容和 1 个 22uF 电容。DVDD_NP U去耦电容图如下。

-

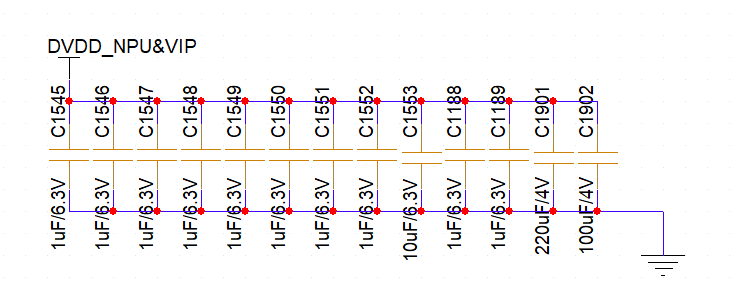

DVDD_NPU_VIP 芯片管脚附近放置 10 个 1uF 电容,1 个 10uF 电容,1 个 100uF 电容和 1 个 220uF 电容。DVDD_NPU_VIP 去耦电容图如下。

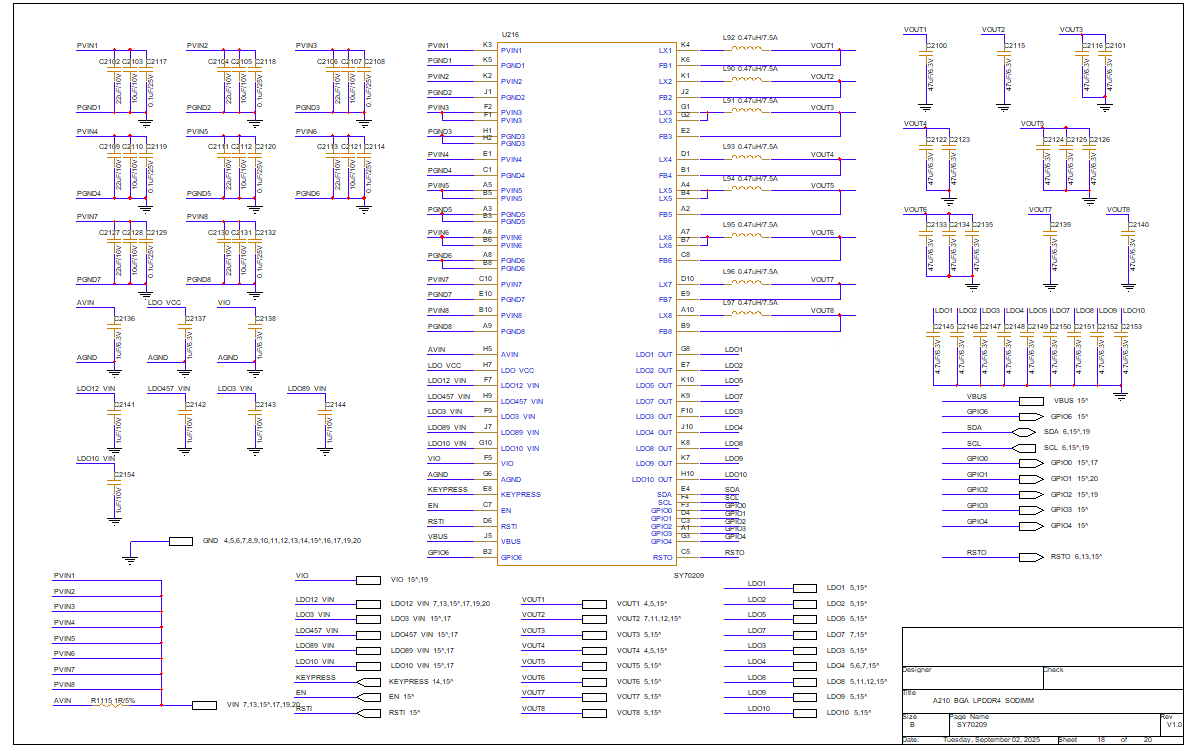

ZH70809G&ZH70300 方案介绍

ZH70809G&ZH70300 特征

ZH70809G 特征表如下。

| 封装大小 | 输入电压 | 待机电流 | 类型 | 通道 | 电压范围 | 调压 STEP | 电压精度(静态) | 动态响应 | 负载能力(mA) | 通信 |

|---|---|---|---|---|---|---|---|---|---|---|

| 4.21mm×4.21mm | 2.5V-5.5V | 20uA | Buck | BUCK1 | 1.2-3.5625 V | 37.5 mV | PWM Mode:±1% Normal Mode:±1.5% ECO Mode:±3% | VOUT:1.8V 0.5A/uS VPP:100mV | 1500 | I2C |

| BUCK2 | 1.7125-3.3 V | 12.5mV | PWM Mode:±1% Normal Mode:±1.5% ECO Mode:±3% | VOUT:2.5V 0.5A/uS VPP:100mV | 2000 | |||||

| BUCK3 | 0.7125-1.5V | 12.5 mV | PWM Mode:±1% Normal Mode:±1.5% ECO Mode:±3% | VOUT:1.1V 0.5A/uS VPP:60mV | 4000 | |||||

| BUCK4 | 0.3-1.0875V | 12.5mV | PWM Mode:±1% Normal Mode:±1.5% ECO Mode:±3% | VOUT:0.6V 0.5A/uS VPP:60mV | 1500 | |||||

| BUCK5/6 | 0.6-2.1875V | 12.5mV | PWM Mode:±1% Normal Mode:±2% ECO Mode:±3% | VOUT:1V 1A/uS VPP:40/50mV | 3000/4000 | |||||

| BUCK7 | 0.6-2.1875V | 12.5mV | PWM Mode:±1% Normal Mode:±2% ECO Mode:±3% | VOUT:0.9V 0.5A/uS VPP:100mV | 1000 | |||||

| BUCK8 | 0.6-2.1875V | 12.5mV | PWM Mode:±1% Normal Mode:±2% ECO Mode:±3% | VOUT:1.2V 0.5A/uS VPP:100mV | 1500 | |||||

| LDO | LDO1/2/5/7/10 | 1.2-3.3V | / | ±2% | VPP:100mV | 400 | ||||

| LDO4 | 0.6-3.3V | / | ±2% | VPP:100mV | 400 | |||||

| LDO3 | 0.6~1.15V | / | ±2% | VPP:100mV | 400 | |||||

| LDO8/9 | 0.75-1.8V | / | ±2% | VPP:100mV | 300 |

-

支持修改电源启动时序控制。

-

额外 6 个 GPIO 可通过 I2C 控制。

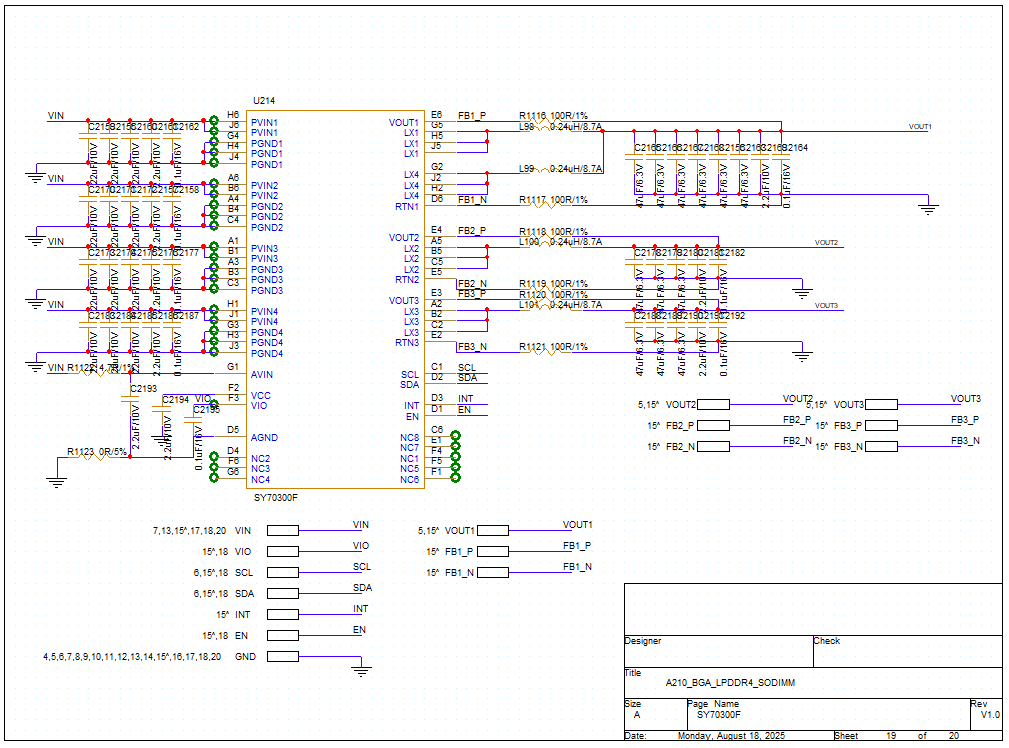

ZH70300 特征表如下。

| 封装大小 | 输入电压 | 待机电流 | 类型 | 通道 | 电压范围 | 调压 STEP | 电压精度(静态) | 负载能力(mA) |

|---|---|---|---|---|---|---|---|---|

| 2.66mm*3.84mm | 2.5V-5.5V | 6uA | Buck | BUCK1&BUCK2 | 0.3~1.85V | 5mV&10mV | ±1.25% | 12000 |

| BUCK3 | 0.45-2V | 5mV&10mV | ±1.25% | 6000 | ||||

| BUCK4 | 0.45-2V | 5mV&10mV | ±1.25% | 6000 |

ZH70809G 注意事项

-

ZH70809G 的 VIO(PIN F5): 是 ZH70809G 芯片内部 IO 数字逻辑供电,在参考设计中 VIO 由 ZH70809G 的LDO4(1.8V)供电,GPIO 输出的高低电平与 VIO 无关。

-

ZH70809G 的 RSTO(PIN C5): 是给 SOC 的复位信号输出,需要外部拉高至 VIO,在所有电源上电完毕后,延迟 40ms,输出高。

-

ZH70809G 的 RSTI(PIN D6):是复位 ZH70809G 的输入脚,当 ZH70809G 被复位时,所有电源电压恢复至 DEFAULT 值,RSTO 重新输出,需要注意的是默认开启的电源并不会下电再上电。

-

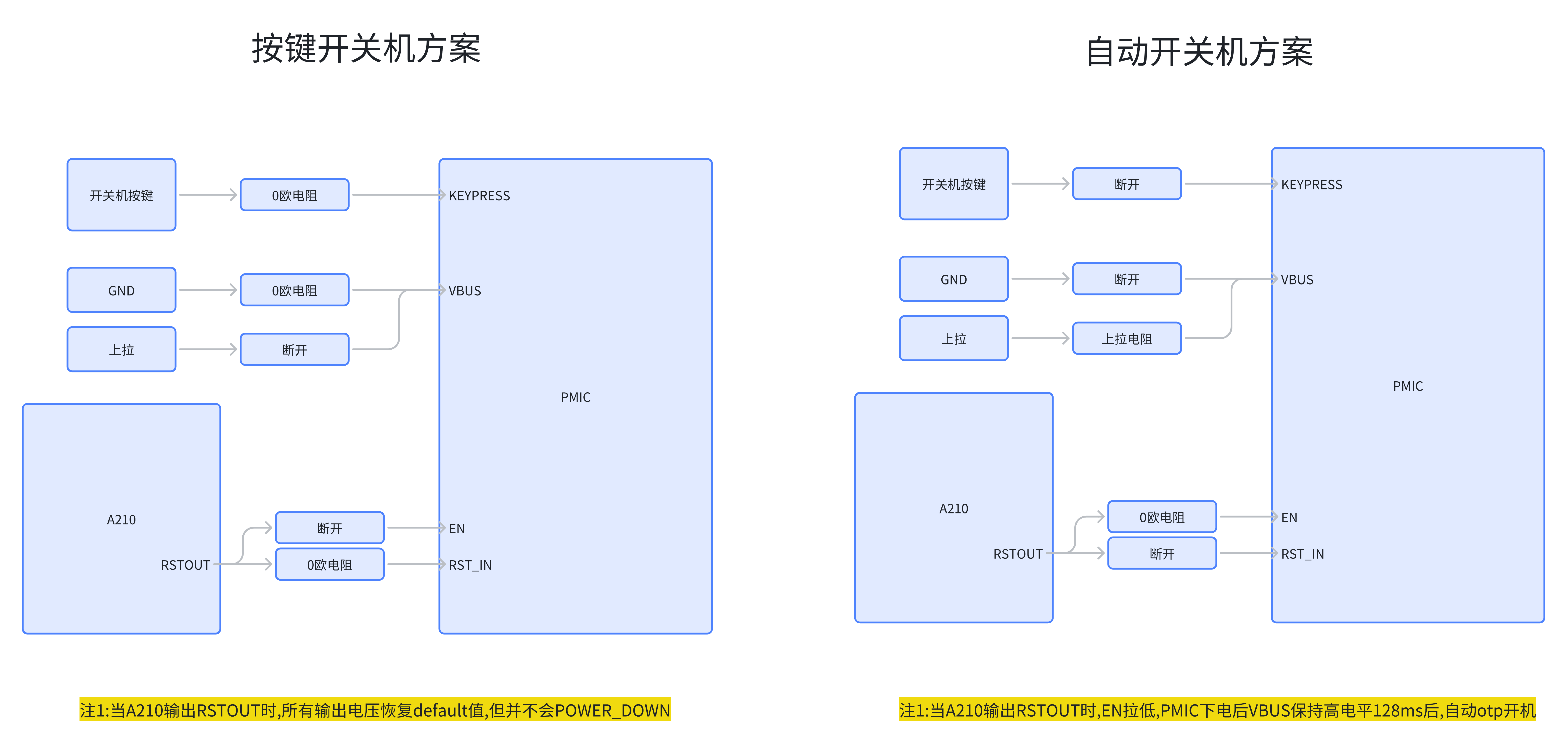

ZH70809G 的 KEYPRESS(PIN E8),EN(PIN C7),VBUS(PIN J5): 都与 ZH70809G 开机有关,有两种开关机方案下如下图,两种方案不能同时存在。

- 按键开机方案中,当 KEYPRESS 保持低电平 4ms 后开机,开机后保持低电平 1s(可配置 10s)后,关机。

- 自动开关机方案中,当 A210 异常输出脚拉低 EN 后,关机,128ms 后自动开机。

-

ZH70809G 的 SDA(PIN E4) SCL(PIN F4): 是ZH70809G I2C 通讯脚,需拉高至 VIO。

-

其余引脚均为电源输入输出脚,需注意 FB,SW 的布线,输入输出电容数量,电感感值请不要随意改动,原理图参考下图。

ZH70300 注意事项

-

ZH70300 的 EN(PIN 1D): 是ZH70300的开机信号,在参考设计中由 ZH70809G GPIO 控制。

-

ZH70300 的 SDA(PIN 2D) SCL(PIN 1C): 是 ZH70300 I2C 通讯脚,需拉高至 VIO。

-

ZH70809G 的 VIO(PIN 3F): 是 ZH703009 片内部 IO 数字逻辑供电,在参考设计中 VIO 由 ZH70809G 的 LDO4(1.8V) 供电。

-

其余引脚均为电源输入输出脚,注意 FB 需走类差分(参考设计中兼容了远近端反馈),SW 的布线短粗,输入输出电容数量,电感感值请不要随意改动,ZH70300 原理图参考图如下。

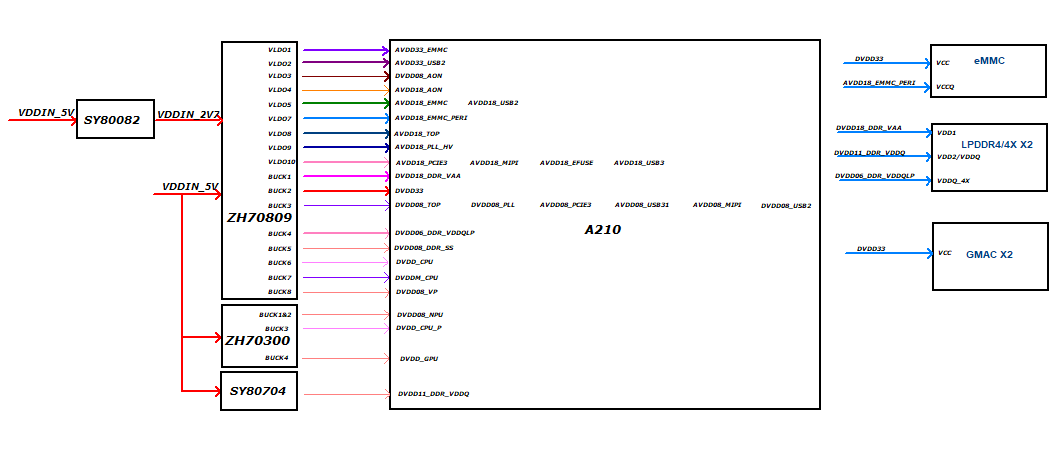

A210 PMIC 电源方案

A210+ZH70809G+ZH70300+独立 BUCK POWER TREE

POWER TREE 如下所示。

ZH70809G 上电时序

ZH70809G 上电时序已经固化,不可用其他型号替代。所有 EX-BUC K都由 ZH70209GPIO 控制。

A210+ZH70809G 上电时序表如下所示。

| Power Name | PMIC Channel | Supply Limit(mA) | Time Slot | Default Voltage | Default ON/OFF |

|---|---|---|---|---|---|

| P3V3 | SY70209-BUCK2 | 2000 | 0 | 3.3 | ON |

| P2V7 | EX-BUCK | 2000 | 0 | 2.7 | ON |

| AVDD18_AON | SY70209-LDO4 | 400 | 1 | 1.8 | ON |

| DVDD08_AON | SY70209-LDO3 | 400 | 2 | 0.8 | ON |

| AVDD18_TOP | SY70209-LDO8 | 300 | 3 | 1.8 | ON |

| AVDD18_PERI1 | |||||

| AVDD18_PERI2 | |||||

| AVDD18_PLL | SY70209-LDO9 | 300 | 4 | 1.8 | ON |

| DVDD08_TOP | SY70209-BUCK3 | 4000 | 5 | 0.8 | ON |

| DVDD08_USB2 | |||||

| DVDD08_PLL | |||||

| AVDD08_USB31 | |||||

| AVDD08_MIPI | |||||

| AVDD08_PCIE | |||||

| AVDD18_EMMC | SY70209-LDO5 | 400 | 6 | 1.8 | ON |

| AVDD18_USB2 | |||||

| AVDD18_EMMC_PERI | SY70209-LDO7 | 400 | 7 | 1.8 | ON |

| AVDD18_FLASH_PERI | |||||

| AVDD33_EMMC | SY70209-LDO1 | 400 | 8 | 3.3 | ON |

| AVDD33_USB2 | SY70209-LDO2 | 400 | 9 | 3.3 | ON |

| DVDD08_DDR | SY70209-BUCK5 | 3000 | 10 | 0.8 | ON |

| DVDD11_DDR_VDDQ | EX-BUCK | 4000 | 11 | 1.1 | ON |

| DVDD06_DDR_VDDQLP | SY70209-BUCK4 | 1500 | 12 | 0.6 | ON |

| DVDD18_DDR_VAA | SY70209-BUCK1 | 1500 | 13 | 1.8 | ON |

| DVDD_CPU | SY70209-BUCK6 | 4000 | 14 | 0.8 | ON |

| DVDDM_CPU | SY70209-BUCK7 | 1000 | 15 | 0.8 | ON |

| AVDD18_EFUSE | SY70209-LDO10 | 400 | 16 | 1.8 | ON |

| AVDD18_PCIE3 | |||||

| AVDD18_USB3 | |||||

| AVDD18_MIPI |

功耗

以下数据为各核心模块工作的峰值电流,供评估电源方案和 PCB Layout 使用,仅供参考。

注意:

SoC 的峰值电流不能全部加起来直接得出。请评估散热方案,并根据实际场景的工作平均电流进行。

| Power Name | Voltage(V) | Current(mA) |

|---|---|---|

| P3V3 | 3.3 | 1500 |

| P2V7 | 2.7 | 1500 |

| AVDD18_AON | 1.8 | 50 |

| DVDD08_AON | 0.8 | 100 |

| AVDD18_TOP | 1.8 | 300 |

| AVDD18_PERI1 | ||

| AVDD18_PERI2 | ||

| AVDD18_PLL | 1.8 | 90.27 |

| DVDD08_TOP | 0.8 | 3244.84 |

| DVDD08_USB2 | ||

| DVDD08_PLL | ||

| AVDD08_USB31 | ||

| AVDD08_MIPI | ||

| AVDD08_PCIE | ||

| AVDD18_EMMC | 1.8 | 381.98 |

| AVDD18_USB2 | ||

| AVDD18_EMMC_PERI | 1.8 | 300 |

| AVDD18_FLASH_PERI | ||

| AVDD33_EMMC | 3.3 | 31.36 |

| AVDD33_USB2 | 3.3 | 10.53 |

| DVDD08_DDR | 0.8 | 2193 |

| DVDD_CPU | 1 | 3522.68 |

| DVDDM_CPU | 1 | 300 |

| AVDD18_MIPI | 1.8 | 281.24 |

| AVDD18_USB31 | ||

| AVDD18_EFUSE | ||

| AVDD18_PCIE | ||

| AVDD18_D2D | ||

| DVDD_NPU | 1 | 2258.4 |

| DVDD_NPU_VIP | 1 | 13768.8 |

| DVDD_VP | 1 | 1500 |

| DVDD_GPU | 1 | 1419 |

| DVDD_CPU_P | 1 | 5547.9 |

| DVDD08_D2D | 0.8 | 2796.63 |

| AVDD08_D2D | ||

| AVDD18_DDR_VAA | 1.8 | 167.94 |

| AVDD18_DDR_VDD1 | ||

| DVDD12_DDR_VDDQ | 1.1 | 2017.28 |

| DVDD12_DDR_VDD2 | ||

| DVDD06_DDR_VDDQLP | 0.6 | 1250 |

| DVDD06_DDR_VDDQ |

功能接口设计指南

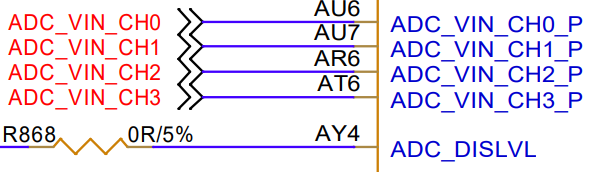

ADC 电路

概述

A210 集成了一个分辨率为 10bit 的 SAR ADC 控制器,分辨率 10/8/6 bit 可配,采样率最高 2.5MSPS,输入电压范围为 0-1.8V。ADC 具体管脚如下图。

- 提供 CH0~CH3 4 路 ADC 输入。

- ADC_DISLVL 为 ADC 控制信号,正常工作时需要拉低该信号。当需要进入深度睡眠模式或者当 AVDD18 已经上电但 DVDD08_TOP 尚未稳定时,拉高该信号,能够避免模拟电源上消耗电流。

设计建议

A210 设计需注意:

- ADC 电源的去耦电容不得删减,布局时,要靠近 A210 管脚放置。

- ADC_VIN_CH[3:0] 有使用,靠近管脚可以增加 1nF 电容消抖。

USB2.0/USB3.1 电路

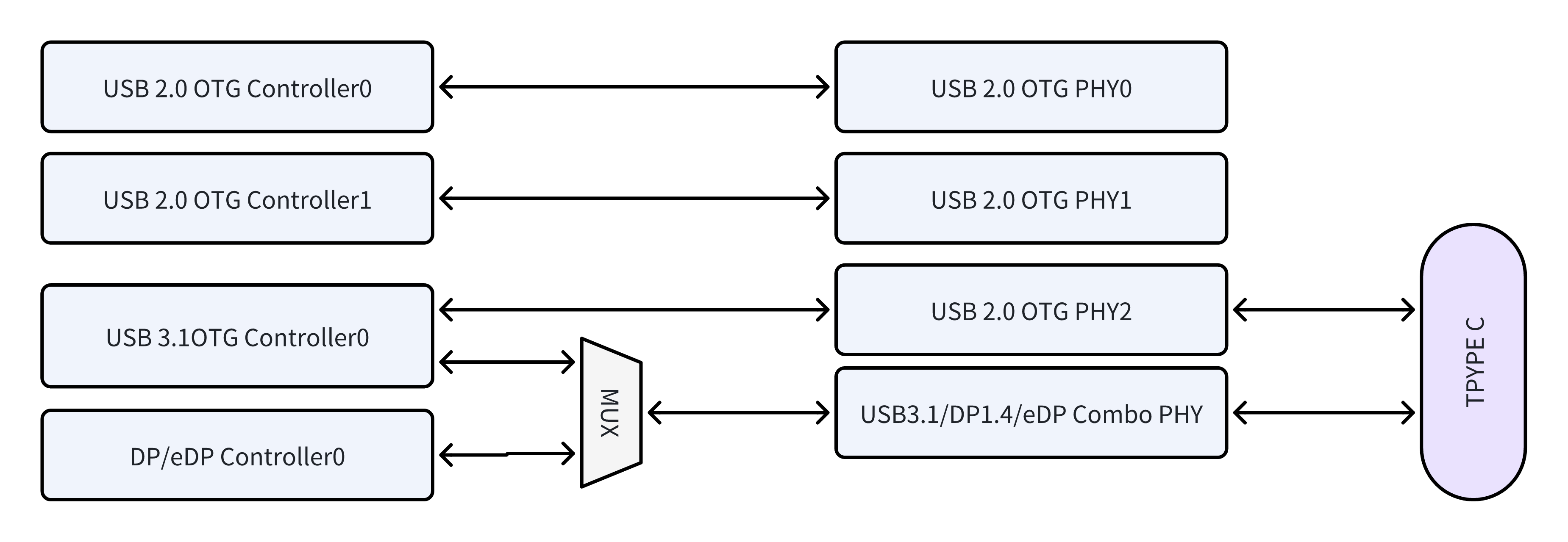

A210 芯片内置 1 个 USB3.1 控制器,2 个 USB2.0 控制器。

控制器与 PHY 的内部复用图如下。

USB2.0

概述

A210 支持两组 USB2.0 接口。

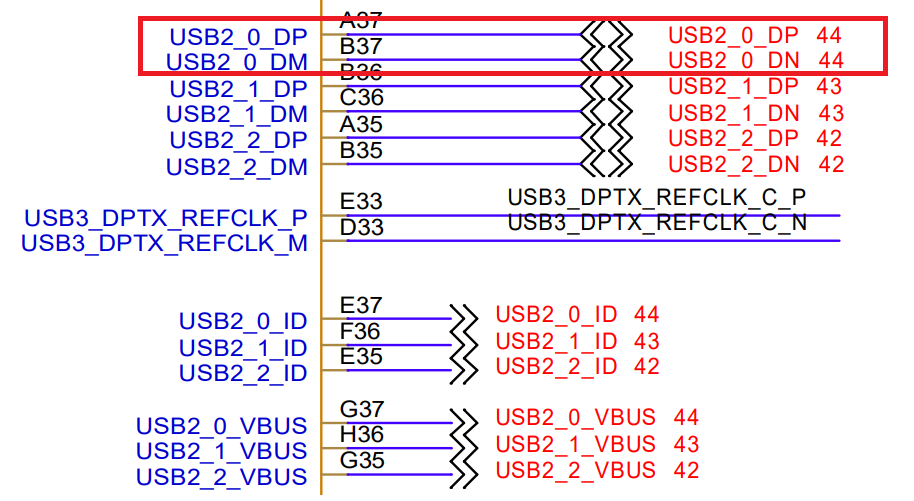

下图方框内信号组成 USB2_0 接口。

A210 支持从 USB2_0 烧录,通过 BOOT_SEL[2:0] 配置,配置如下表所示。

| BOOT_SEL[2] | BOOT_SEL[1] | BOOT_SEL[0] | BOOT MODE |

|---|---|---|---|

| 0 | 0 | 0 | USB Fastboot(先检测 CCTboot,超时 1s 则自动进入 USB Fastboot) |

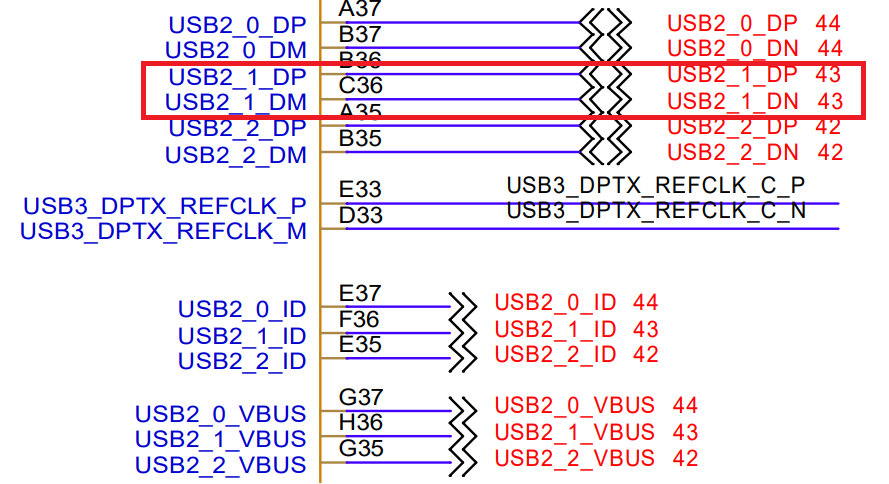

下图方框内信号组成 USB2_1 接口。

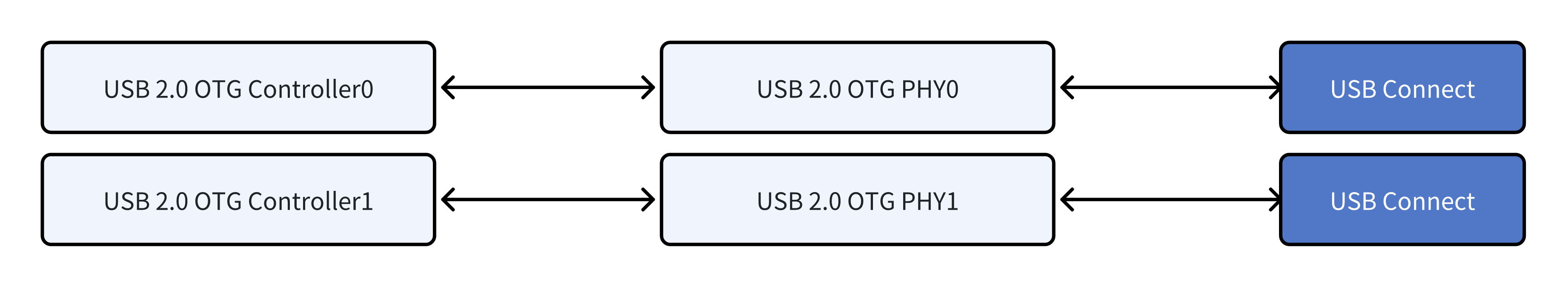

2 个 USB2.0 接口,可以直接与 USB 连接器对接,连接关系图如下。

特性

-

两组 USB2.0 均支持 OTG。

关于 OTG 可以设置以下三种模式。

-

OTG模式:软件通过识别 USB2_x_ID 脚状态切换 device 模式或 HOST 模式。ID 高为 device,ID 拉低为 HOST。

-

Device模式:该模式时,无需 USB2_x_ID 脚,只判断 USB2_x_VBUS 脚是否为高。如果为高,拉高DP,开始枚举。

-

HOST 模式:设置为这个模式时,ID 和 VBUS 状态都无需关心。

注意: USB2_x_ID 管脚的电源域为 1.8V,USB2_x_VBUS 电源域为 3.3V。

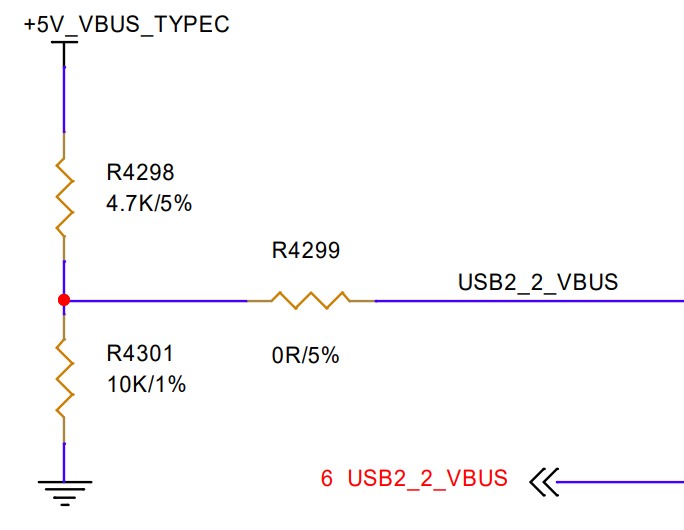

VBUS的参考电路如下。

-

-

支持唤醒功能。

-

为提高 USB 性能,PHY 各路电源的去耦电容不得删除,布局时请靠近管脚放置.

-

加强抗静电和浪涌能力设计。

-

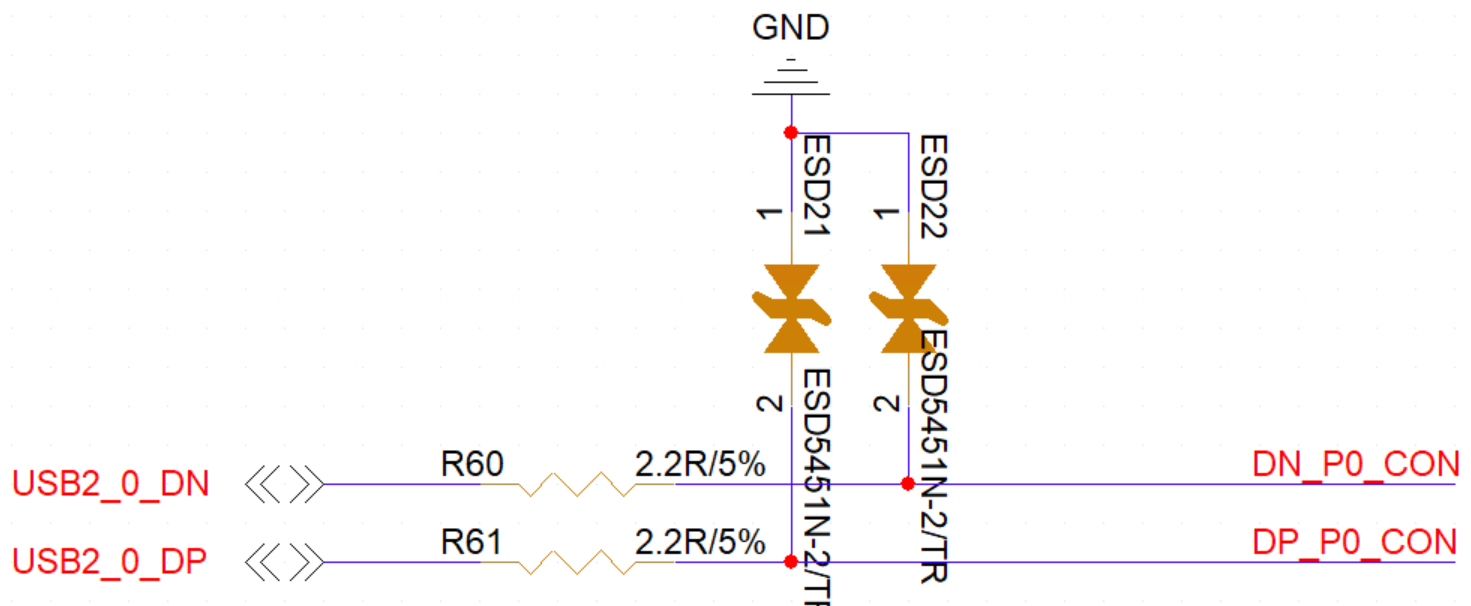

信号上必须预留 ESD 器件,USB2.0 信号的 ESD 寄生电容不得超过 3pF。

另外 USB2.0 信号的 DP/DM 串接 2.2ohm 电阻,示意图如下。

-

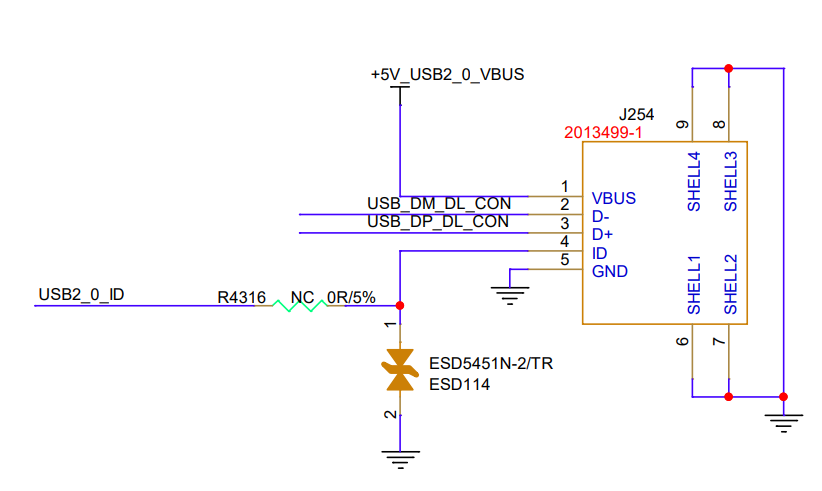

如有 USB2_x_ID 信号,信号上建议预留 ESD 器件外,且需预留串接电阻,USB2_x_ID 管脚电路如下图所示。

-

-

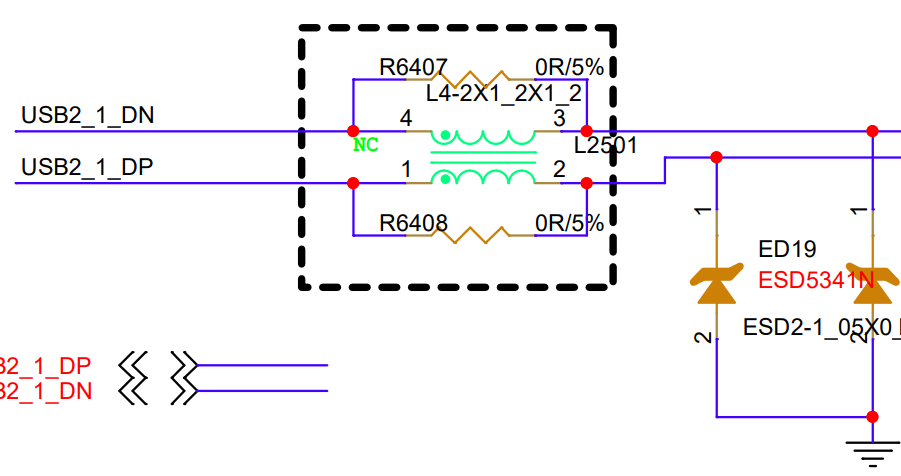

为抑制电磁辐射,可以考虑在信号线上预留共模电感,在调试过程中根据实际情况选择使用电阻或者共模电感,USB2.0 信号串接共模电感电路示意图如下。

设计建议

USB2.0 接口匹配设计推荐如下表所示。

| 信号 | 连接方式 | 说明 |

|---|---|---|

| USB2_0P | 串接 2.2ohm 电阻。 | USB2_0 USB 信号,数据输入/输出。 |

| USB2_0M | 串接 2.2ohm 电阻。 | |

| USB2_0_ID | USB OTG ID 识别,电源域为 1.8V。 | |

| USB2_0_VBUS | 电阻分压检测。 | USB OTG 插入检测。 |

| USB2_1P | 串接 2.2ohm 电阻。 | USB2_1 USB信号,数据输入/输出。 |

| USB2_1M | 串接 2.2ohm 电阻。 | |

| USB2_1_ID | USB OTG ID 识别,电源域为 1.8V。 | |

| USB2_1_VBUS | 电阻分压检测。 | USB OTG 插入检测。 |

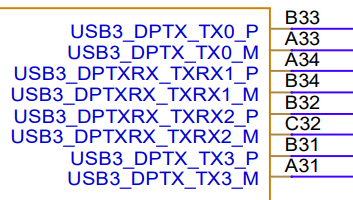

USB3.1/DP/eDP

概述

USB3.1 控制器支持 Host/Device 模式,向下兼容 USB2.0 和 USB1.1。

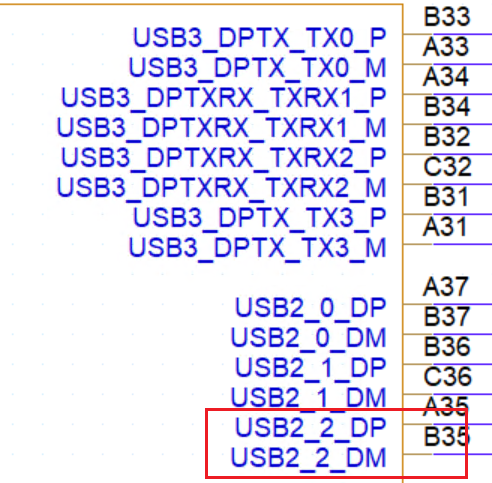

USB2.0 信号名见下图的红色方框内。

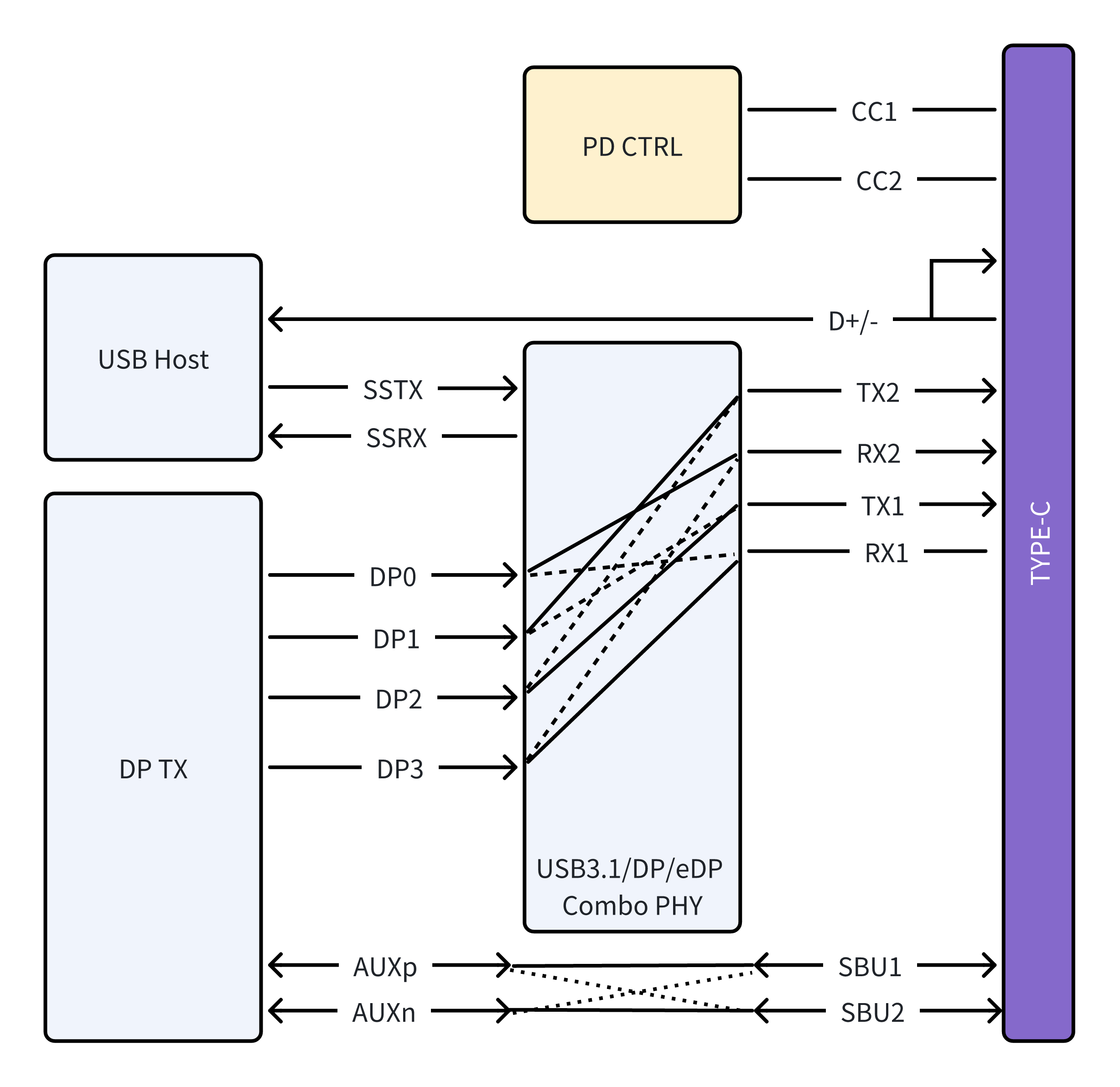

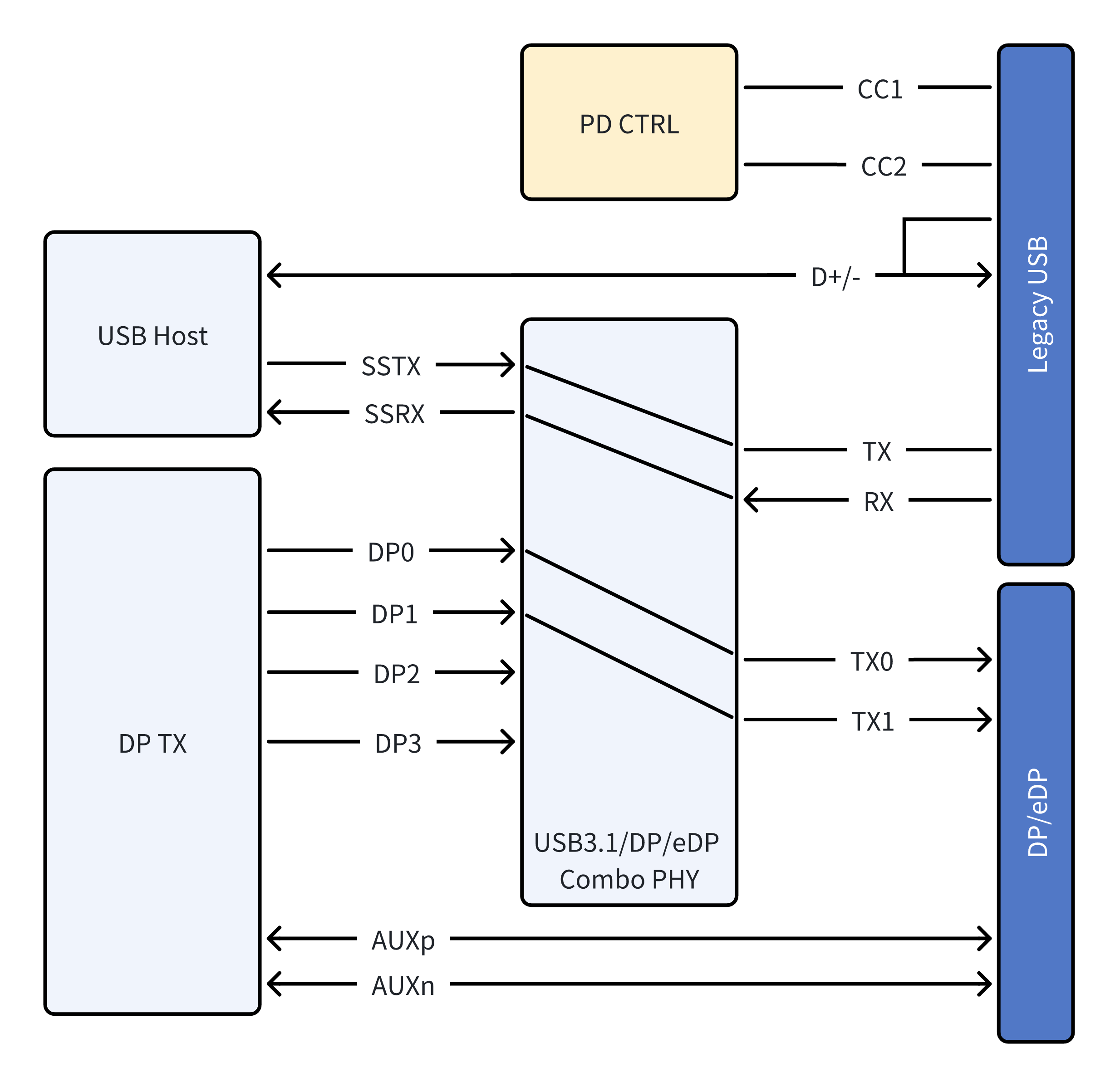

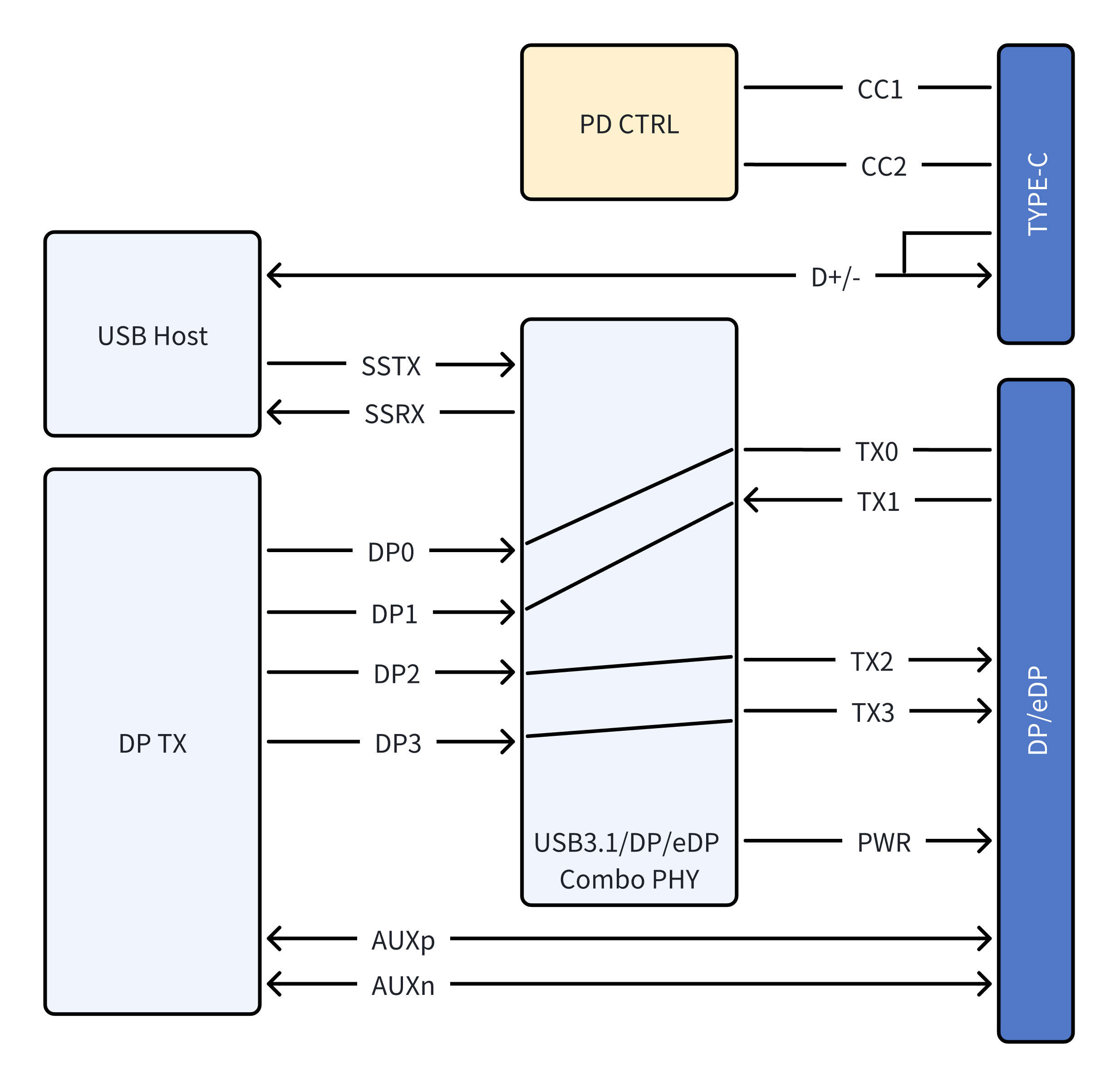

USB3.1 的 SS 信号(10Gbps)与 DP/eDP 复用,采用 USB/DP/eDP 的 Combo PHY。USB3.1 信号名如下图的红色方框内。

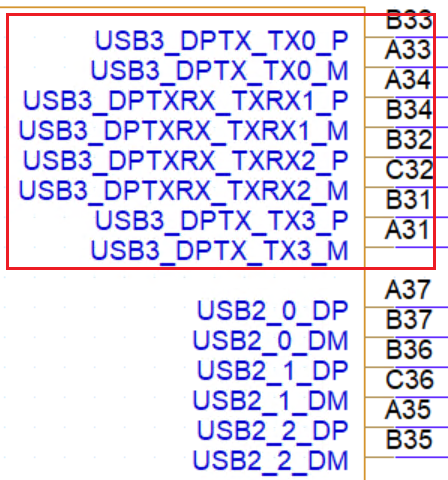

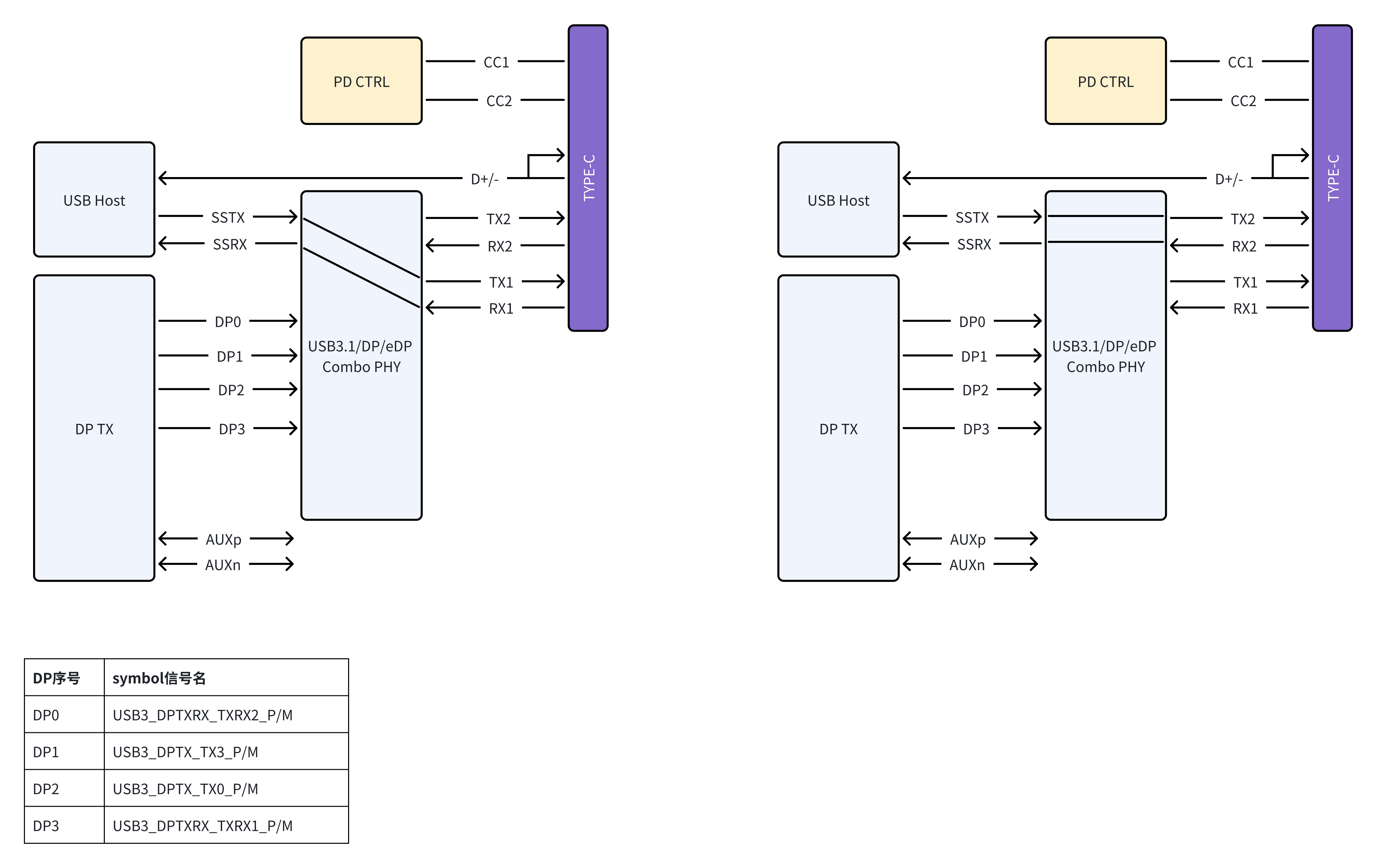

USB3.0 Controller0 和 DP1.4 Controller0 通过 USB3.0/DP1.4 的 Combo PHY0 组合成一个完整的 TYPEC 口。

USB3.1/DP1.4/eDP 的 Combo PHY 支持 Lane 间的交换(SWAP),在实际使用中,支持如下五种的配置。

说明:

连接示意图如下,端口上附加的 AC 电容、上拉电阻、USB 接口的防护电路等均未体现。详细电路可参考对应 EVB SCH。)

-

USB3.1 Only => Type-C "Normal" & "Flip"

-

USB3.1 + 2 Lane DP1.4 => Type-C (Normal - Flip shown‘dashed’)

-

USB2.0 + 4 Lane DP1.4 => Type-C (Normal - Flip shown‘dashed’)

-

USB3.1(Only) +2 Lane DP/eDP

该模式的目的为灵活配置接口资源,并最大限度地提高接口资源的利用率。

注意:

该模块不支持 Type-C 接口,若想使用,需使用外部模拟开关或者 MUX。

-

USB2.0 Only => Type-C + 4 Lane DP/eDP

该模式的目的为灵活配置接口资源,并最大限度地提高接口资源的利用率。

特性

-

由于 USB3.1 的 OTG 和 USB2_2 的 OTG 是同一个 USB3.1 的控制器,因此 USB3.1 和 USB2_2 的 OTG 只能同时做 Device 或者做 HOST。

注意 以下两种 USB OTG 模式搭配均无法实现。

- USB3.1 的 OTG 做 HOST,USB2_2 的 OTG 做 Device。

- USB3.1 的 OTG 做 Device 而 USB2_2 的 OTG 做 HOST。

-

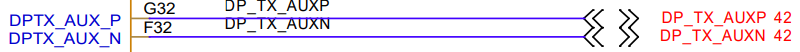

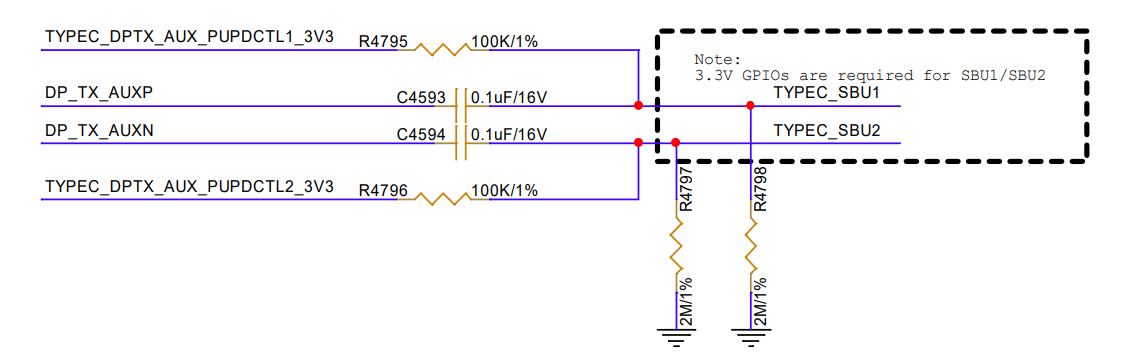

DP 接口上,还存在 DPTX_AUX_P/N,在 DP ALT Mode 下,用于传输 AUX 信号,实现 USB3.1/DP AUX PHY 的功能。AUX 信号具体 pin 脚定义如下。

默认串接 100nF 电容到 Type-C SU1/2 管脚,并分别接 100kΩ 上拉电阻到 3.3V 和 100kΩ 下拉到地的电阻。建议使用两个 3.3V 通用 IO 驱动这两个 100kΩ 电阻,根据 CC/PD 检测到的方向在 3.3V 和地之间切换,控制信号应来自 PD 控制器。当 USB3.1/DP AUX PHY 用作 UFP_D 时,板上要驱动的两个电阻为 1MΩ。AUX 参考电路如下。

-

TYPEC 座子所有信号都必须增加 ESD 器件,布局时靠近 USB 连接器放置。对于 SSTXP/N、SSRXP/N 信号,ESD 寄生电容不得超过 0.3pF。

设计建议

USB3.1/DP/eDP 接口匹配设计推荐如下表所示。

| 信号 | 连接方式 | 说明 |

|---|---|---|

| USB2_2P | 串接 2.2ohm 电阻。 | USB2.0 信号,数据输入/输出。 |

| USB2_2M | 串接 2.2ohm 电阻。 | |

| USB3_DPTX_TX0_P | 串接 100nF 电容。 | USB3.1 TX 信号或者DP/eDP TX 信号。 |

| USB3_DPTX_TX0_M | 串接100nF电容。 | |

| USB3_DPTXRX_TXRX1_P | 串接 0ohm 电阻。 | USB3.1 RX 信号或者 DP/eDP RX/TX 信号。 |

| USB3_DPTXRX_TXRX1_M | 串接 0ohm 电阻。 | |

| USB3_DPTXRX_TXRX2_P | 串接 0ohm 电阻。 | USB3.1 RX 信号或者 DP/eDP RX/TX 信号。 |

| USB3_DPTXRX_TXRX2_M | 串接 0ohm 电阻。 | |

| USB3_DPTX_TX3_P | 串接 100nF 电容。 | USB3.1 TX 信号或者 DP/eDP TX 信号。 |

| USB3_DPTX_TX3_M | 串接 100nF 电容。 | |

| USB_DPTX_REFCLK_P | 悬空。 | |

| USB_DPTX_REFCLK_M | ||

| DPTX_AUX_P | 串接 100nF 电容到 Type-C SU1/2 管脚。并通过 100K 电阻接到 3.3V IO 上,用于根据 CC/PD 检测到的方向在 3.3V 和地之间切换。 | 用于 DP Alt Mode,接 TypeC SU1/2,进行视频信号传输等操作。 |

| DPTX_AUX_N | ||

| USB2_2_ID | USB OTG ID 识别,电源域为 1.8V。 | |

| USB2_2_VBUS | 电阻分压检测。 | USB OTG 插入检测。 |

SATA 电路

特性

A210 芯片拥有 2 个 SATA3.0 控制器,SATA3.0 支持如下特性。

- 支持 SATA PM 功能。

- 支持 SATA 1.5Gb/s,SATA 3.0Gb/s,SATA 6.0Gb/s speeds。

- 支持唤醒功能。

Pin 脚定义/IO 复用关系

SATA3.0 接口和 PCIE 复用,复用关系如下表:

| PHY | PHY0(x2) | PHY1(x2) | |||

| lane# | 0 | 1 | 2 | 3 | |

| 产品配置 | 配置编号 | 配置 | |||

| 1 | PCIE x4 (PCIE DM) | ||||

| 2 | PCIE x2(PCIE_DM) | PCIE x1(PCIE_RP) | N/A | ||

| 3 | PCIE x2(PCIE_RP) | x2(SATA) | |||

| 4 | PCIE x1(PCIE_DM) | PCIE x1(PCIE_RP) | x2(SATA) | ||

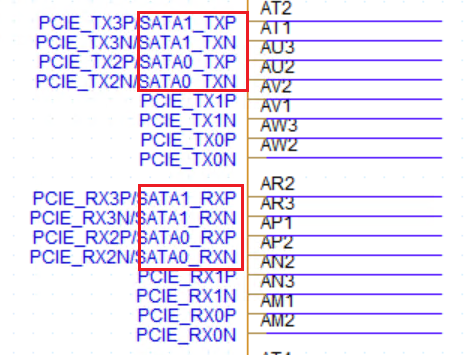

SATA0 和 SATA1 相关 Pin 定义如下。

SATA 控制器相关的控制 IO 如下。如下控制通过 IO 复用实现,所有 IO 的电源域均为 1.8V,设计时注意电平匹配。

- SATA_Px_DEVSLP:SATAx device sleep 控制管脚,通过其高低电平让 SSD 进出低功耗。

- SATA_Px_MP_SWITCH:SATAx 热拔插设备的开关检测输入。

- SATA_Px_CP_DET:SATAx 热拔插设备的插拔检测输入。

- SATA_Px_CP_POD:SATAx控制热拔插设备电源开关输出。

- SATA_Px_ACT_LED:SATAx 接口有数据传输时 LED 闪烁控制输出。

设计建议

SATA 设计中注意事项如下。

- Slot 设计时,外围电路及电源需满足 Spec 要求。

- SATA 接口的 TXP/N,RXP/N 差分信号上串接的 10nF 交流耦合电容,AC 耦合电容建议使用 0201 封装,更低的 ESR 和 ESL,也可减少线路上的阻抗变化。

- eSATA 接口座子所有信号都必须增加 ESD 器件,布局时靠近座子放置,ESD 寄生电容不得超过 0.4pF。

SATA 接口匹配设计推荐如下表所示。

| 信号 | 连接方式 | 说明 |

|---|---|---|

| PCIE_RX2N/SATA0_RXN | 串接 10nF 电�容。 | SATA0 信号输入。 |

| PCIE_RX2P/SATA0_RXP | 串接 10nF 电容。 | SATA0 信号输入。 |

| PCIE_TX2N/SATA0_TXN | 串接 10nF 电容。 | SATA0 信号输出。 |

| PCIE_TX2P/SATA0_TXP | 串接 10nF 电容。 | SATA0 信号输出。 |

| PCIE_SATA_0_REFCLK_P/M | 100M 时钟。 | SATA0 参考时钟。 |

| PCIE_RX3N/SATA1_RXN | 串接 10nF 电容。 | SATA1 信号输入。 |

| PCIE_RX3P/SATA1_RXP | 串接 10nF 电容。 | SATA1 信号输入。 |

| PCIE_TX3N/SATA1_TXN | 串接 10nF 电容。 | SATA1 信号输出。 |

| PCIE_TX3P/SATA1_TXP | 串接 10nF 电容。 | SATA1 信号输出。 |

| PCIE_SATA_1_REFCLK_P/M | 100M 时钟。 | SATA1 参考时钟。 |

PCIe 电路

配置

A210 芯片拥有 2 个 PCIe 控制器,支持 PCIe 3.1/2.1/1.1,均为2lane。

PCIE PHY 与 SATA PHY 相互组合后,共有如下 4 种配置。(DM:Dual Mode,RP:Root Port)

| PHY | PHY0(x2) | PHY1(x2) | |||

| lane# | 0 | 1 | 2 | 3 | |

| 产品配置 | 配置编号 | 配置 | |||

| 1 | PCIE x4 (PCIE DM) | ||||

| 2 | PCIE x2(PCIE_DM) | PCIE x1(PCIE_RP) | N/A | ||

| 3 | PCIE x2(PCIE_RP) | x2(SATA) | |||

| 4 | PCIE x1(PCIE_DM) | PCIE x1(PCIE_RP) | x2(SATA) | ||

- 2 个 2lane PCIE3.0 PHY ��组合为 PCIe 3.0 x4 DM模式.

- 1 个 2lane PCIE3.0 DM模式 + 1个 PCIe 3.0 x1 RP模式。

- 1 个 2lane PCIE3.0 DM模式 + 2个SATA。

- 1 个 PCIe 3.0 x1 DM 模式 + 1个 PCIe 3.0 x1 RP 模式 + 2 个 SATA。

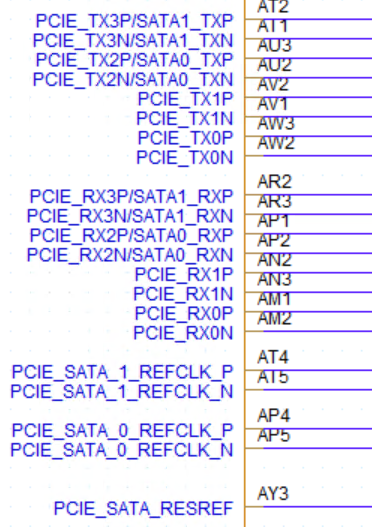

Pin 脚定义

PCIEX4_TYPE 管脚,用于 PCIE 模式选择。

![]()

具体说明及设计建议见下表。

| 信号 | 功能说明 | 设计建议 |

|---|---|---|

| PCIEX4_TYPE | PCIE TYPE选择如下。 0:EP,1:RC | 按需选择 |

PCIe 相关信号 pin 信息如下图。

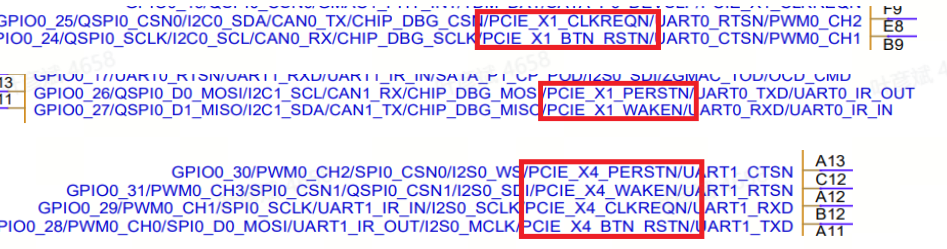

除此以外,PCIe 还有 BTN_RSTN,CLKREQN,PERSTN,WAKE 4个边带信号,功能均为通过GPIO复用实现。如下图所示,这些 IO 电源域均为 1.8V。

PCIe 相关 Pin 脚信息,连接方式及说明如下表。

| 信号 | 连接方式 | 说明 |

|---|---|---|

| PCIE_TX0/1N/P | 串接 220nF 电容。 | PCIe 数据输出。 |

| PCIE_RX0/1N/P | 直连。 | PCIe 数据输入。 |

| PCIE_TX2/3N/P | 串接 220nF 电容。 | PCIe 数据输出,SATA 时作为 SATA0/1 的数据输出。 |

| PCIE_RX2/3N/P | 直连。 | PCIe 数据输出,SATA 时作为 SATA0/1 的数据输入。 |

| PCIE_SATA_0_REFCLK_P/M | 100M 时钟。 | PCIe0 参考时钟。 |

| PCIE_SATA_1_REFCLK_P/M | 100M 时钟。 | PCIe1 参考时钟。 |

| PCIE_SATA_RESREF | 200ohm 到地。 | 外置参考电阻管脚。 |

| PCIE_X1/4_CLKREQN | 串接 0ohm,IO 为 1.8V,注意电平匹配,必要时增加电平转换电路。 | PCIe 参数时钟请求输出。 |

| PCIE_X1/4_PERSTN | 串接 0ohm,IO 为 1.8V,注意电平匹配,必要时增加电平转换电路。 | PCIe 全局复位输出(RC 模式)PCIe 全局复位输入(X4 EP 模式)。 |

| PCIE_X1/4_WAKEN | 串接 0ohm,IO 为 1.8V,注意电平匹配,必要时增加电平转换电路。 | PCIe 唤醒输出(EP 模式)。 |

| PCIE_X1/4_BTN_RSTN | 预留。 | PCIe 外部硬件复位管脚,低有效。拉低 PCIe 复位。 |

设计建议

设计中需要注意:

- Slot 设计时,外围电路及电源需要满足 Spec 要求。

- PCIe 接口的 TXP/N 差分信号上串接的 220nF 交流耦合电容,AC 耦合电容建议使用 0201 封装,更低的 ESR 和 ESL,也可减少线路上的阻抗变化。

- PCIE_X4_BTN_RSTN,PCIE_X4_CLKREQN,PCIE_X4_PERSTN,PCIE_X4_WAKE,PCIE_X1_BTN_RSTN,PCIE_X1_CLKREQN,PCIE_X1_PERSTN,PCIE_X1_WAKE 均为1.8V IO。设计中需要注意电平匹配,对接其他电平需使用电平转换。

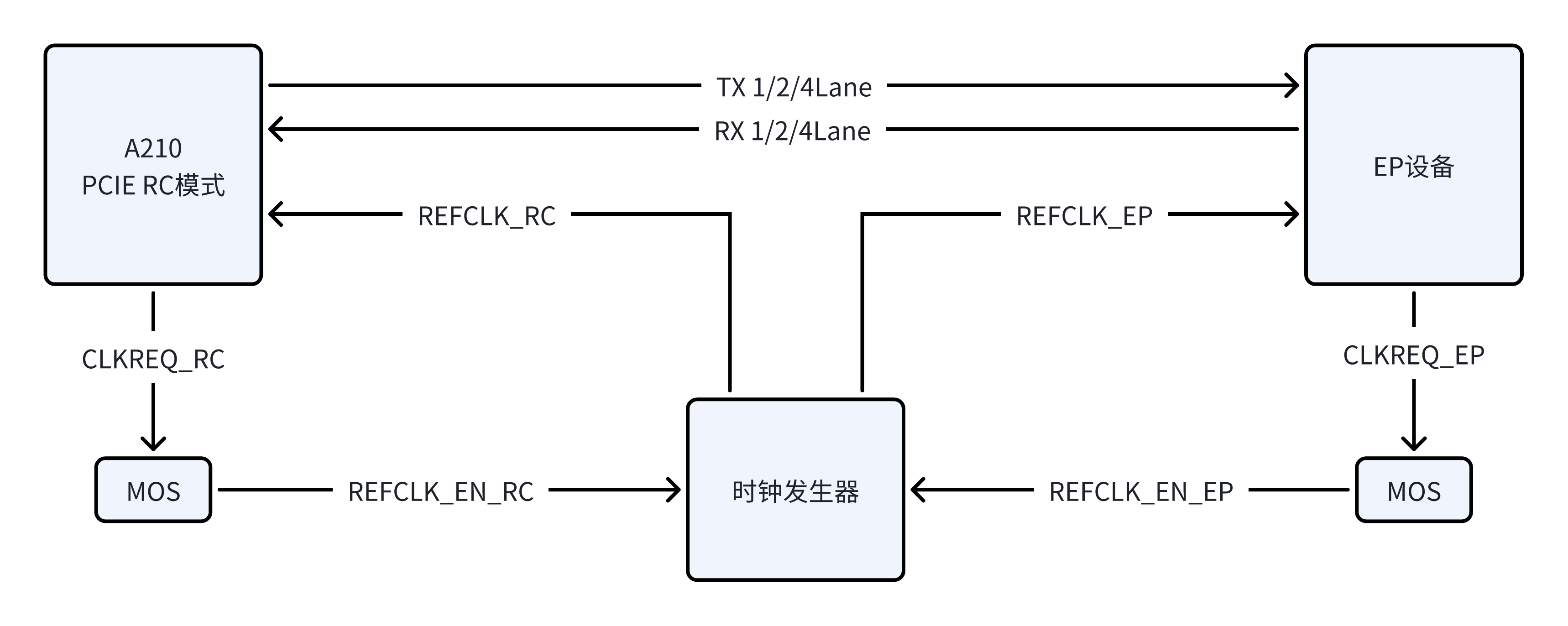

- 当 PCIE 用作 RC 模式时,CLKREQ 信号作为输出,正常工作时拉低,这是给 PCIE_SATA_0/1_REFCLK 提供时钟。同时当 EP 设备拉低 CLKREQ_EP 时,表示 EP 设备向 RC 请求 PCIe 参考时钟,这是需要向 EP 设备提供 100MHz 时钟。建议参考如下设计。

-

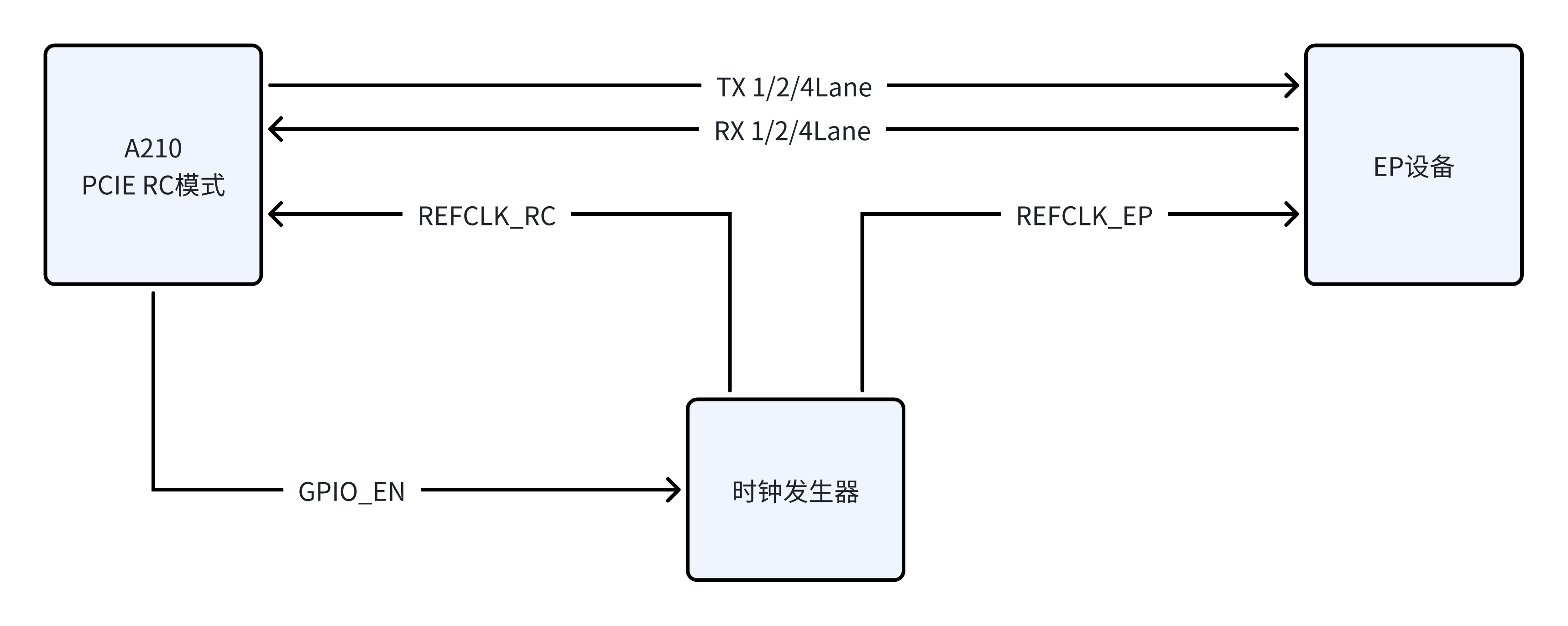

若对成本有一定要求,CLKREQN 信号也可以不做连接,使用一个普通 GPIO 作为时钟发生器的使能,系统起来后直接控制时钟输出,参考如下:

-

当 PCIE 用作 EP 模式时,CLKREQ 信号初始时作为 PCIe 参考时钟请求输出,拉低来向 RC 设备请求时钟。

-

PERST 信号为 PCIe 全局复位信号,拉低有效,作为 PCIe 全局复位。当有效时,EP 设备使用该信号复位内部逻辑。

-

WAKEN 信号为唤醒信号,仅在 EP 模式下有效,为输出,低有效。主要用于当 EP 进入休眠模式后,可以通过 WAKE 信号向 RC 提交唤醒请求。WAKEN为 可选信号。用作 RC 模式时,若要使用 WAKEN 功能,可以选择 AON 管脚作为唤醒 IO。

-

BTN_RSTN 外部硬件复位管脚,拉低有效。设计可以预留。

视频输入接口电路

MIPI DPHY CSI 接口

概述

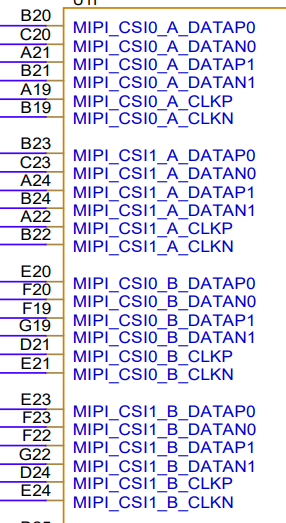

A210 有两个 MIPI DPHY CSI RX,都支持 MIPI V1.2 版本,每个通道最大数据传输速率为 2.5Gbps。

- 支持4x2lane,2x4lane,1x4lane + 2x2lane。

- 支持8/10/12/16 bit 位宽。

- 支持 4 路 1080P@30fps,1x4K@30fps,2x1080P@60fps 输入。

- 支持最大输入分辨率 12M Pixel。

MIPI DPHY CSI0 RX 接口模式支持情况。

-

支持 x4Lane 模式,MIPI_CSI0_A/B_DATA0[1:0] 数据参考 MIPI_CSI0_A_CLK。

-

支持 x2Lane + x2Lane 模式。

- MIPI_CSI0_A_DATA0[1:0],数据参考MIPI_CSI0_A_CLK。

- MIPI_CSI0_B_DATA0[1:0],数据参考MIPI_CSI0_B_CLK。

CSI0 RX 接口各个模式 Lane 和 CLK 的分配情况及参考如下表所示。

| Option1 | sensor1 x4 Lane | MIPI_CSIO_A_DATA0/1 MIPI_CSIO_B_DATA0/1 MIPI_CSIO_A_CLK |

| Option2 | sensor1 x2 Lane | MIPI_CSI1_A_DATA0/1 MIPI_CSI1_A_CLK |

| sensor2 x2 Lane | MIPI_CSI1_B_DATA0/1 MIPI_CSI1_B_CLK |

MIPI DPHY CSI1 RX 接口模式支持情况如下。

-

支持 x4Lane 模式,MIPI_CSI1_A/B_DATA0[1:0] 数据参考 MIPI_CSI1_A_CLK。

-

支持 x2Lane + x2Lane 模式。

- MIPI_CSI1_A_DATA0[1:0],数据参考MIPI_CSI1_A_CLK。

- MIPI_CSI1_B_DATA0[1:0],数据参考MIPI_CSI1_B_CLK。

CSI0 RX 接口各个模式 Lane 和 CLK 的分配情况及参考如下表所示。

| Option1 | sensor1 x4 Lane | MIPI_CSI1_A_DATA0/1 MIPI_CSI1_B_DATA0/1 MIPI_CSI1_A_CLK |

| Option2 | sensor1 x2 Lane | MIPI_CSI1_A_DATA0/1 MIPI_CSI1_A_CLK |

| sensor2 x2 Lane | MIPI_CSI1_B_DATA0/1 MIPI_CSI1_B_CLK |

设计建议

MIPI CSI0/1 RX 设计中请注意:

- 为提高 MIPI CSI0/1 RX 性能,PHY 各路电源的去耦电容不得删除,布局时请靠近管脚放置:涉及电源有 DVDD08_TOP,AVDD08_MIPI,AVDD18_MIPI。

- 当通过连接器实现板对板连接时,预留 TVS 器件。

MIPI DPHY CSI0/1 RX 接口匹配设计推荐如下表所示。

| 信号 | 连接方式 | 说明 |

|---|---|---|

| MIPI_CSI0_A_DATAP/N0 | 直连 | MIPI CSI0 数据 Lane0 输入。 |

| MIPI_CSI0_A_DATAP/N1 | 直连 | MIPI CSI0 数据 Lane1 输入。 |

| MIPI_SCI0_A_CLKP/N | 直连 | MIPI CSI0 时钟 0 输入。 |

| MIPI_CSI0_B_DATAP/N0 | 直连 | MIPI CSI0 数据 Lane2 输入。 |

| MIPI_CSI0_B_DATAP/N0 | 直连 | MIPI CSI0 数据 Lane3 输入。 |

| MIPI_SCI0_B_CLKP/N | 直连 | MIPI CSI0 时钟 1 输入。 |

| MIPI_CSI1_A_DATAP/N0 | 直连 | MIPI CSI1 数据 Lane0 输入。 |

| MIPI_CSI1_A_DATAP/N0 | 直连 | MIPI CSI1 数据 Lane1 输入。 |

| MIPI_SCI1_A_CLKP/N | 直连 | MIPI CSI1 时钟 0 输入。 |

| MIPI_CSI1_B_DATAP/N0 | 直连 | MIPI CSI1 数据 Lane2 输入。 |

| MIPI_CSI1_B_DATAP/N0 | 直连 | MIPI CSI1 数据 Lane3 输入。 |

| MIPI_SCI1_B_CLKP/N | 直连 | MIPI CSI1 时钟 1 输入。 |

视频输出接口电路

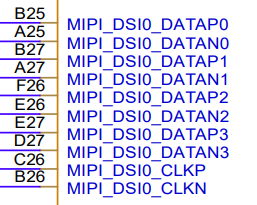

MIPI DPHY DSI 接口

概述

A210 支持 1 个 4Lane DSI TX,支持 MIPI V1.2 版本,每个通道最大数据传输速率为 2.5Gbps。支持 4K@60fps 输出。

设计建议

MIPI DSI TX 设计中请注意:

- 为提高 MIPI DSI TX 性能,PHY 各路电源的去耦电容不得删除,布局时请靠近管脚放置;涉及电源有 DVDD08_TOP,AVDD08_MIPI,AVDD18_MIPI。

- 当通过连接器实现板对板连接时,预留 TVS 器件。

MIPI DPHY DSI TX 接口匹配设计推荐如下表所示。

| 信号 | 连接方式 | 说明 |

|---|---|---|

| MIPI_DSI0_DATAP/N0 | 直连 | MIPI DSI 数据 Lane0 输出。 |

| MIPI_DSI0_DATAP/N1 | 直连 | MIPI DSI 数据 Lane1 输出。 |

| MIPI_DSI0_DATAP/N2 | 直连 | MIPI DSI 数据 Lane2 输出。 |

| MIPI_DSI0_DATAP/N3 | 直连 | MIPI DSI 数据 Lane3 输出。 |

| MIPI_DSI0_CLKP/N | 直连 | MIPI DSI 时钟输出。 |

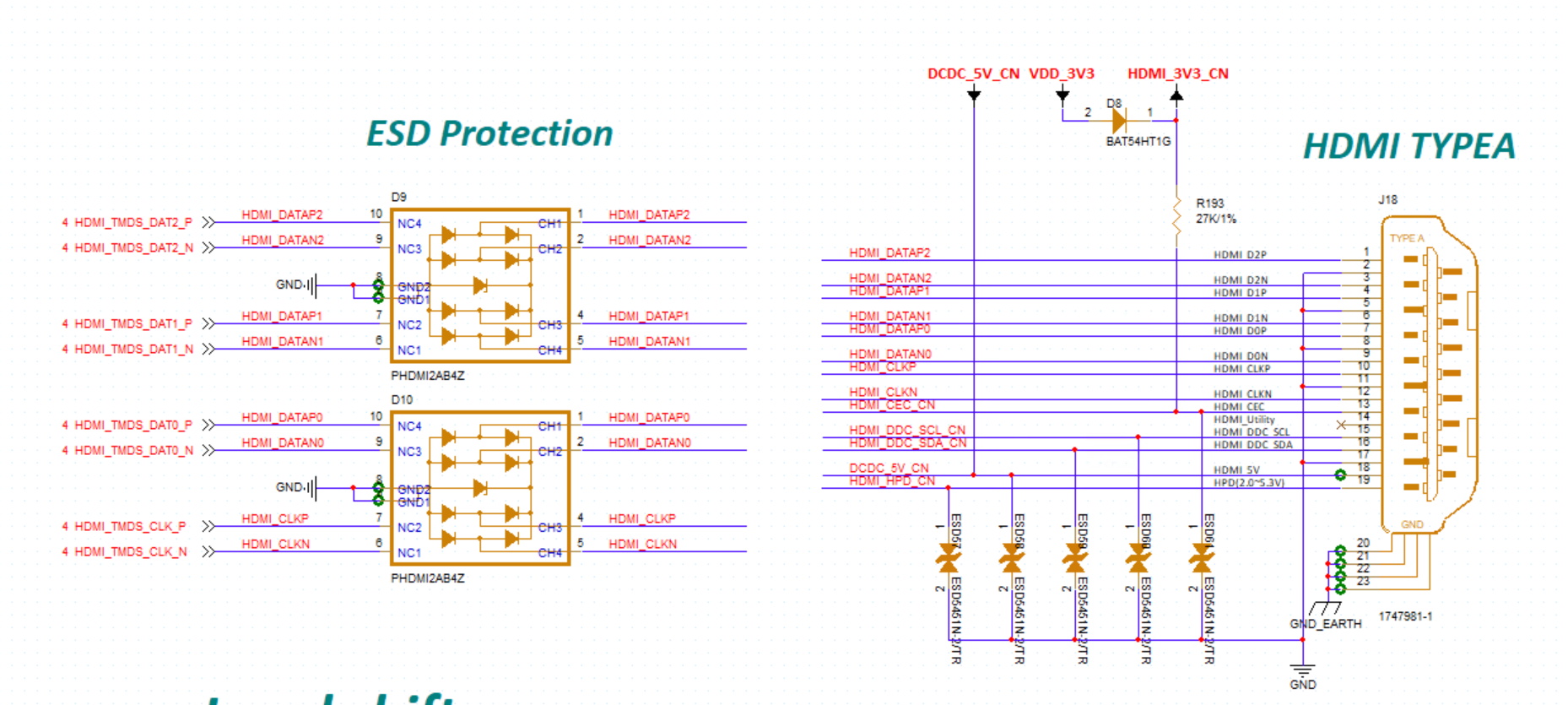

HDMI TX 接口

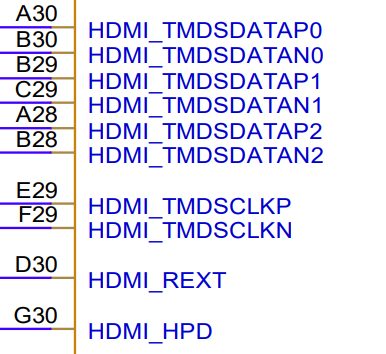

A210 内置 1 个 HDMI TX PHY,支持 HDMI2.0 版本。

- 支持 4K@60fps 输出。

- 支持 HDCP 1.4。

- 支持音频输出。

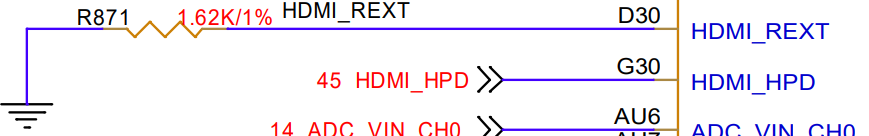

HDMI_HPD 为热拔插检测管脚,电源域为 1.8V。由于在 HDMI 接口中,HPD 的高电平为 2.0~5.3V,所以需要增加电平转换电路。

HDMI_REXT 是 HDMI PHY 的外置参考电阻管脚,外接对地 1.62Kohm 精度为 1% 的电阻,不得更改电阻值,布局时靠近 A210 芯片管脚放置。

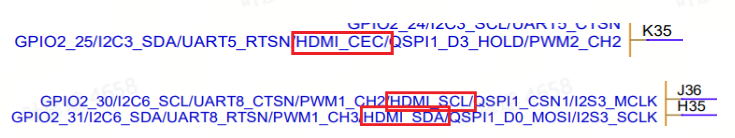

HDMI 还有 HDMI_CEC,HDMI_SCL,HDMI_SDA 等辅助管脚,功能复用在 GPIO 上,具体 HDMI 信号辅助管脚如下图。

HDMI_CEC 是 HDMI 控制器 CEC 功能复用到普通 GPIO 上功能,电平为 1.8V,CEC 协议规定是 3.3V 电平,但是协议要求,往 CEC 管脚通过 27K 电阻加 3.3V 电压,漏电不允许超过 1.8uA。

IO Domain 在未上电时,如果 IO 上有电压,IO 会存在漏电,比如 A210 已经断电了,HDMI 线还连接着 Sink 端(电视或显示器),此时 Sink 端的 CEC 会通过 HDMI 线漏电到 A210 IO 上,会造成 CEC 漏电超过 1.8uA,因此外部需要增加一个隔离电路,CEC 电路参考如下。

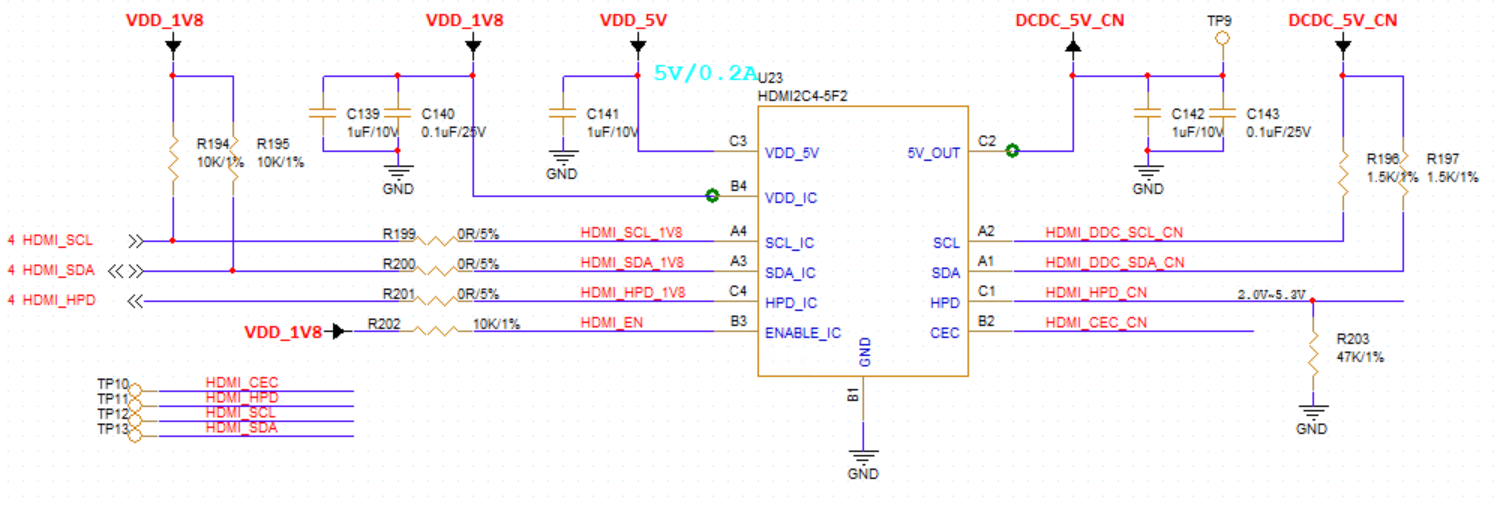

HDMI_SCL,HDMI_SDA 是 HDMI TX 控制器的 I2C/DDC 总线。协议规定是 5V 电平,必须增加电平转换电路,不得删减。

参考设计中,HDMI 相关辅助信号采用了 HDMI2C-5F2 进行电平转换和电源控制,HDMI 辅助信号参考电路如下。

为加强抗静电能力,信号上必须预留 ESD 器件,HDMI2.0 信号的 ESD 寄生电容不得超过 0.2pF,其它信号的 ESD 寄生电容建议使用不超过 1pF。

HDMI TX 接口匹配设计推荐如下表所示。

| 信号 | 连接方式 | 说明 |

|---|---|---|

| HDMI_TMDSDATAP/N0 | 直连。 | TMDS 数据 Lane0。 |

| HDMI_TMDSDATAP/N1 | 直连。 | TMDS 数据 Lane1。 |

| HDMI_TMDSDATAP/N2 | 直连。 | TMDS 数据 Lane2。 |

| HDMI_TMDSCLKP/N | 直连。 | TMDS 时钟。 |

| HDMI_REXT | 对地 1.62Kohm 精度为 1% 的电阻。 | 外置参考电阻。 |

| HDMI_HPD | HDMI2C-5F2 转换。 | 热拔插检测。 |

| HDMI_CEC | MOS 隔离。 | CEC 信号。 |

| HDMI_SCL | HDMI2C-5F2 转换。 | DDC 时钟。 |

| HDMI_SDA | HDMI2C-5F2 转换。 | DDC 数据输入输出。 |

DP/eDP �接口

概述

A210 支持 1 个 DP1.4/eDP1.5 TX PHY(和 USB3.1 Combo),最大输出分辨率可达 4K@60fps。

- 每个 Lane 速率可支持 1.62/2.7G/5.4/8.1Gbps。

- 支持 2Lane 或 4Lane 输出。

- 支持唤醒功能。

- 支持音频输出。

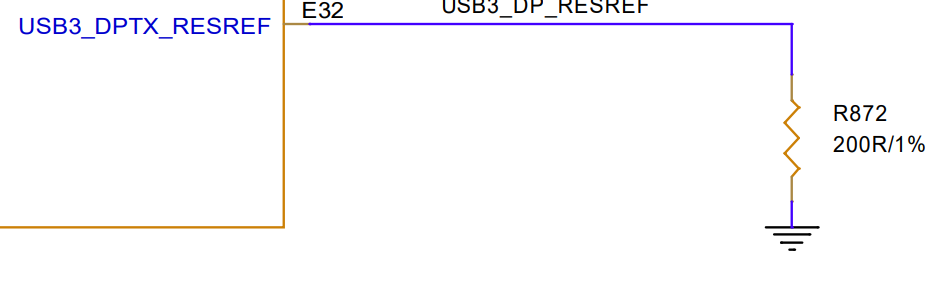

设计建议

DP/eDP TX PHY 设计中请注意。

- TX 线对需要串接的 100nF 交流耦合电容,交流耦合电容建议使用 0201 封装,更低的 ESR 和 ESL,也可减少线路上的阻抗变化,布局时,靠近 A210 管脚放置。

- USB3_DPTX_RESREF 是 USB DP Combo PHY 的外置参考电阻管脚,外接对地 200ohm 精度为 1% 的电阻,不得更改电阻值,布局时靠近 A210 芯片管脚放置。

DP0/1 TX PHY 接口匹配设计推荐如下表所示。

| 信号 | 连接方式 | 说明 |

|---|---|---|

| USB3_DPTX_TX0_P | 串接 100nF 电容。 | DP/eDP Lane0 输出。 |

| USB3_DPTX_TX0_M | 串接 100nF 电容。 | |

| USB3_DPTXRX_TXRX1_P | 串接 100nF 电容。 | DP/eDP Lane1 输出。 |

| USB3_DPTXRX_TXRX1_M | 串接 100nF 电容。 | |

| USB3_DPTXRX_TXRX2_P | 串接 100nF 电容。 | DP/eDP Lane2 输出。 |

| USB3_DPTXRX_TXRX2_M | 串接 100nF 电容。 | |

| USB3_DPTX_TX3_P | 串接 100nF 电容。 | DP/eDP Lane3 输出。 |

| USB3_DPTX_TX3_M | 串接 100nF 电容。 | |

| USB_DPTX_REFCLK_P | 悬空。 | |

| USB_DPTX_REFCLK_M | ||

| DPTX_AUX_P | 串接 100nF 电容到 Type-C SU1/2 管脚。并通过 100K 电阻接到 3.3V IO 上,用于根据 CC/P D检测到的方向在 3.3V 和地之间切换。 | DP AUX 通道。 |

| DPTX_AUX_N |

LCD屏和触摸屏设计注意点

- LED 背光升压 IC 的 FB 端限流电阻,请选用 1% 精度电阻,并按功率需求选择合适的封装尺寸。

- LED 背光升压 IC 的 EN/PWM 管脚,选择内部下拉的 GPIO,外接下拉电阻,避免上电时出现闪屏现象。

- LED 背光的驱动电压输出,请选择合适额定电压的滤波电容。

- LED 背光升压电路的肖特基二极管请根据工作电流选择合适的型号,并注意二极管的反向击穿电压,避免在空载时反向击穿。

- LED 背光升压电路的电感请根据实际型号匹配感量,饱和电流,DCR 等。

- 屏和触摸屏的信号电平要与芯片的 IO 驱动电平匹配,如 RST/Stand by 等信号。

- 屏的电源必须可控制,上电时,默认不提供。

- 屏和触摸屏的去耦电容不得删减,必须保留。

- TP 的 I2C 总线�必须加 2.2K 上拉到 VCC3V3_TP 电源,建议不和其它设备共用总线,如果一定要共用,注意上拉电源和地址是否冲突。

- 带 Charge pump 的 TP IC,请注意电容的额定电压。

- 对于屏,当通过 FPC 与板连接时,建议串接一定阻值的电阻(22ohm-100ohm 之间,具体以能满足SI 测试为准),并预留 TVS 器件。

- 串行接口的屏在接口处建议预留共模电感。

音频相关电路设计

A210 总共提供了 4 组 I2S 接口、1 组 PDM 接口。

I2S

概述

A210 总共提供了 4 组 I2S 接口,I2S 作为应用最广泛的数字音频接口,可用于音频 ADC、音频 DAC、音频 Codec、DSP 等外设的通讯,也可为视频输入/输出接口提供集成的音频输入与输出支持。

其中 I2S3 是支持 8 通道输入/输出能力的标准 I2S 接口,I2S0、I2S1、I2S2是支持 2 通道输入/输出能力的标准 I2S 接口。

I2S3支持如下特性。

- 支持 8 通道输入输出。

- 支持 RX/TX 全双工。

- 支持最高 384KHz 采样率。

- 支持主从模式。

- 支持采样精度 16 至 32bits。

- 支持 3 种 I2S 格式(常规、左对齐、右对齐)。

- 支持 PCM 模式秒支持标准和自定义两种模式(帧同步信号仅支持短脉冲同步信号,同步信号的持续时间为 1 个时钟周期)。

I2S0/1/2 支持如下特性。

- 支持2通道输入输出。

- 支持RX/TX全双工。

- 支持最高384KHz采样率。

- 支持主从模式。

- 支持采样精度 16 至 32bits。

I2S 接口输出数据 SDOx 和输入数据 SDIx,同时参考一组位/帧时钟 SCLK/WS。

设计建议

I2S上IO的分布及设计推荐如下。

| 信号 | 电源域 | 连接方式 | 描述 |

|---|---|---|---|

| I2S0_MCLK | AVDD18_PERI1 | 串接 22ohm 电阻。 | I2S 系统时钟输出。 |

| I2S0_SCLK | 串接 22ohm 电阻。 | I2S 连续串行时钟,位时钟。 | |

| I2S0_WS | 串接 22ohm 电阻。 | I2S 帧时钟,用于声道选择。 | |

| I2S0_SDI | 串接 22ohm 电阻。 | I2S 串行数据 0 输入。 | |

| I2S0_SDO | 串接 22ohm 电阻。 | I2S 串行数据 0 输出。 | |

| I2S1_MCLK | AVDD18_PERI2 | 串接 22ohm 电阻。 | I2S 系统时钟输出。 |

| I2S1_SCLK | 串接 22ohm 电阻。 | I2S 连续串行时钟,位时钟。 | |

| I2S1_WS | 串接 22ohm 电阻。 | I2S 帧时钟,用于声道选择。 | |

| I2S1_SDI | 串接 22ohm 电阻。 | I2S 串行数据 0 输入。 | |

| I2S1_SDO | 串接 22ohm 电阻。 | I2S 串行数据 0 输出。 | |

| I2S2_MCLK | AVDD18_PERI2 | 串接 22ohm 电阻。 | I2S 系统时钟输出。 |

| I2S2_SCLK | 串接 22ohm 电阻。 | I2S 连续串行时钟,位时钟。 | |

| I2S2_WS | 串接 22ohm 电阻。 | I2S 帧时钟,用于声道选择。 | |

| I2S2_SDI | 串接 22ohm 电阻。 | I2S 串行数据 0 输入。 | |

| I2S2_SDO | 串接 22ohm 电阻�。 | I2S 串行数据 0 输出。 | |

| I2S3_MCLK | AVDD18_PERI2 | 串接 22ohm 电阻。 | I2S 系统时钟输出。 |

| I2S3_SCLK | 串接 22ohm 电阻。 | I2S 连续串行时钟,位时钟。 | |

| I2S3_WS | 串接 22ohm 电阻。 | I2S 帧时钟,用于声道选择。 | |

| I2S3_SDI0 | 串接 22ohm 电阻。 | I2S 串行数据 0 输入。 | |

| I2S3_SDI1 | 串接 22ohm 电阻。 | I2S 串行数据 1 输入。 | |

| I2S3_SDI2 | 串接 22ohm 电阻。 | I2S 串行数据 2 输入。 | |

| I2S3_SDI3 | 串接 22ohm 电阻。 | I2S 串行数据 3 输入。 | |

| I2S2_SDO0 | 串接 22ohm 电阻。 | I2S 串行数据 0 输出。 | |

| I2S2_SDO1 | 串接 22ohm 电阻。 | I2S 串行数据 1 输出。 | |

| I2S2_SDO2 | 串接 22ohm 电阻。 | I2S 串行数据 2 输出。 | |

| I2S2_SDO3 | 串接 22ohm 电阻。 | I2S 串行数据 3 输出。 |

注意

I2S 信号均为 1.8V 电平,设计时需注意电平的匹配。

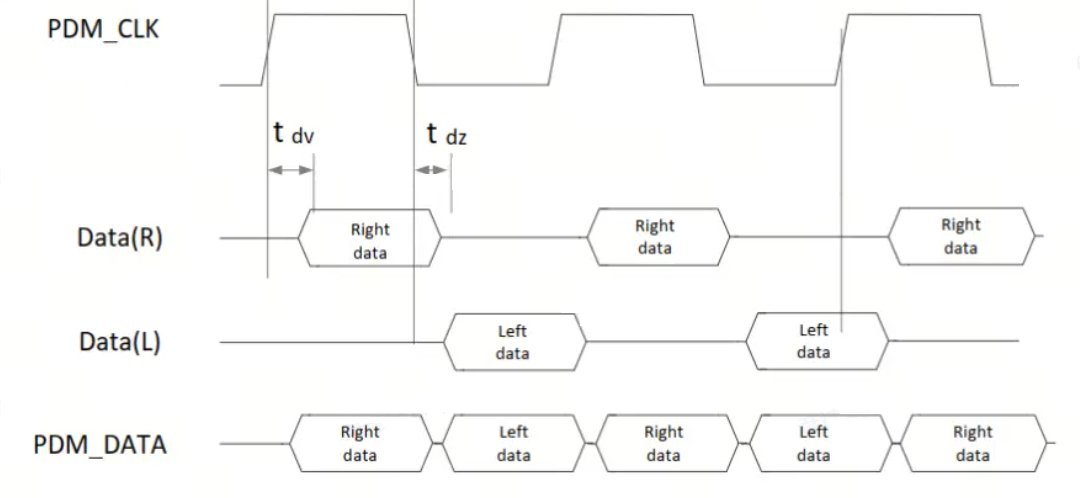

PDM

概述

A210 提供了 1 组 PDM 接口,都工作在主接收模式(master receive mode,即 A210 提供 PDM 时钟、接收数据)支持 4 通道输入能力,16/24bits 的位宽,最高到 192kHz 的采样率。

PDM 接口通常用于接入数字麦克风,或者通过 PDM 接口的模拟音频 ADC 对模拟麦克风进行录音。

下图是 PDM 接口的数据格式,PDM_DATA 由 Data(R)和 Data(L)组成,PDM 是 1bit 采样接口,分别在 CLK 的上升沿、下降沿采样 Data(L)和 Data(R),即每根 PDM_SDIx 数据线可传输两个声道的音频数据。

PDM 引脚复用在 AVDD18_PERI1 电源域,电平为1.8V 需要核对 PDM 外设的 IO 电平,使其匹配对应的 IO 电源域供电。

设计建议

PDM0 接口匹配设计推荐如下表所示。

| 信号 | 电源域 | 连接方式 | 描述 |

|---|---|---|---|

| PDM_CLK | AVDD18_PERI1 | 串联 22ohm 电阻。 | PDM 时钟。 |

| PDM_SDIN0 | 直连。 | PDM 数据输入 0。 | |

| PDM_SDIN1 | 直连。 | PDM 数据输入 1。 | |

| PDM_SDIN2 | 直连。 | PDM 数据输入 2。 | |

| PDM_SDIN3 | 直连。 | PDM 数据输入 3。 |

当通过连接器实现板对板连接时,建议时钟/控制/信号都串接一定阻值的电阻(22ohm-100ohm 之间,具体以能满足 SI 测试为准),并预留 TVS 器件。

音频外设设计参考

大多数情况下,上文提及的数字音频接口不可直接使用,需要配套相关外设才得以实现具体的音频能力。本章节对于常用的音频场景,给出了设计建议,用户可参考使用。

放音设备、耳机、喇叭

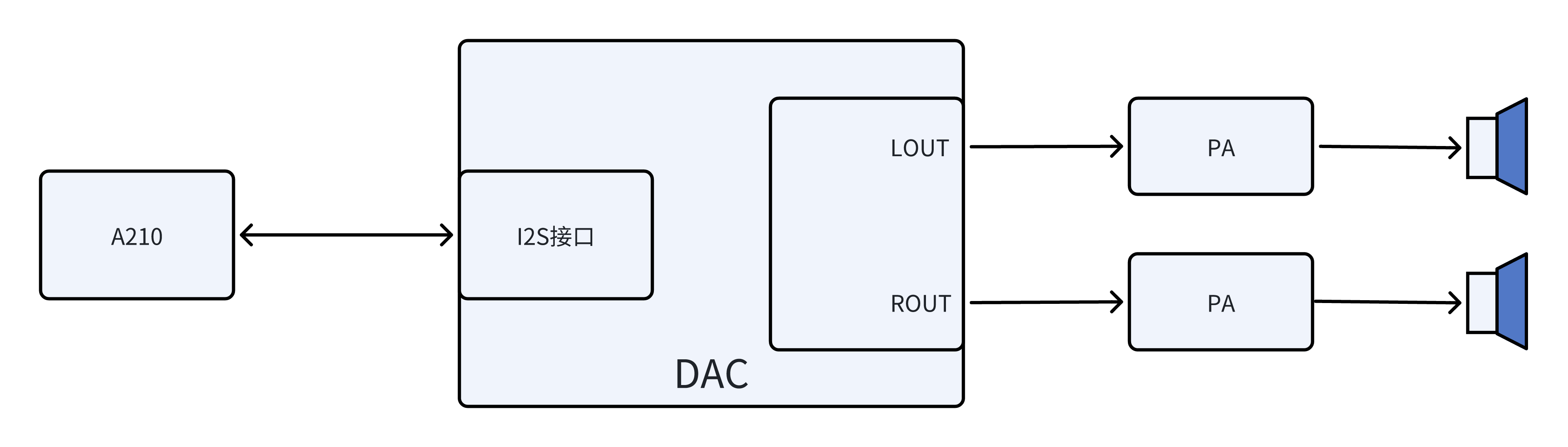

对于喇叭放音需求,实现方案如下,A210 通过 I2S 连接音频 DAC 实现模拟输出,再通过音频功放实现功率放大驱动喇叭。

录音设备、麦克风

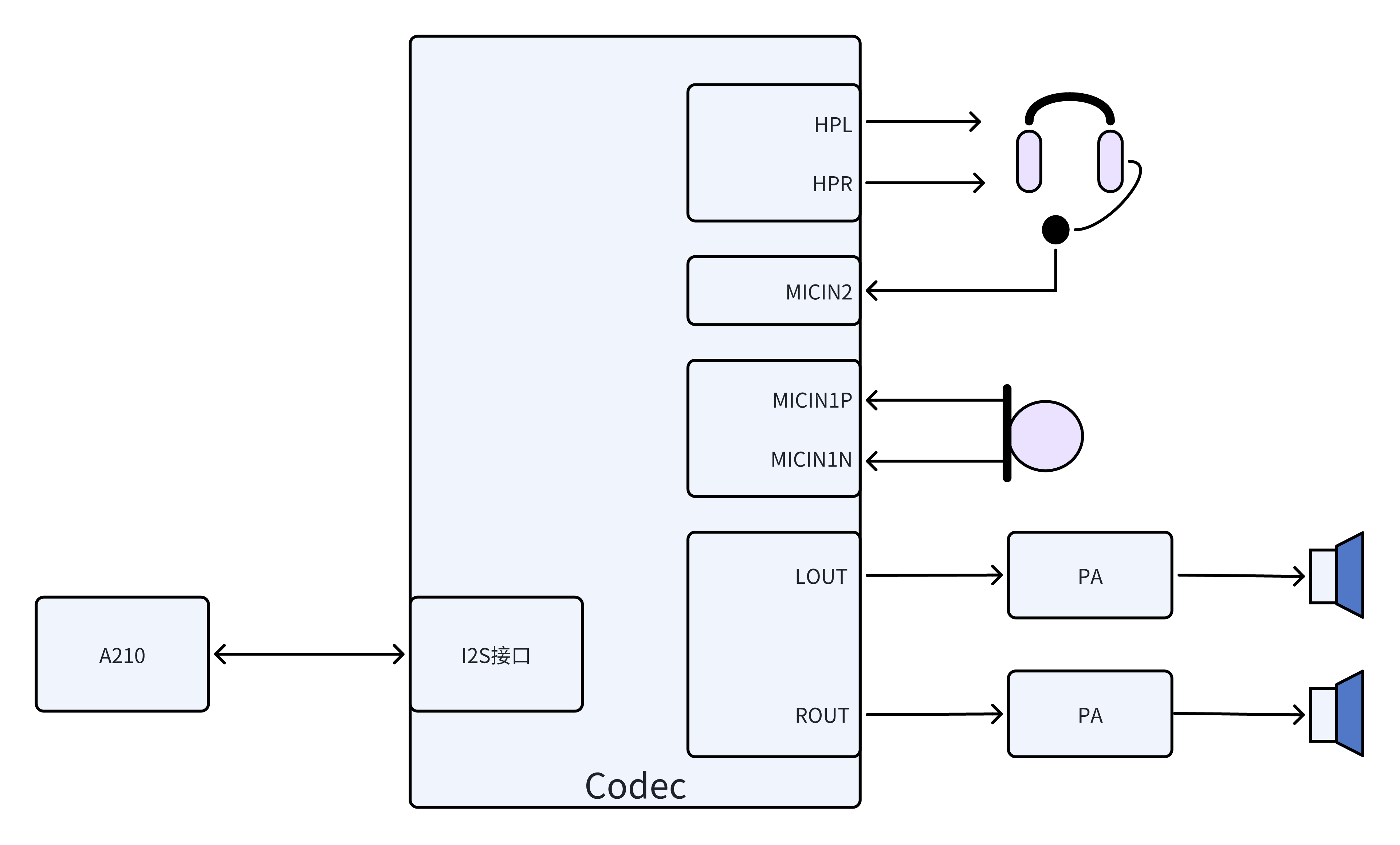

在平板、笔电等应用场景中,除了放音还有录音的需求,此时通常使用集成 ADC、DAC 的 Codec 来实现相关功能,如下图所示。

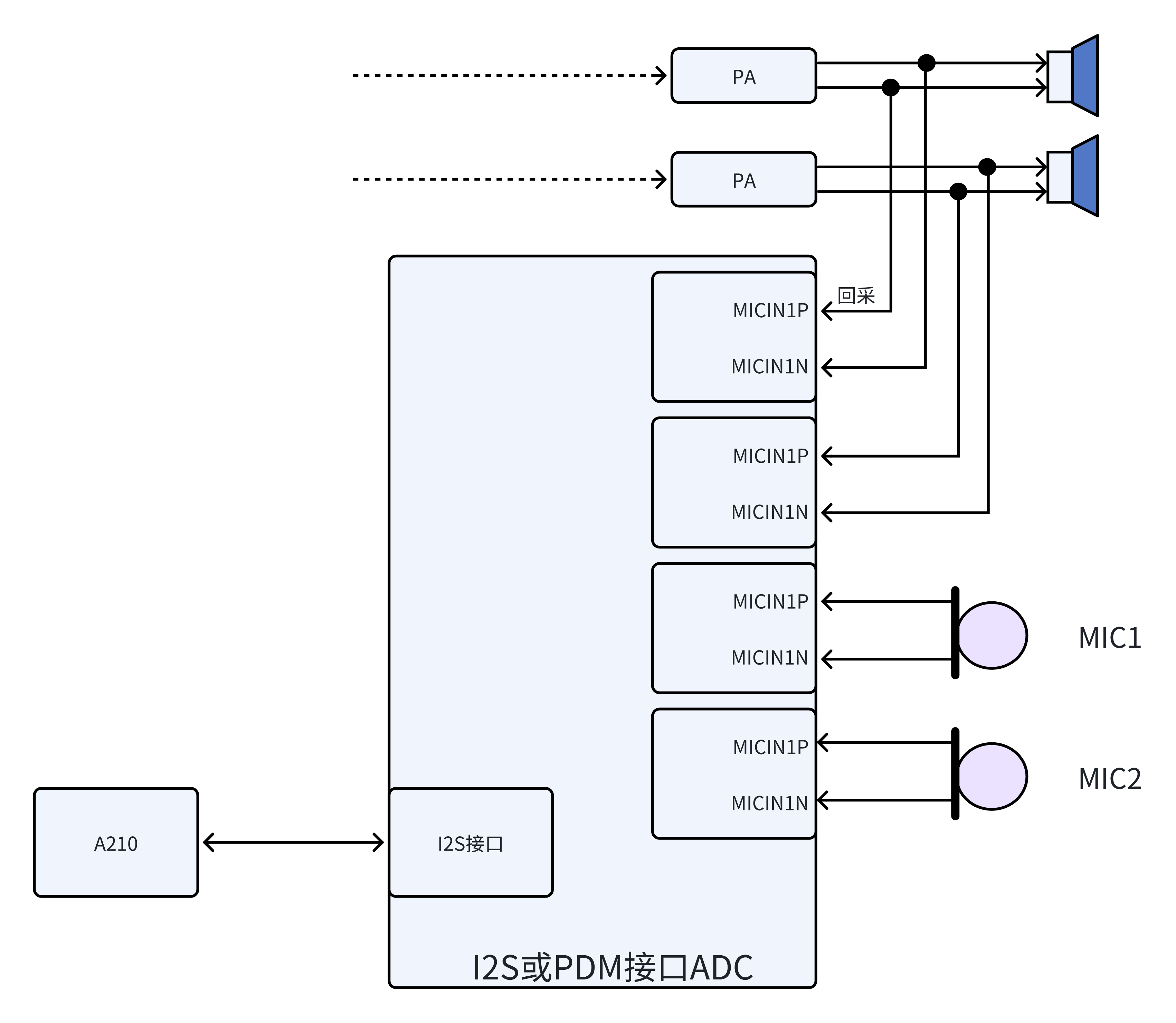

多麦克风方案介绍

对于有多麦克风输入(麦克风阵列、远场识别)的场景,此时需要接入较多的麦克风,常见的扩展方案有如下三种,若都不能满足具体需求、可联系技术支持讨论可行性。

- 通过 I2S 接口的 Codec 实现多个麦克风和喇叭回采的输入采集。

- 通过 PDM 接口的 Codec 实现多个麦克风和喇叭回采的输入采集。

- 通过 PDM 接口的麦克风实现录音,通过 PDM 接口的 Codec 实现喇叭回采的输入采集。

如果存在路数不够的情况,可以通过多根 SDI 信号线来实现多组输入,或者通过 I2S 接口的 TDM 模式实现级联输入。硬件上简单堆叠相同电路即可。

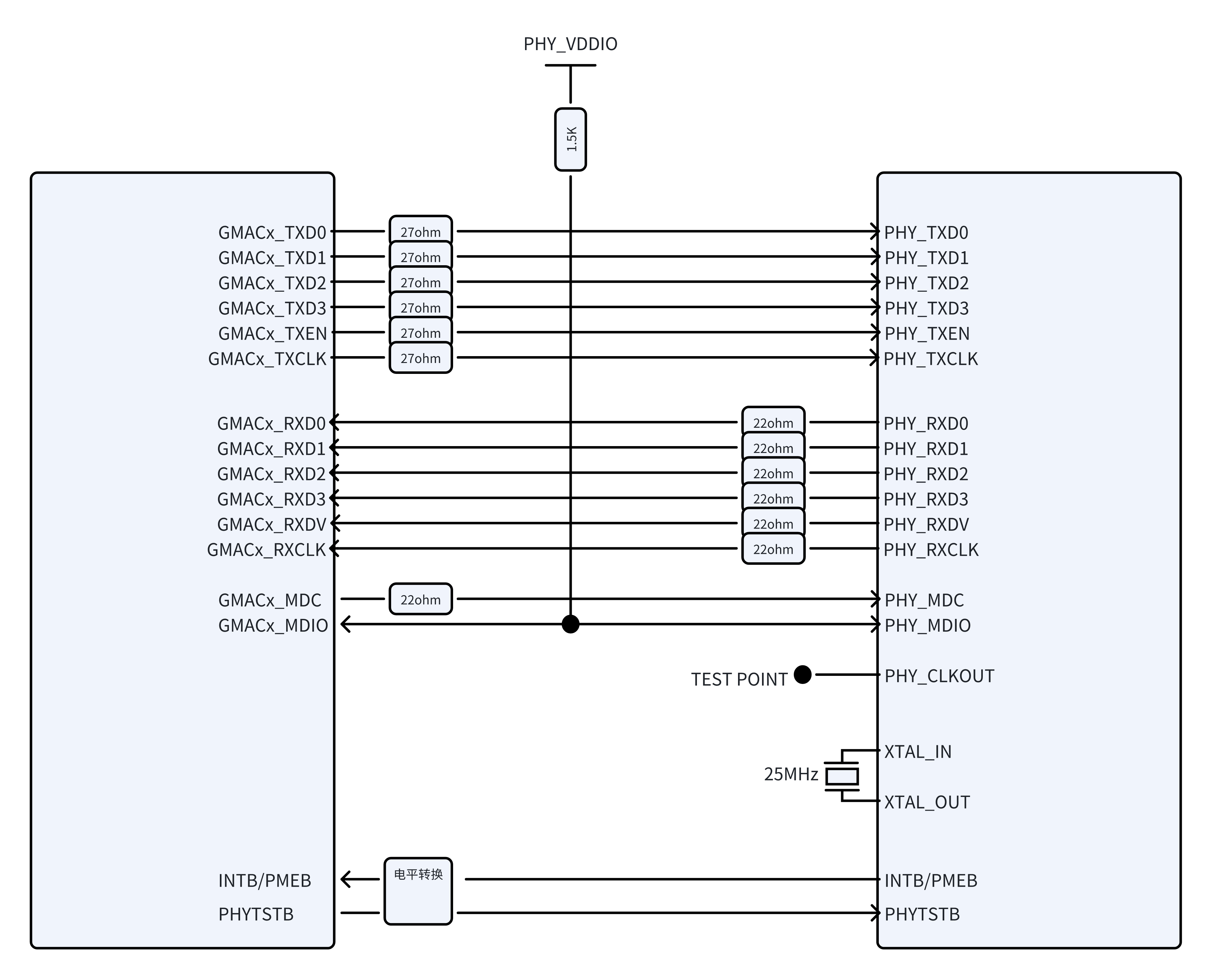

GMAC 接口电路

概述

A210 芯片拥有 2 个 GMAC 控制器,提供RGMII 接口连接外置的 Ethernet PHY,GMAC 控制器支持以下功能。

- 支持 10/100/1000 Mbps 数据传输速率的 RGMII 接口。

- 支持 TSN。

- 支持 TSO。

- 设置成虚拟化(Multiple Channels and Queues)。

- 支持 UFO。

- 支持硬件流控功能。

- 支持远程唤醒功能。

GMAC0 和 GMAC1 的 RGMII 接口复用在 AVDD18_PERI1 电源域。

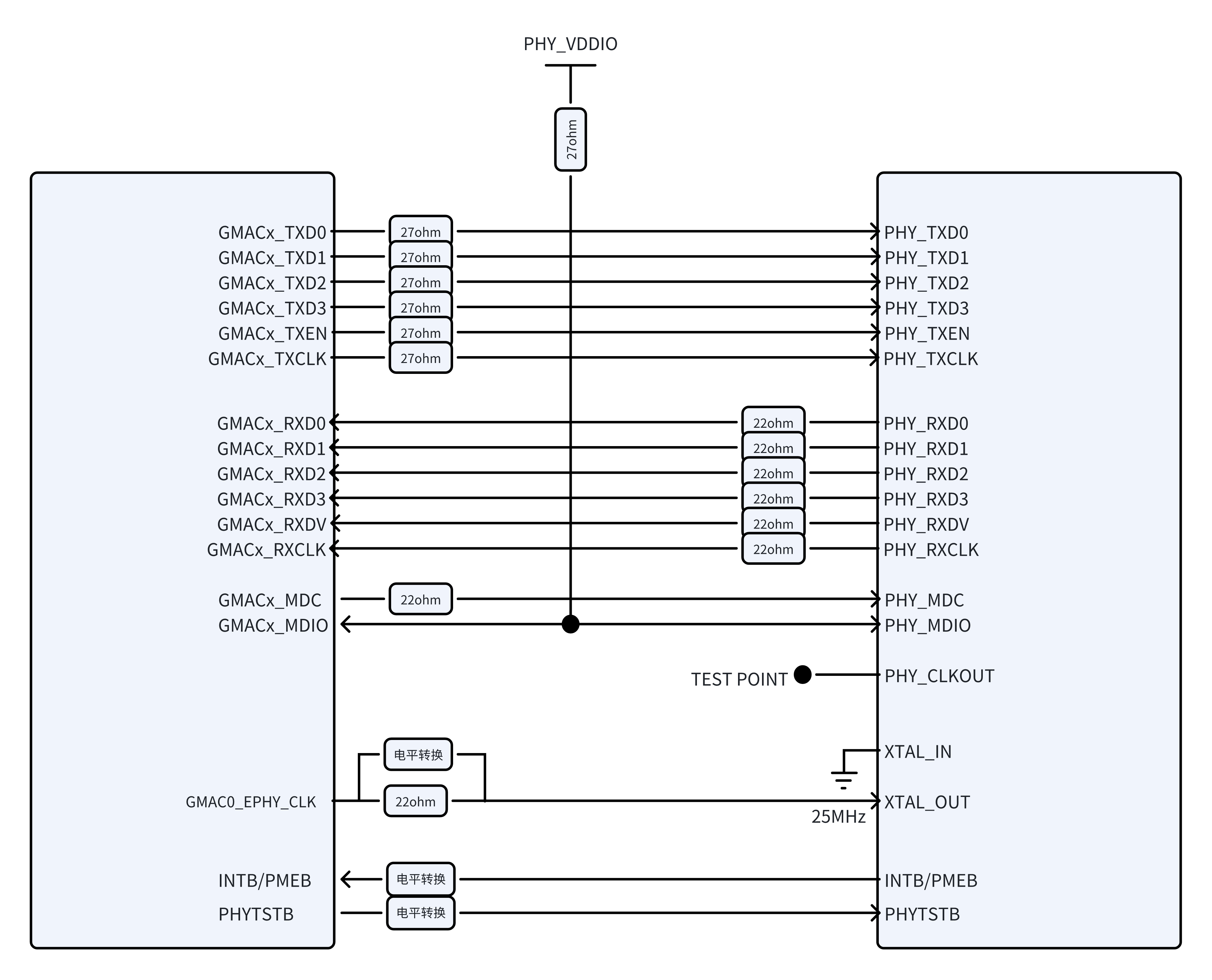

设计建议

RGMII 接口设计中请注意:

-

GMAC0 和 GMAC1 只支持 1.8V 电平。

-

为提高 RGMII 接口性能,所在 VCCIOx 电源的去耦电容不得删除,布局时请靠近管脚放置。

-

TXD0-TXD3,TXCLK,TXEN 需在 A210 端预留串接 0 ohm 电阻,根据实际情况有条件提高信号质量。

-

RXD0-RXD3,RXCLK,RXDV 需在 PHY 端串接 22 ohm 电阻,以提高信号质量。

-

RGMII接口上下拉和匹配设计推荐如下表。

信号 IO类型(芯片端) 连接方式 RGMII接口 信号描述 GMACx_TX_CLK O 串接 27ohm,靠近 A210 端。 RGMIIx_TX_CLK 数据发送参考时钟 GMACx_RX_CLK I 串接 22ohm,靠近 PHY 端。 RGMIIx_RX_CLK 数据接受参考时钟 GMACx_TXEN O 串接 27ohm,靠近 A210 端。 RGMIIx_TXEN 数据发送使能(上升沿)

数据发送错误(下降沿)

GMACx_TXD[3:0] O 串接 27ohm,靠近 A210 端。 RGMIIx_TXD[3:0] 数据发送 GMACx_RXDV I 串接 22ohm,靠近 PHY 端。 RGMIIx_RXDV 数据接收有效(上升沿)

数据接收错误(下降��沿)

GMACx_RXD[3:0] I 串接 22ohm,靠近 PHY 端。 RGMIIx_RXD[3:0] 数据接收 GMACx_MDC O 串接 27ohm,靠近 A210 端。 RGMIIx_MDC 管理数据时钟 GMACx_MDIO I/O 外部上拉 1.5Kohm 电阻。 RGMIIx_MDIO 管理数据输入/输出 GMACx_PHY_INT I RGMIIx_INTB 中断及唤醒信号输入 GMAC0_EPHY_CLK O 预留串接 0ohm,靠近 A210 端。 RGMIIx_EXT_CLK A210 提供 25MHz 时钟替代 PHY 晶体。 -

当通过连接器实现板对板连接时,建议串接一定阻值的电阻(22ohm-100ohm 之间,具体以能满足 SI 测试为准),并预留 TVS 器件。

-

RGMII 连接示意图 1 如下,具体电路请见参考图(GEPHY 工作时钟使用外置 25MHz 晶体)。

-

RGMII 连接示意图 2 如下,具体电路请见参考图(GEPHY 工作时钟使用 A210 提供的 25MHz 时钟)。

-

Ethernet PHY 的 Reset 信号需要用 GPIO 来控制,GPIO 电平必须和 PHY IO 电平匹配,靠近 PHY 管脚建议增加 100nF 电容,加强抗静电能力。

注意:

RTL8211F/FI 的复位管脚只支持 3.3V 电平,所以需要增加电平转换。

-

Ethernet PHY 的 INTB/PMEB 信号接到 A210 的GMACx_PHY_INT上。若需要支持唤醒功能,也可以连接到 AON GPIO 上。电平为 1.8V,注意和 PHY IO 电平匹配。

注意:

RTL8211F/FI 的 INTB/PMEB 为开漏输出,外部必须增加上拉电阻。

-

PHY 使用外置晶体时,晶体电容请根据实际使用的晶体的负载电容值选择,控制频偏在 +/-20ppm 以内。

-

MDIO 必须外部加上拉电阻,推荐 1.5-1.8Kohm,上拉电源必须和 IO 电源保持一致。

-

Ethernet PHY 变压器中心抽头的连接,建议参考各 Ethernet PHY 厂家的参考设计。

-

1000pF 隔离电容建议采用高压安规电容,有足够大的电气间隙保证雷击的安全性。

-

网络变压器高压侧的 75 ohm 电阻建议采用 0805 以上的封装。

-

雷击防护等级达到 4KV 以上需要增加防雷管,普通的隔离变压器只能满足 2KV 等级要求。

-

如果有雷击差分测试要求,MDI 差分对间需要增加 TVS 管。

-

PHY 的初始化硬件配置必须和实际需求匹配。

UART 接口电路

A210 芯片拥有 11个 UART 控制器,其中1个AO UART,10个普通UART。

A210 UART 接口分布情况如下。

| UART编号 | UART信号 | 电源域 | 备注 |

|---|---|---|---|

| AOUART | AOUART_TXD | AVDD18_AON | E902 调试串口,建议预留调试接口。 |

| AOUART_RXD | |||

| UART0 | UART0_TXD | AVDD18_PERI1 | |

| UART0_RXD | |||

| UART0_CTSN | |||

| UART0_RTSN | |||

| UART1 | UART1_TXD | ||

| UART1_RXD | |||

| UART2 | UART2_TXD | ||

| UART2_RXD | |||

| UART3 | UART3_TXD | ||

| UART3_RXD | |||

| UART4 | UART4_TXD | AVDD18_PERI2 | C908/C920 调试串口,建议预留调试接口。 |

| UART4_RXD | |||

| UART5 | UART5_TXD | ||

| UART5_RXD | |||

| UART6 | UART6_TXD | ||

| UART6_RXD | |||

| UART6_CTSN | |||

| UART6_RTSN | |||

| UART7 | UART7_TXD | 可用于IRDA | |

| UART7_RXD | |||

| UART8 | UART8_TXD | ||

| UART8_RXD | |||

| UART9 | UART9_TXD | ||

| UART9_RXD |

- UART 信号均为 1.8V,注意与外设的电平匹配。当不一致时需要使用电平转换。

- AOUART 和 UART4 默认作为调试 UART,建议设计时预留调试接口。

- 当通过连接器实现板对板连接时,预留 TVS 器件。

- UART 支持红外,可以连接 IRDA Transceiver 实现红外收发功能,建议使用 UART7。

SPI 接口电路

A210 芯片除了2 个 QSPI 控制器外,还拥有 3 个通用 SPI 控制器,其中 1 个 AO SPI,2 个普通 SPI。

- 支持 master �模式。

- AO SPI 支持低功耗唤醒。

- 每个接口支持 2 个片选。

SPI 接口分布情况如下。

| SPI编号 | 信号 | 电源域 |

|---|---|---|

| AOSPI | AOSPI_CSN0 | AVDD18_AON |

| AOSPI_CSN1 | ||

| AOSPI_D0_MOSI | ||

| AOSPI_D1_MISO | ||

| AOSPI_SCLK | ||

| SPI0 | SPI0_CSN0 | AVDD18_PERI1 |

| SPI0_CSN1 | ||

| SPI0_D0_MOSI | ||

| SPI0_D1_MISO | ||

| SPI0_SCLK | ||

| SPI1 | SPI1_CSN0 | AVDD18_PERI2 |

| SPI1_CSN1 | ||

| SPI1_D0_MOSI | ||

| SPI1_D1_MISO | ||

| SPI1_SCLK |

- SPI 信号均为 1.8V,注意与外设的电平匹配。当不一致时需要使用电平转换。

- 当通过连接器实现板对板连接时,预留 TVS 器件。

CAN 接口电路

A210 芯片拥有 3 个 CAN 控制器。

A210 CAN 接口分布情况如下。

| CAN编号 | 信号 | 电源域 |

|---|---|---|

| CAN0 | CAN0_RX | AVDD18_PERI1 |

| CAN0_TX | ||

| CAN1 | CAN1_RX | |

| CAN1_TX | ||

| CAN2 | CAN2_RX | AVDD18_PERI2 |

| CAN2_TX |

- CAN 信号均为 1.8V,注意与外设的电平匹配。当不一致时需要使用电平转换。

- 当通过连接器实现板对板连接时,预留 TVS 器件。

I2C 接口电路

A210 芯片拥有 10 个 I2C 控制器,支持以下功能。

- 支持 I2C 总线主模式。

- 最高速率 3.4Mbps。

- 支持 7 位和 10 位寻址模式。

10 个 IC 控制器中,有 2 个AO I2C,8 个普通 I2C。AO I2C 能够支持唤醒。

A210 I2C 接口分布情况如下表。

| I2C编号 | 电源域 |

|---|---|

| AOI2C0 | AVDD18_AON |

| AOI2C1 | |

| I2C0 | AVDD18_PERI1 |

| I2C1 | |

| I2C2 | |

| I2C3 | AVDD18_PERI2 |

| I2C4 | |

| I2C5 | |

| I2C6 | |

| I2C7 |

- I2C 信号均为 1.8V,注意与外设的电平匹配。当不一致时需要使用电平转换。

- I2C 信号 SCL、SDA 需要外接上拉电阻,根据总线负载不同,选择不同阻值的电阻。

- I2C 总线上各设备地址不要冲突,上拉电源必须和电源保持一致。

- 当通过连接器实现板对板连接时,预留 TVS 器件。

PWM 接口电路

A210 芯片拥有 3 个独立的 PWM 控制器,每个控制器有 6 个通道,最多可以有 18 个 PWM 通道,最高频率 12MHz。

PWM 接口分布情况如下表所示。

| PWM编号 | 电源域 |

|---|---|

| PWM0_CH0 | AVDD18_PERI1 |

| PWM0_CH1 | |

| PWM0_CH2 | |

| PWM0_CH3 | |

| PWM0_CH4 | |

| PWM0_CH5 | |

| PWM1_CH0 | AVDD18_PERI2 |

| PWM1_CH1 | |

| PWM1_CH2 | |

| PWM1_CH3 | |

| PWM1_CH4 | |

| PWM1_CH5 | |

| PWM2_CH0 | AVDD18_PERI2 |

| PWM2_CH1 | |

| PWM2_CH2 | |

| PWM2_CH3 | |

| PWM2_CH4 | |

| PWM2_CH5 |

- PWM 信号均为 1.8V,注意与外设的电平匹配。当不一致时需要使用电平转换。

- 当通过连接器实现板对板连接时,建议串接一定阻值的电阻(22ohm-100ohm 之间,具体以能满足 SI 测试为准),并预留 TVS 器件。

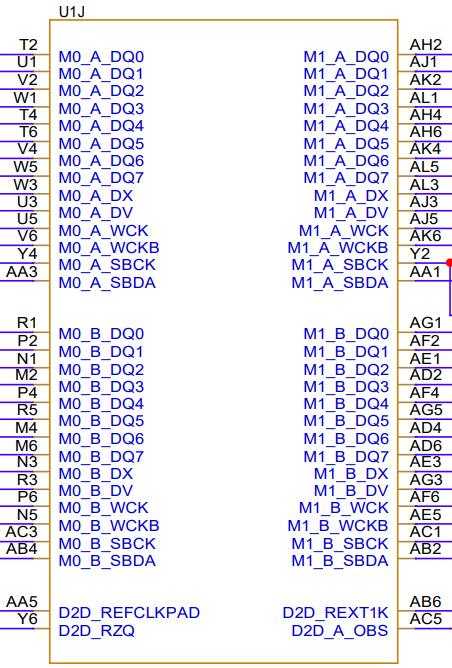

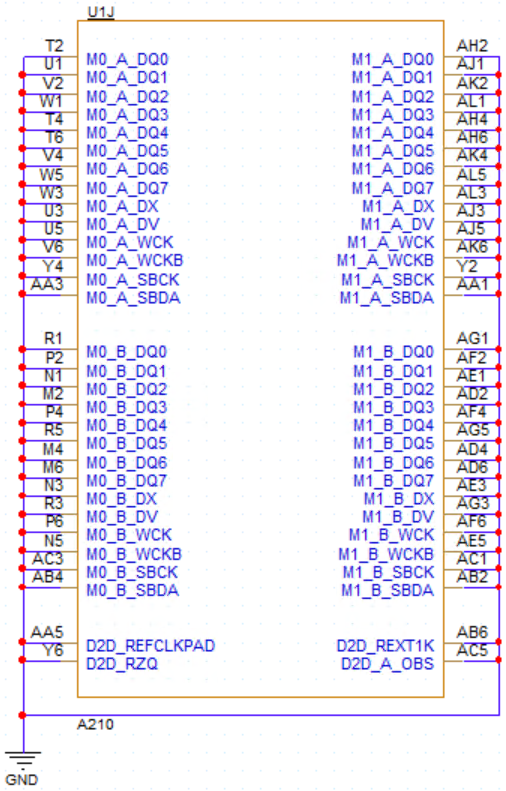

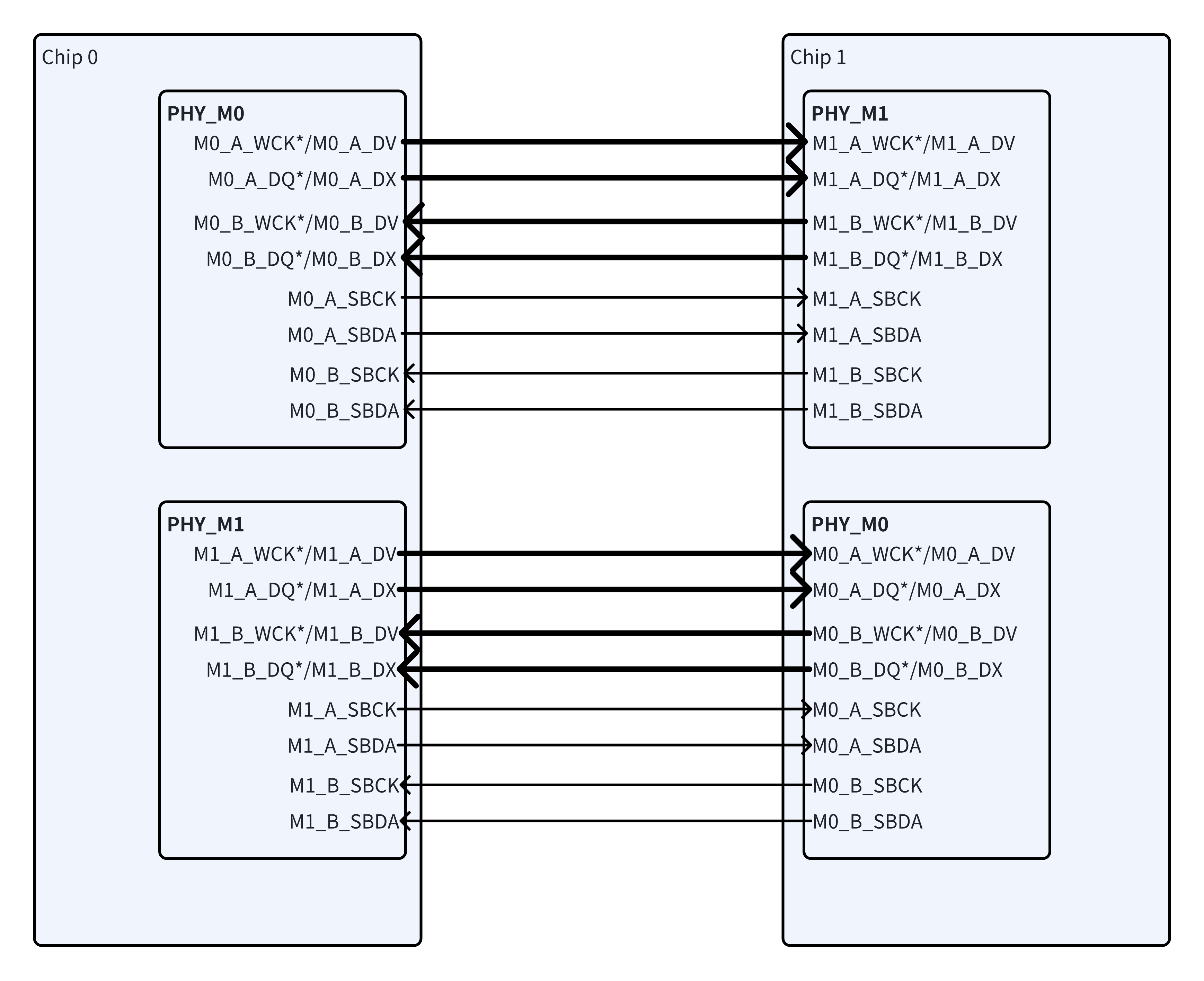

C2C 接口电路

C2C 接口即 Chip-to-Chip 接口,是为了通过连接 Chip,以实现 Chip 之间的紧密耦合,从而提高计算能力。

A210 支持 2 个 C2C Port,其中一个 Port 支持一致性互联,另外一个不支持。

- C2C单个 port 带宽 ≥20GB/s,128B@BL 下读写带宽利用率 ≥71%。

- 支持 2 个 C2C port 之间做 swap。

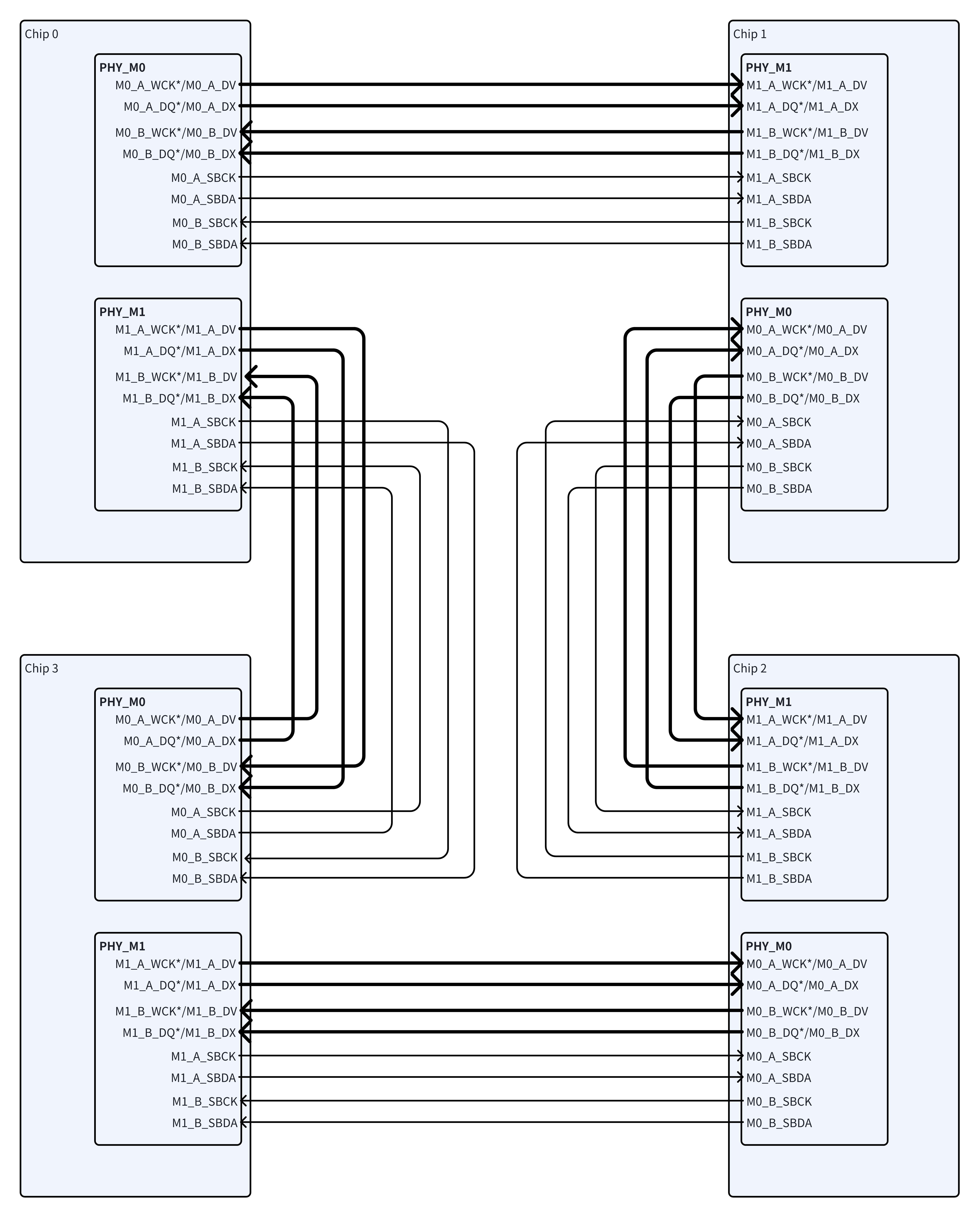

1Chip,2Chip,4Chip 情况下的互联情况如下。

-

1Chip

1Chip 情况下不需要使用 C2C 模块,外部管脚可以拉低到地,如下图所示。

-

2Chip 互联关系

-

4Chip 互联关系