PCB 设计建议

PCB 叠层设计

为了减少在高速信号传输过程中的反射现象,必须在信号源、接收端以及传输线上保持阻抗的匹配。

单端信号线的具体阻抗取决于它的线宽以及与参考平面之间的相对位置。特定阻抗要求的差分对间的线宽/线距则取决于选择的 PCB 叠层结构。由于最小线宽和最小线距是取决于 PCB 类型以及成本要求,选择的 PCB 叠层结构必须能实现板上的所有阻抗需求,包括内层和外层、单端和差分线等。

PCB 层的定义设计原则。

- 原则上应该采用对称结构��设计。对称的含义包括:介质层厚度及种类、铜箔厚度、图形分布类型(电源层、走线层)的对称。

- 主芯片相邻层应为完整的地平面,提供器件面布线参考平面。

- 主电源尽可能与其对应地平面层相邻。

- 所有信号层尽可能与地平面相邻,尽量避免两信号层直接相邻,提供完整的参考地平面。

- 若需要两相邻层布线时,两相邻层距离尽量远,信号尽量互相垂直,减小层间的信号串扰。

PCB 的层定义推荐方案:具体的 PCB 层设置时,要对以上原则进行灵活掌握,根据实际的需求,确定层的排布,切忌生搬硬套。

A210-1DIE-FCBGA 目前主要使用 8 层通孔和 10 层三阶盲埋(专用于 C2C 走线)等叠层,以下叠层做为范例,可以给工程师在叠层结构的选择和评估上提供帮助。如果选择其他类型的叠层,请根据 PCB 厂商给出的规格,重新计算阻抗。

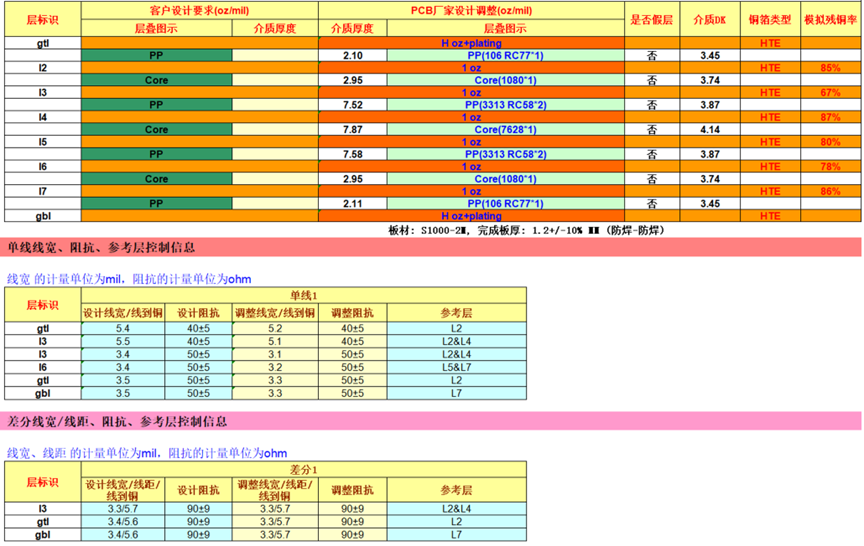

8 层板叠层

在 8 层板叠层设计中,建议层叠为 TOP-Gnd-Signal-GND-Power/Signal--Power/Signal-Gnd-Bottom,顶层信号 L1 的参考平面为 L2,底层信号 L8 的参考平面为 L7,L3 层信号参考平面为 L2 和 L4,主要参考平面为 L2,具体视叠层情况而定,所有层的铜厚必须采用 1oz,下图为 1.2mm 板厚的参考叠层,可以根据板厚要求调整 Core 厚度。

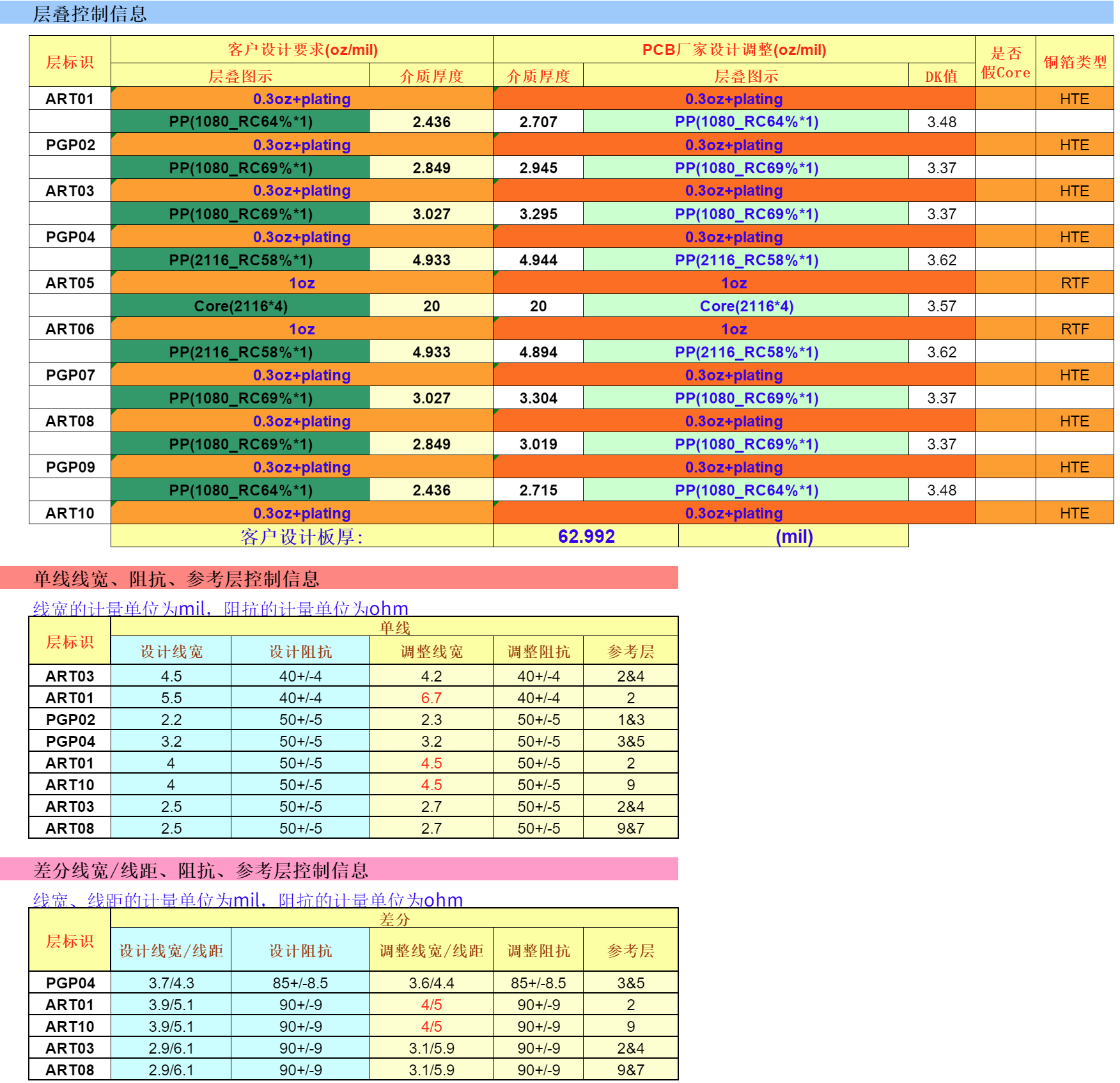

10 层三阶叠层

为了满足 C2C 走线质量,推荐使用 10 层三阶设计,C2C 信号推荐走在 L2 和 L4。走内层为满足低串扰,且采用盲埋设计避免过孔残桩,建议层叠为 TOP-GND/Signal-Signal-Signal/GND–POWER-POWER- GND-Signal/POWER-GND-Bottom,顶层信号 L1 的参考平面为 L2,底层信号 L10 的参考平面为 L9,L2 层信号参考平面为 L1 和 L3,L4层信号参考平面为L3和L5,具体视叠层情况而定。下图为 1.6mm 板厚的参考叠层,可以根据板厚要求调整 Core 厚度。

A210-1DIE-FCBGA 扇出设计

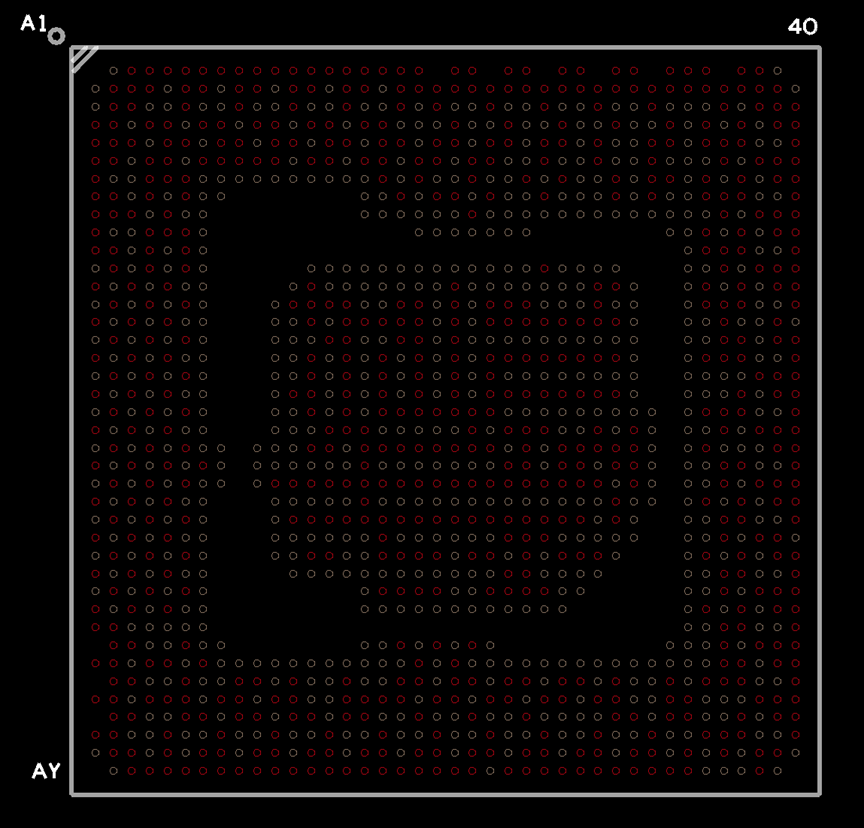

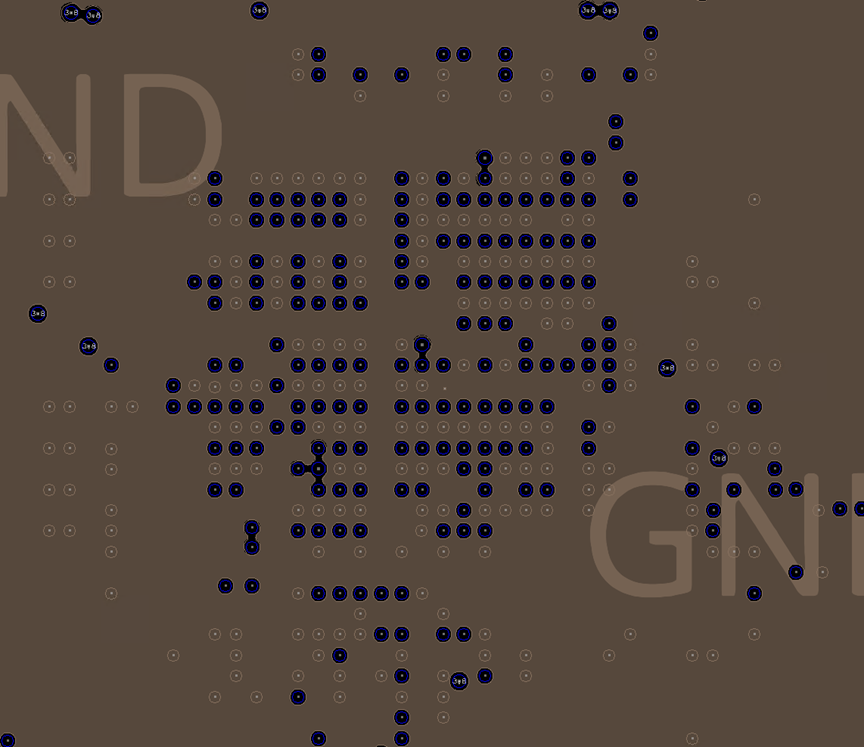

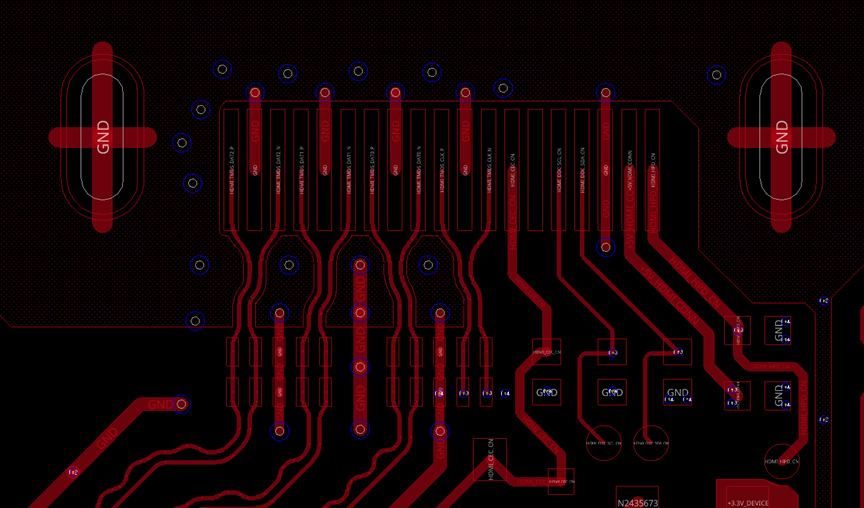

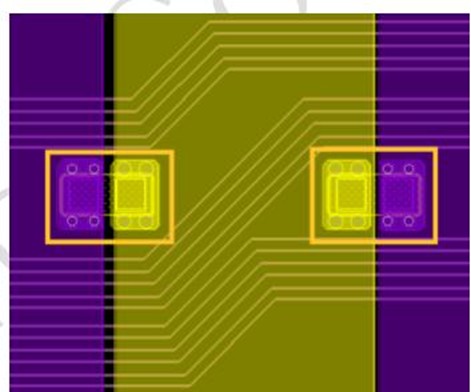

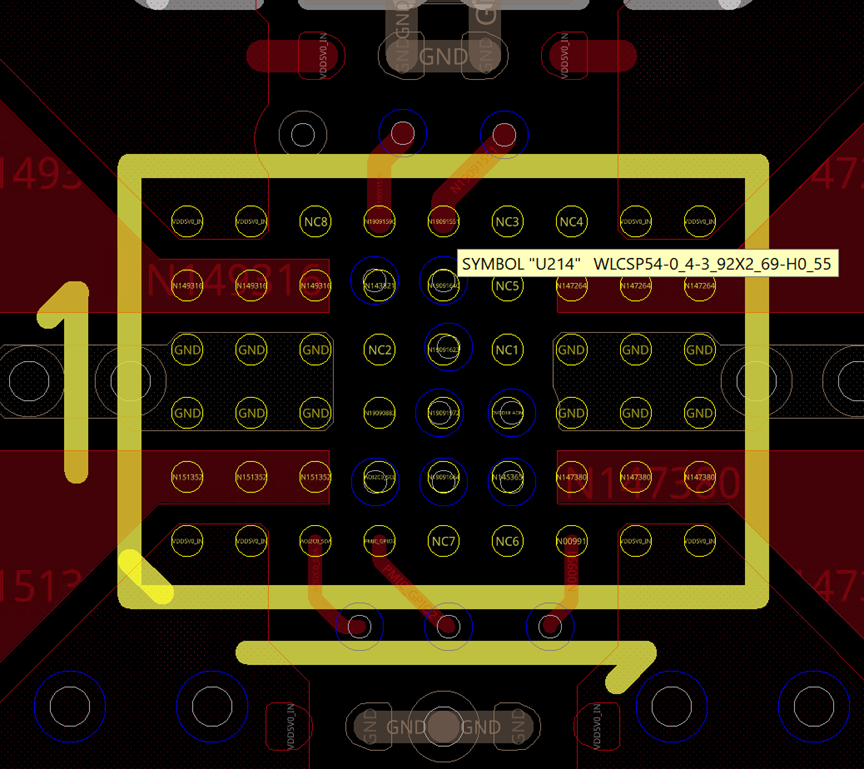

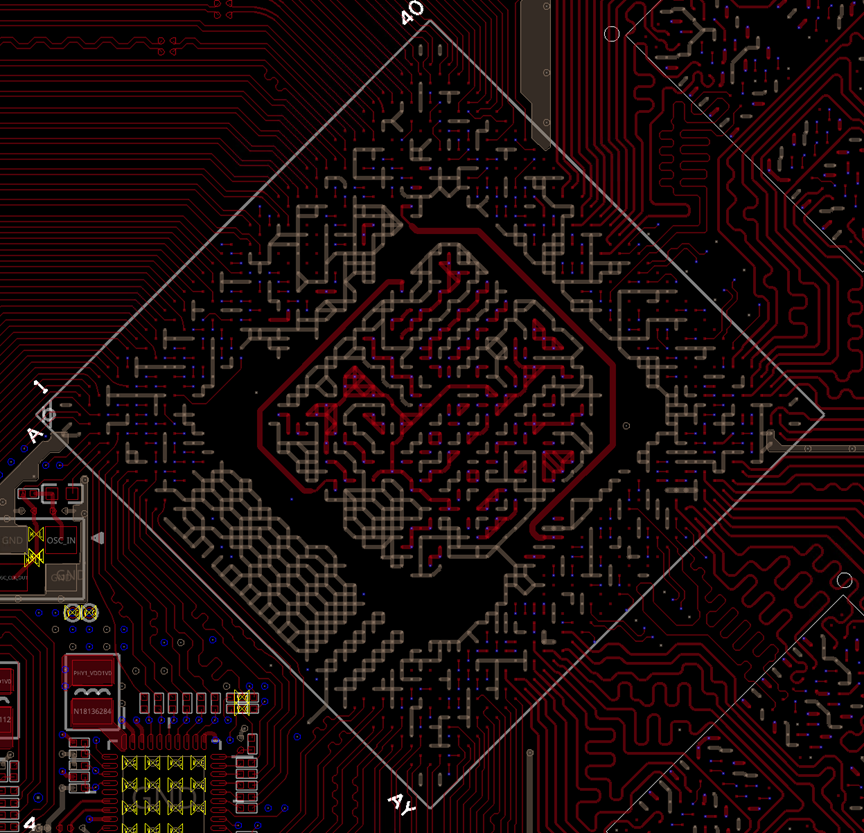

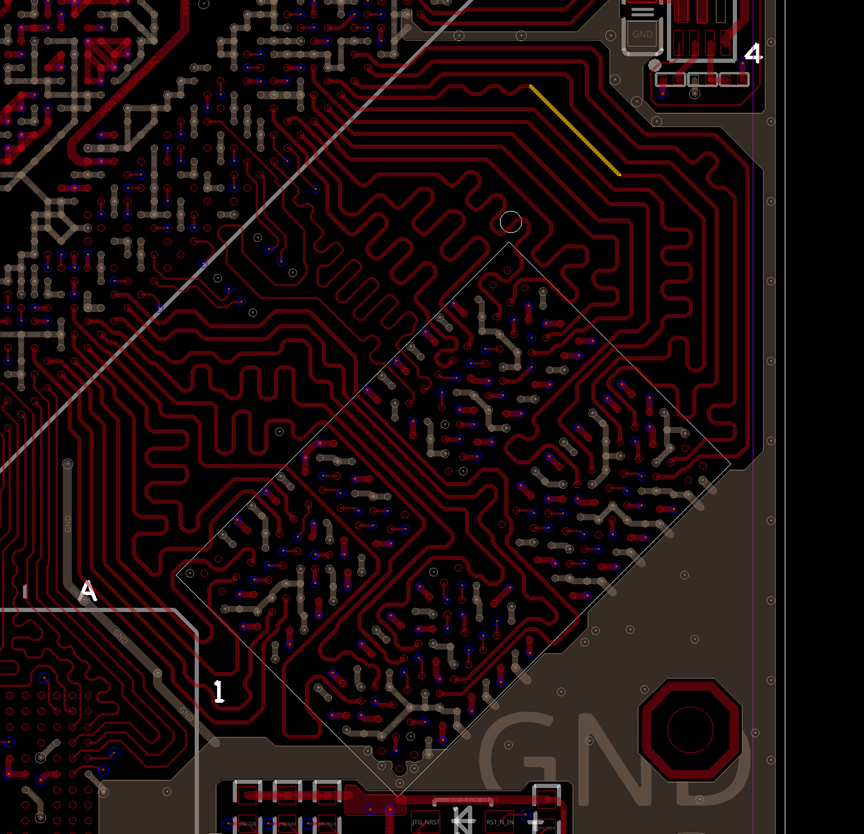

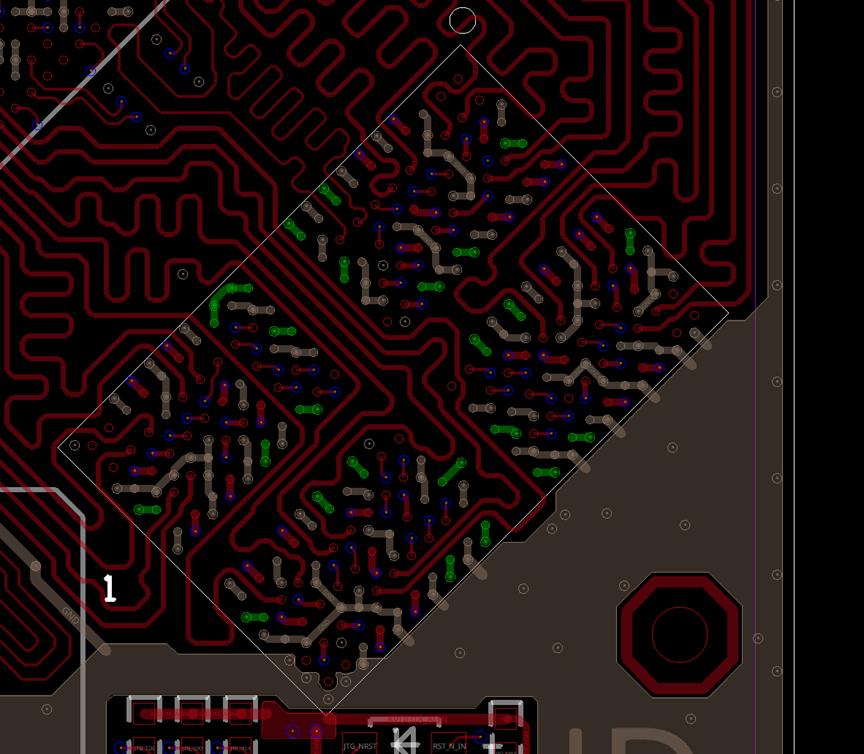

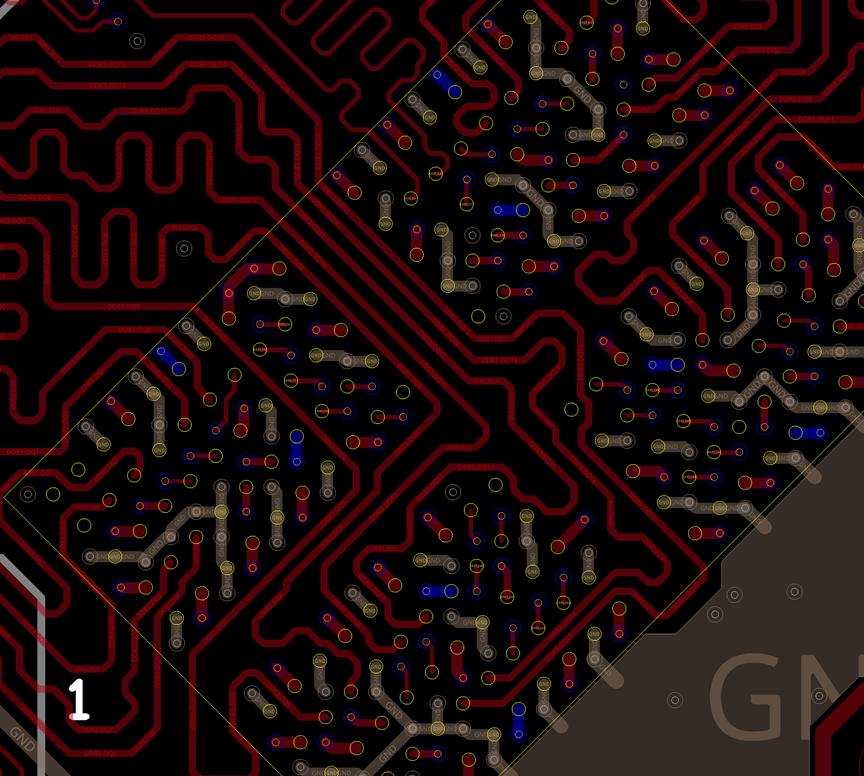

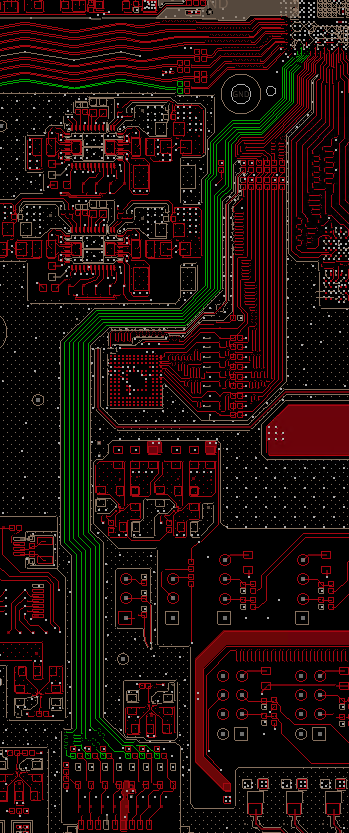

A210-FCBGA封装总共 1373 个 ball,球位由 0.6mm pitch 组成,如下图所示。

-

最外面两圈的 Ball 扇出设计。

A210-1DIE-FCBGA(SoC)靠最外的两圈以及部分第三圈 ball,从 TOP 层可以走最小线宽 4mil 局部扇出,之后应尽快按照相应的特性阻抗线的线宽线距 Fan-out,最小线宽的出线长度尽可能短。

-

内圈的 Ball 扇出设计。

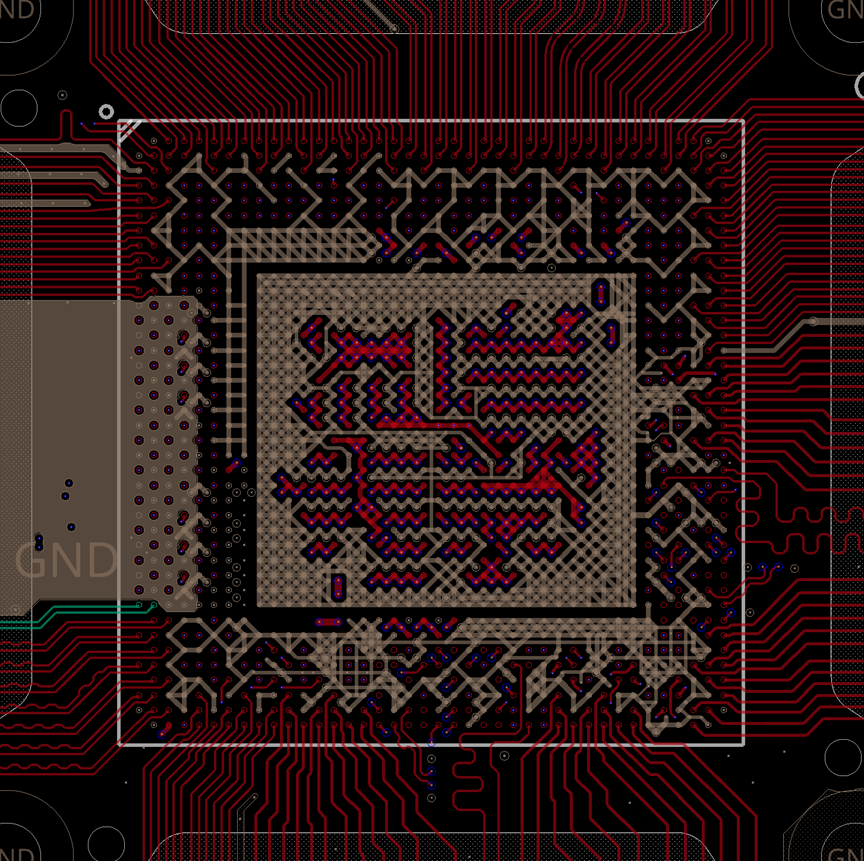

第 3 圈开始,需要换层到内层,换层过孔务必规则放置,并且建议间隔 2-4 排换层过孔,空一排不放置换层过孔,给地平面以及电源平面留出尽量大的通道。

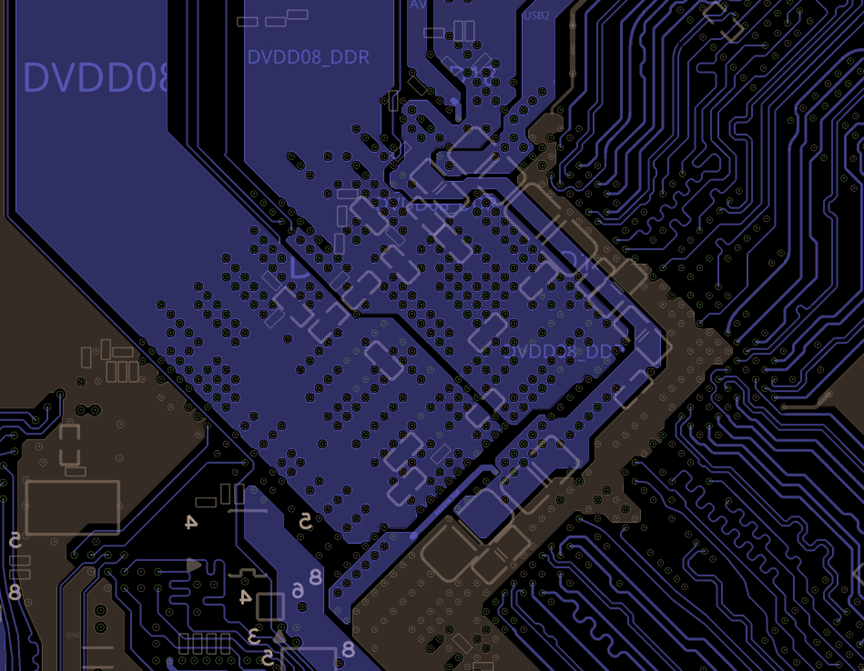

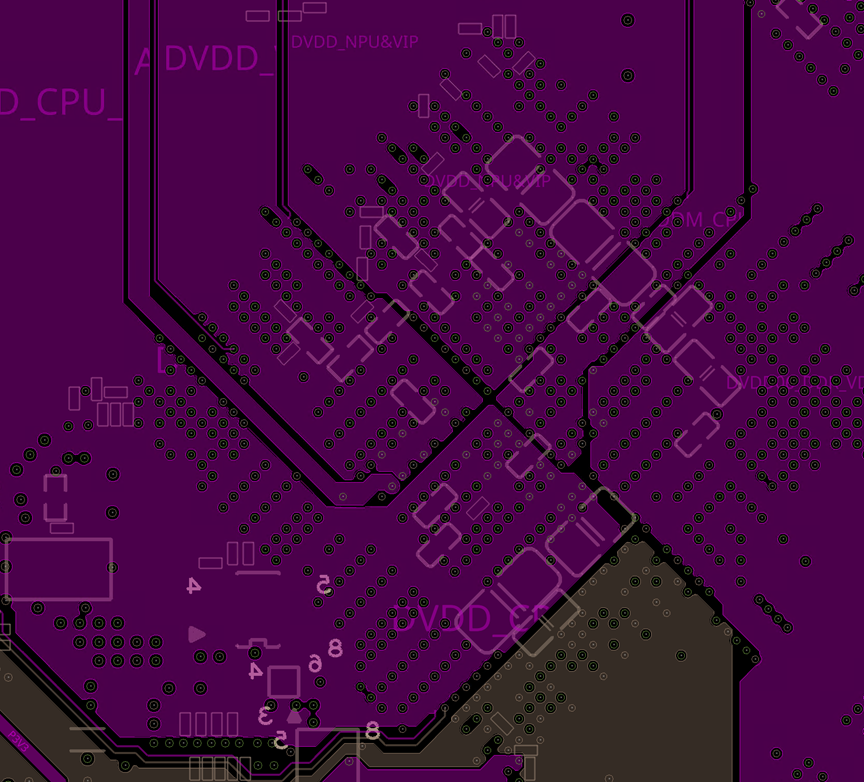

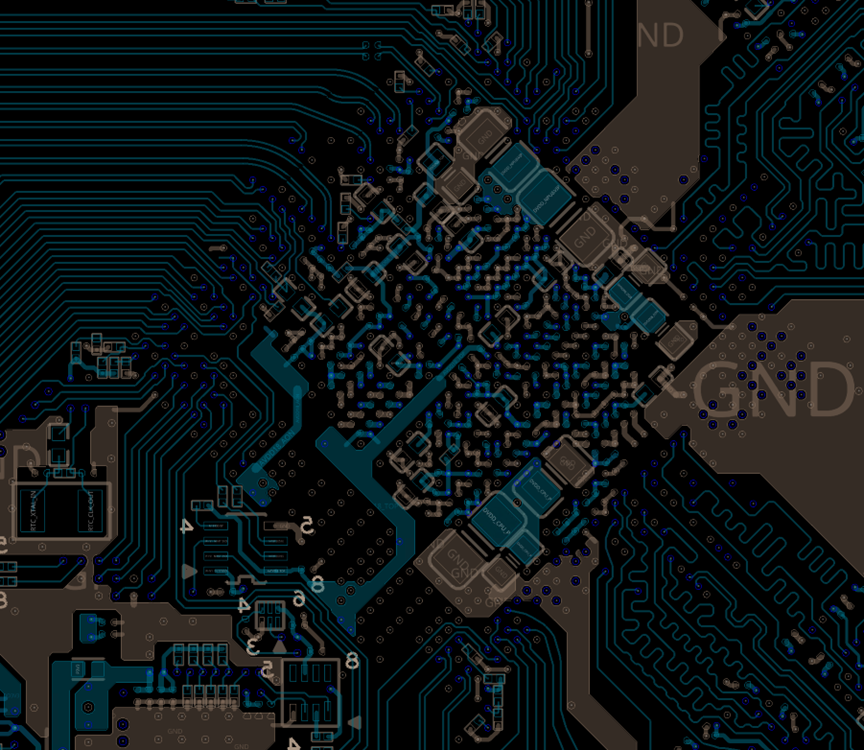

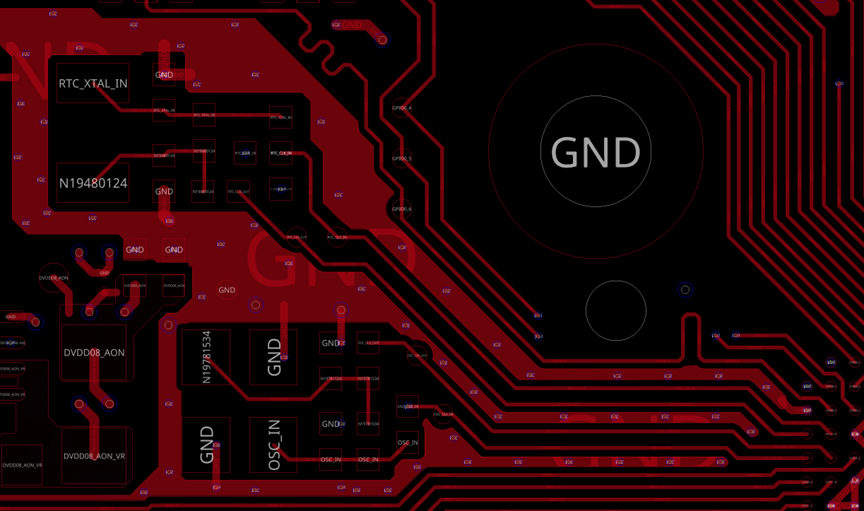

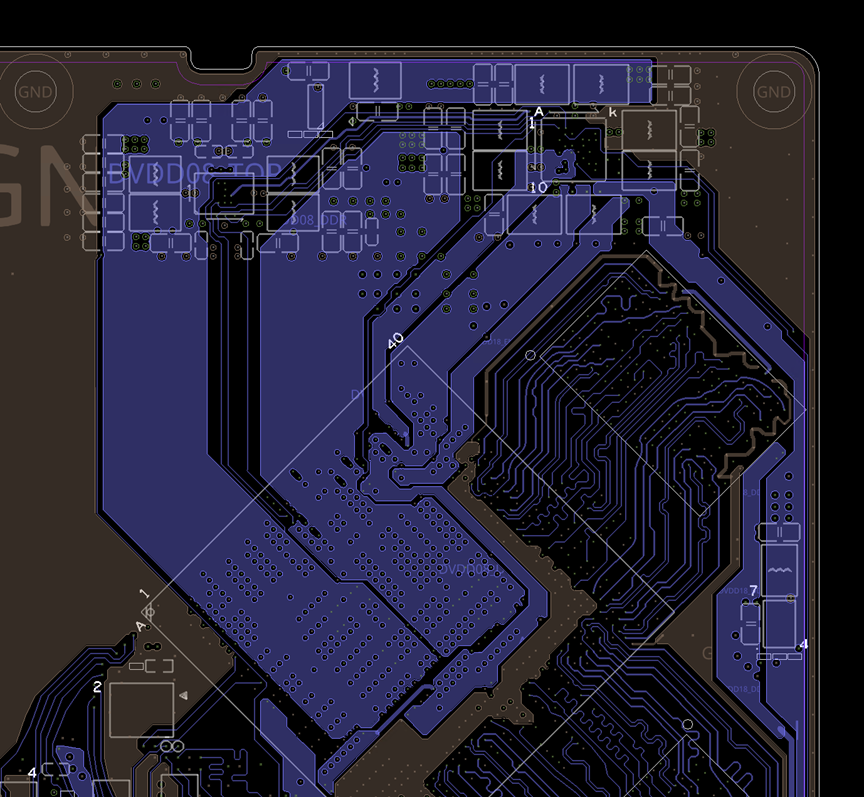

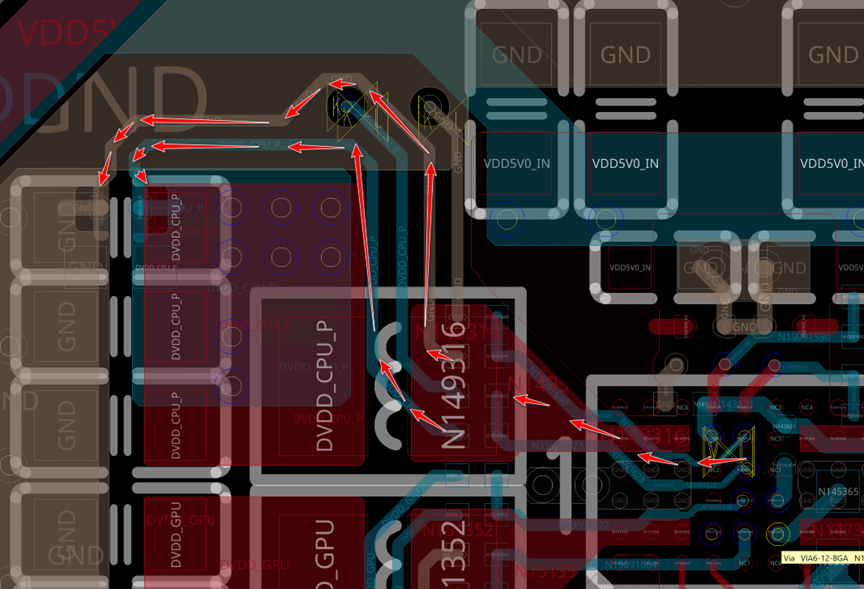

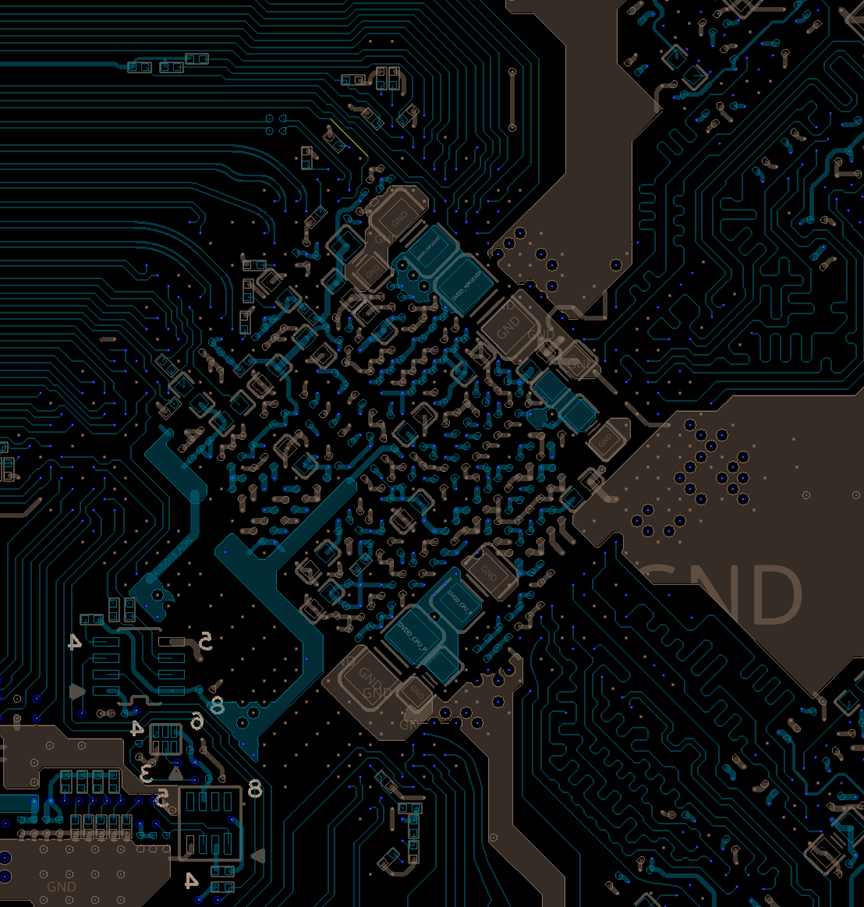

如下图地层平面覆铜情况,有多条通道和外面的地连接,有利于 SI/PI 以及散热。

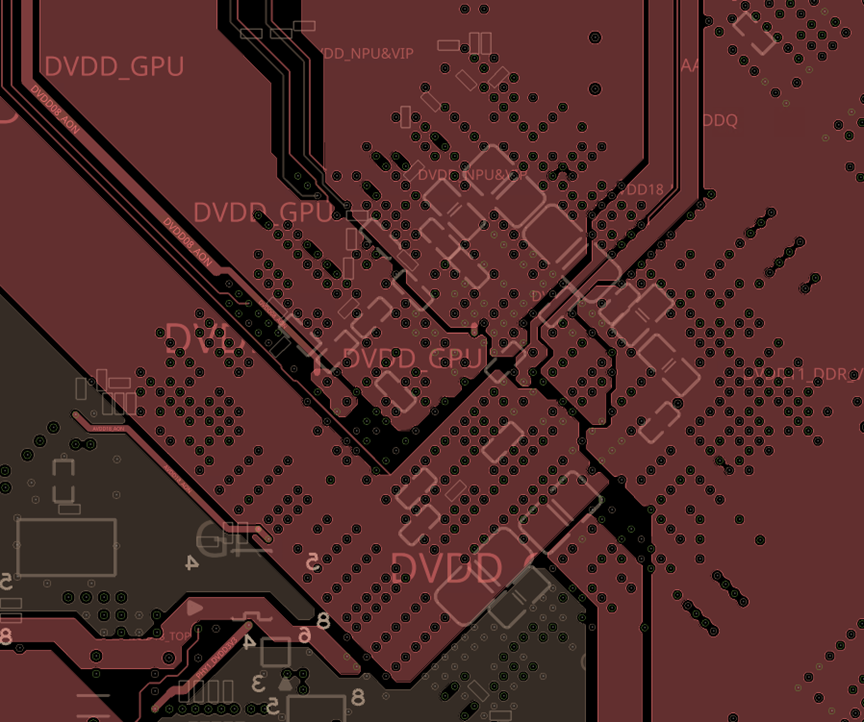

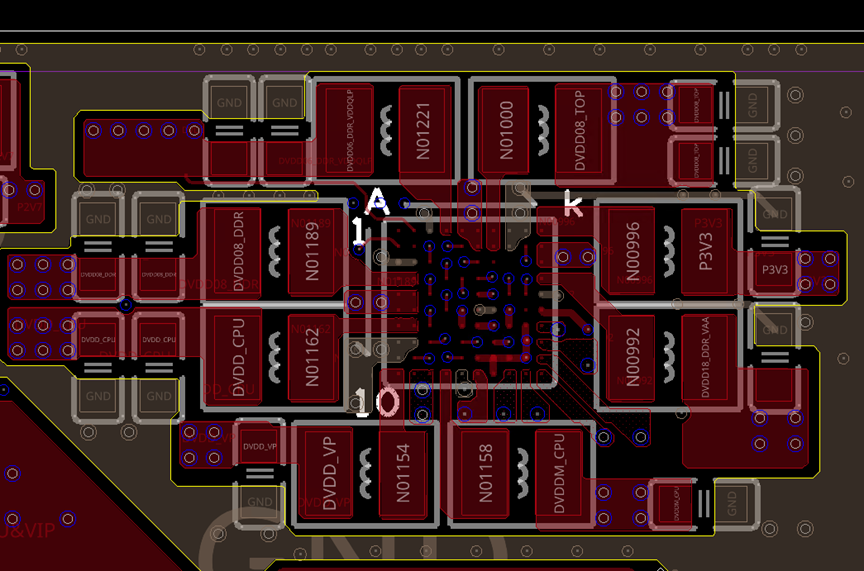

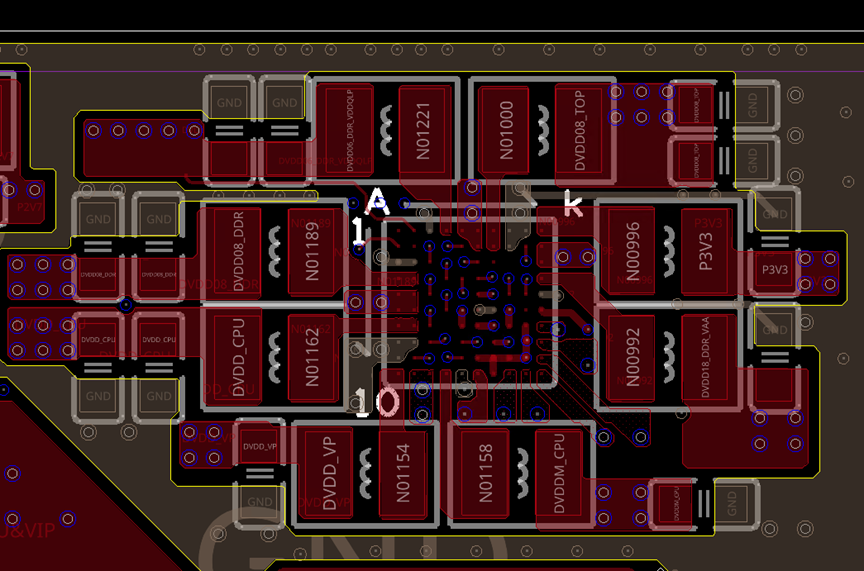

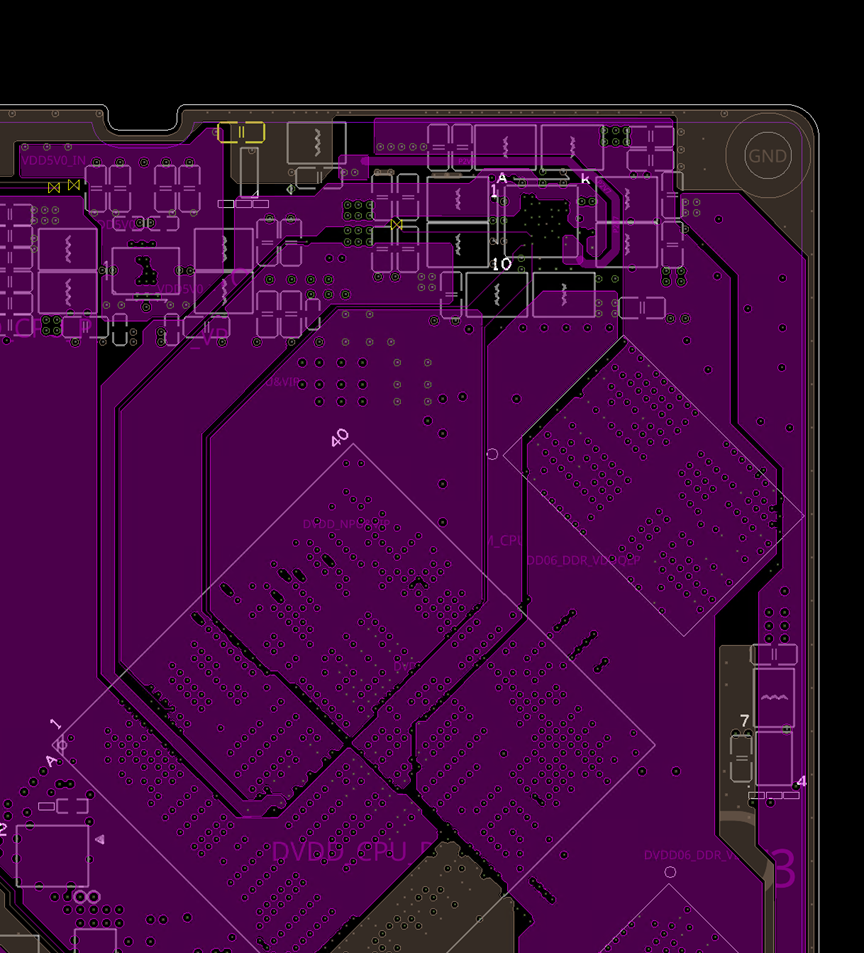

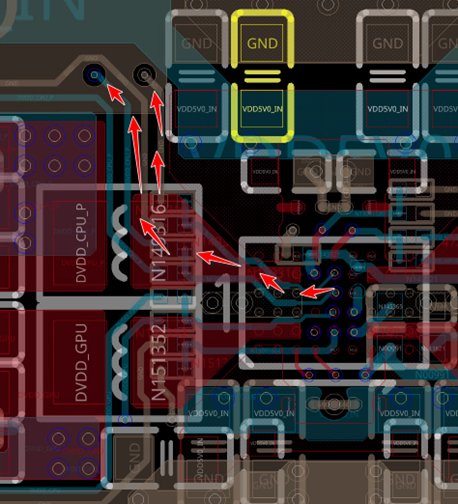

如下图电源层平面覆铜情况,有规则的放置过孔,可使各种电源有尽量大覆铜通道,有效提高电源供电质量。

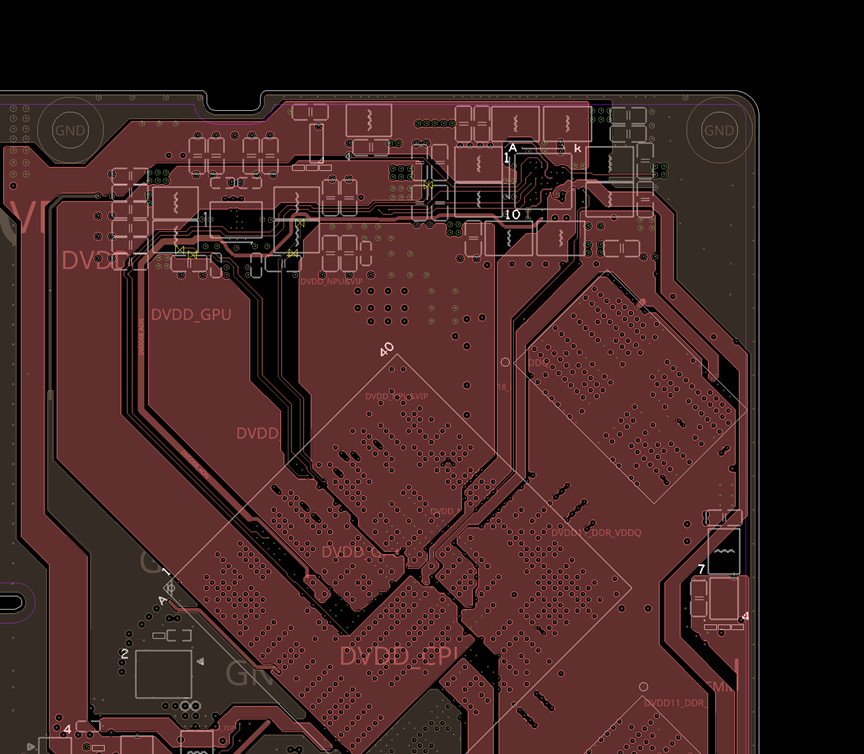

如下图,有规则的放置过孔后,层走线可以使用 3.5mil 线宽 Fan- out。

Layout 通用建议

allegro 建议

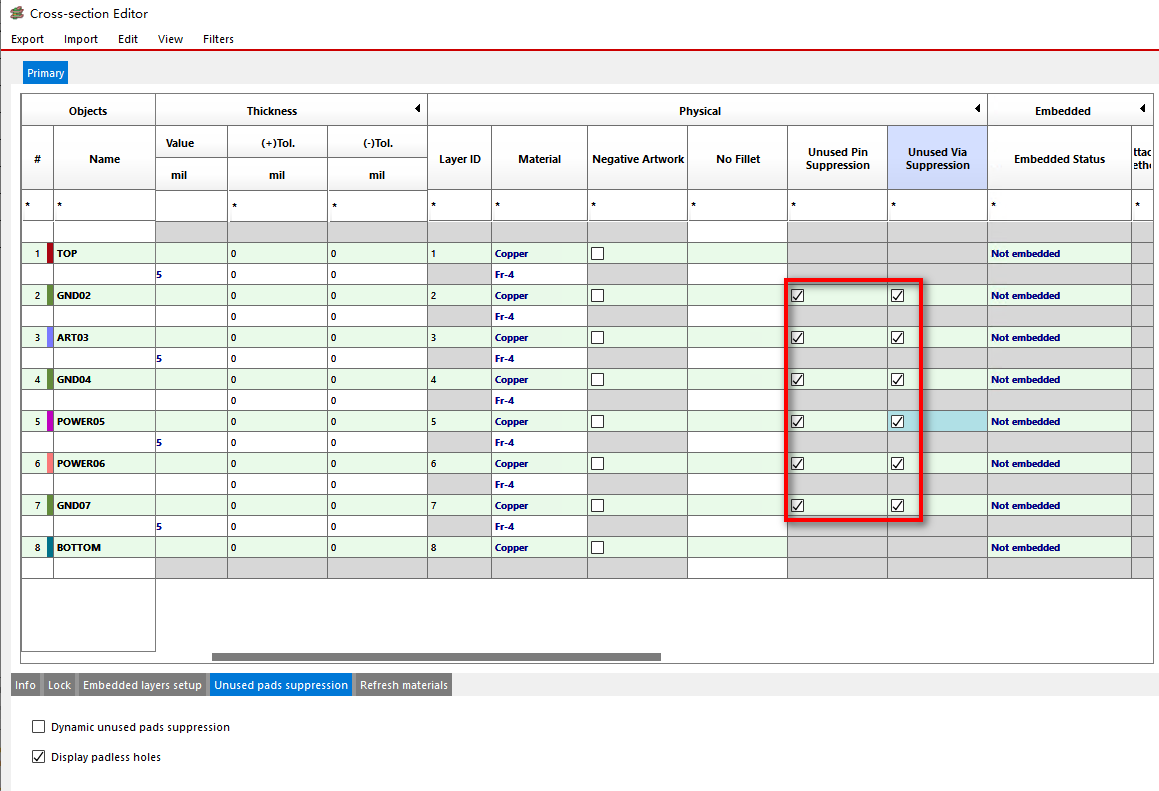

非功能孔环会破坏铜皮以及增大过孔的寄生电容,建议删除内层的非功能孔环及插件焊环,增强平面铺铜的完整性。allegro 中取消内层非功能性孔环及插件焊环的设置方式:

选用allegro 17.4 版本:Xsection-Physical-Unused Pads/Via Suppression,勾选要取消的Pins及Vias。

布局建议

-

除非结构限制及等长需求,各个接口尽量靠近主芯片 A210-1DIE-FCBGA 放置,总的连线尽可能短,特别是关键信号线尽量短。

-

元器件的排布要充分考虑调试、维修及散热。

-

满足工艺前提下,各个电路模块布局尽量均衡、紧凑、美观,减少环路面积。

-

不同的电路模块间可适当拉开间距,减小模块间的相互干扰,特别是高频元器件的间隔要充分。

-

去耦电容的布局要尽量靠近 IC 的电源管脚,使电源和地之间形成的回路最短。

-

时��钟信号的串接电阻靠近发送端放置,如 eMMC clk 的串接电阻,靠近 A210-1DIE-FCBGA(SoC)侧放置。

-

TX 串接电阻靠近发送端放置,RX 串接电阻靠近接收端放置,管脚和电阻之间走线建议控制在 400mil 以内。

比如 GMAC 的 TXD0-TXD3,TXCTL,TCLK 的串联匹配电阻靠近 A210-1DIE-FCBGA(源端),RXD0-RXD3,RXCTL,RXC 的串联匹配电阻靠近 PHY 端。

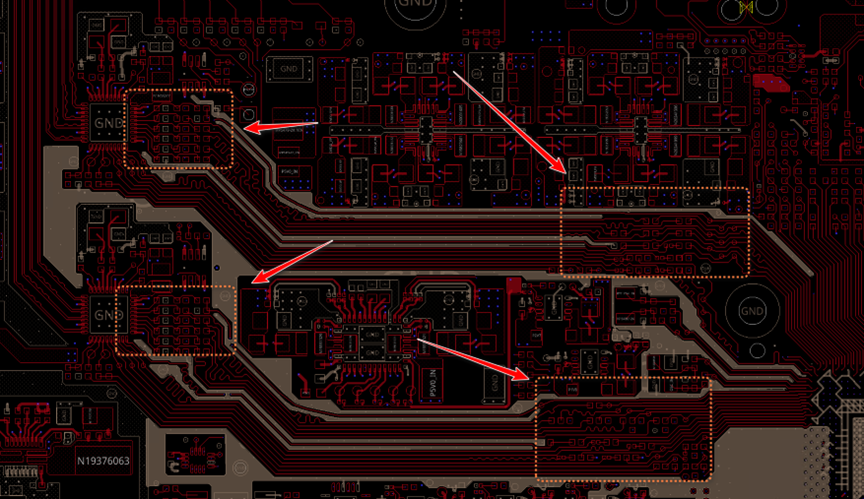

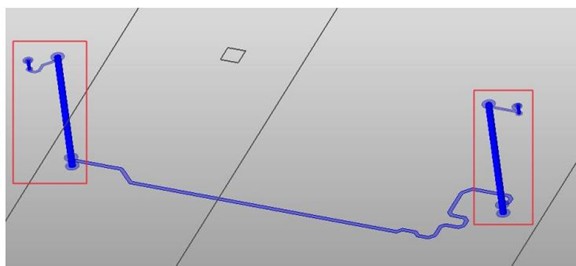

GMAC 串接电阻放置示意图如下。

GMAC RX串接电阻放置示意图如下。

-

ESD必须靠近接口放置,耦合电容建议靠连接器放置。

ESD放置示意图如下。

耦合电容放置示意图如下。

走线建议

-

走线长度应包含过孔。

-

走线尽量减少拐角,拐角建议用 135 度代替 90 度。

-

移除所有非功能焊盘。

-

避免在时钟器件(如晶体、晶振、时钟 buffer)、开关电源、磁类器件、插件过孔等周边布线。

-

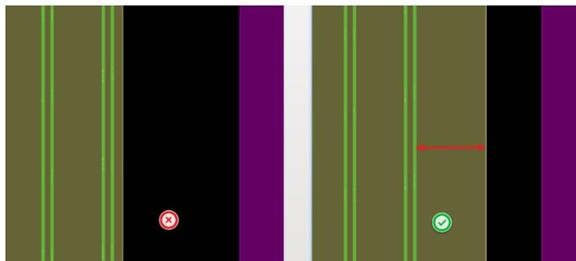

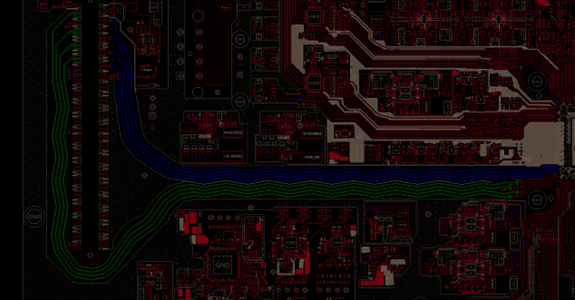

高速 SERDES 信号建议间距拉开,TX、RX 之间包地隔开或拉开足够距离。

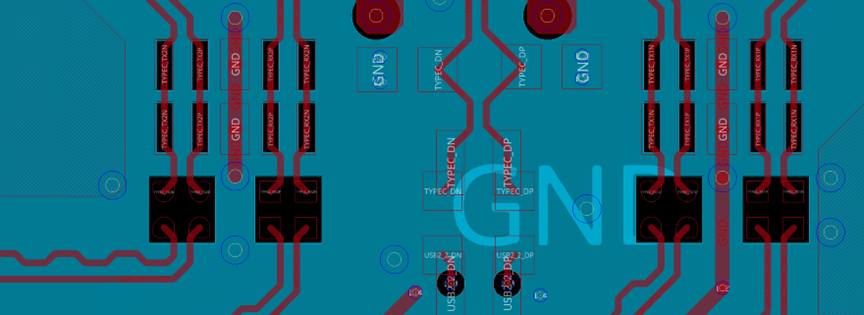

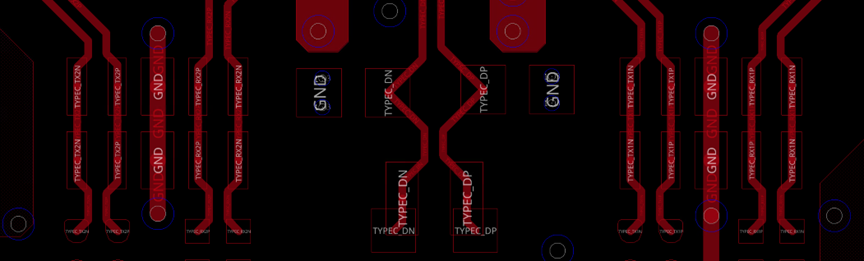

USB3走线TX RX包地隔离示意图如下。

-

避免高速信号跨区,建议高速信号距离参考平面的边沿至少有 40mil。高速信号参考面边沿示意图如下。

-

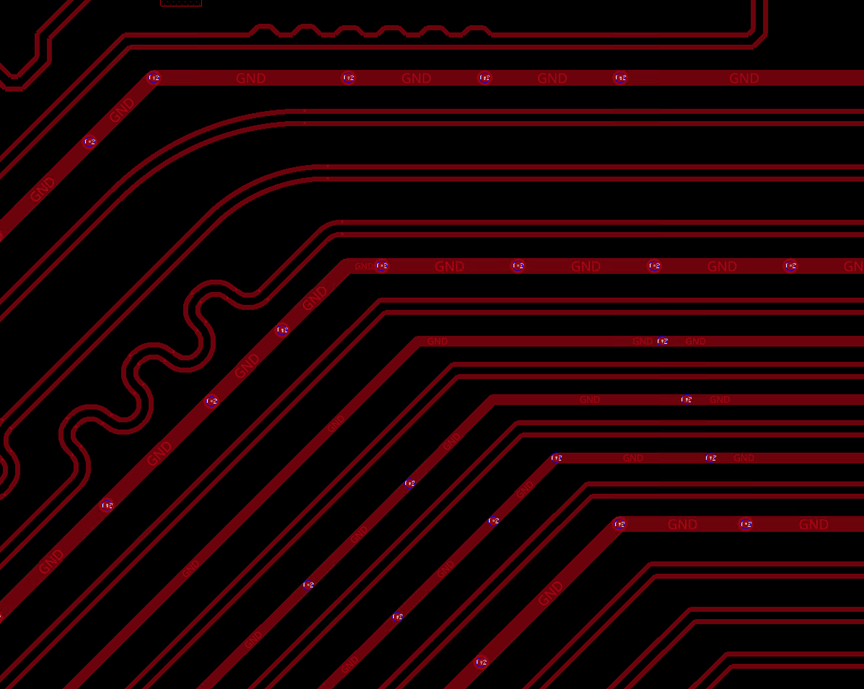

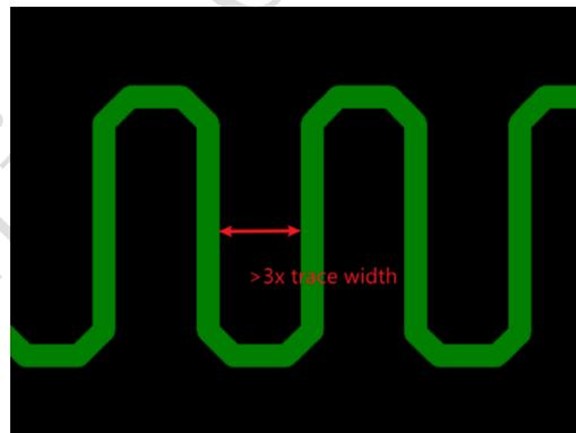

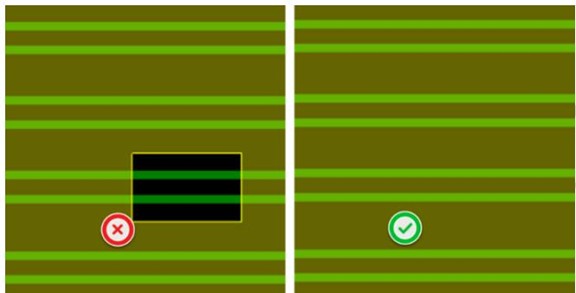

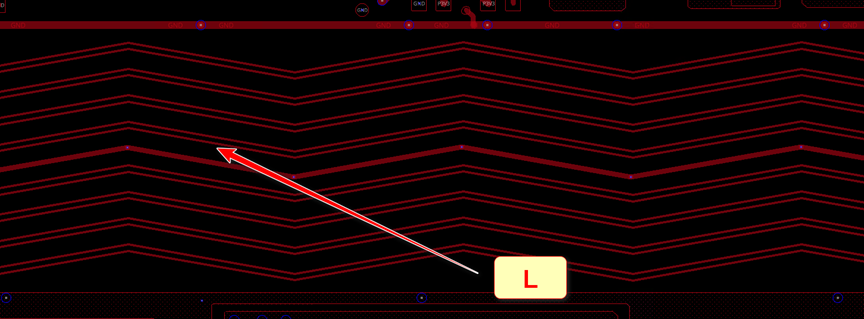

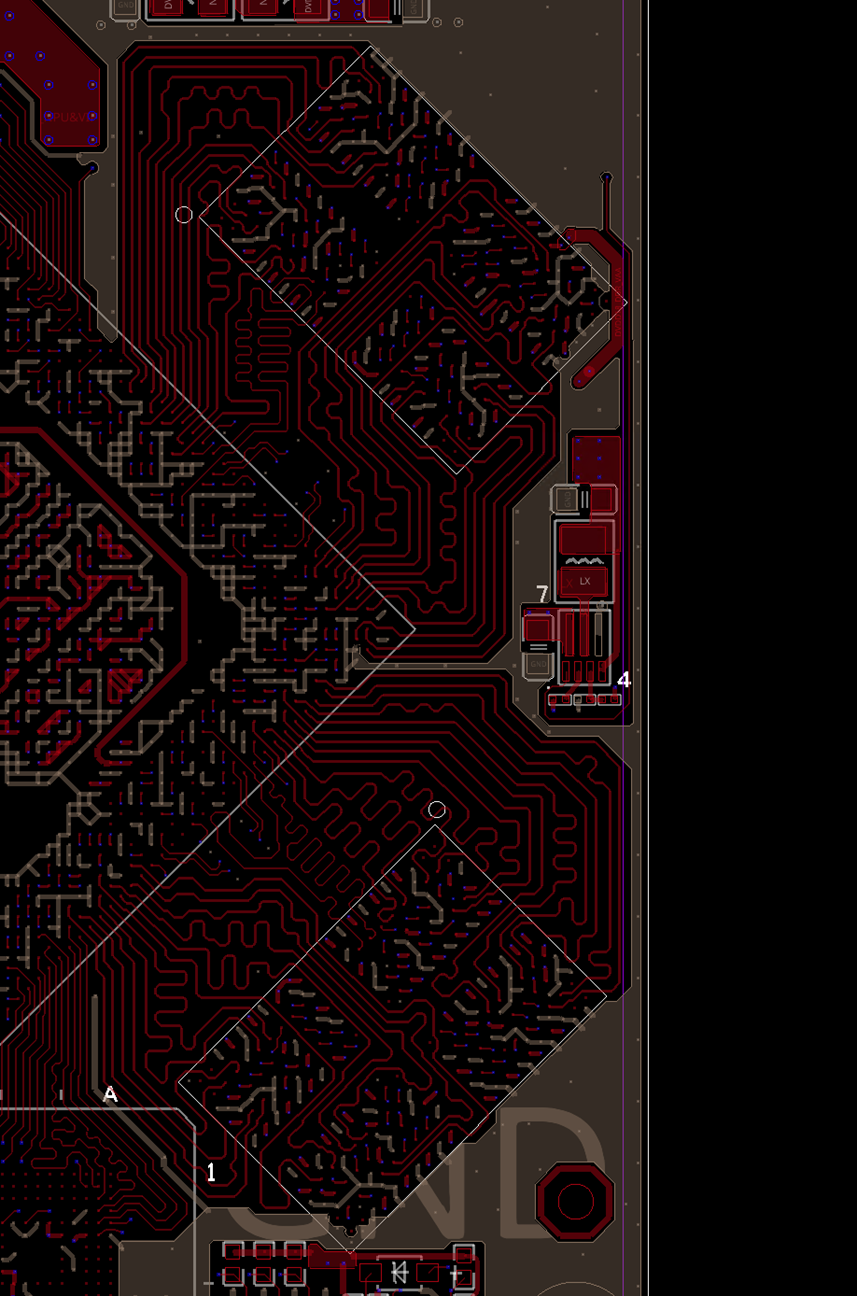

建议按如下蛇形绕线示意图走蛇形绕线,以降低绕线带来的串扰。

-

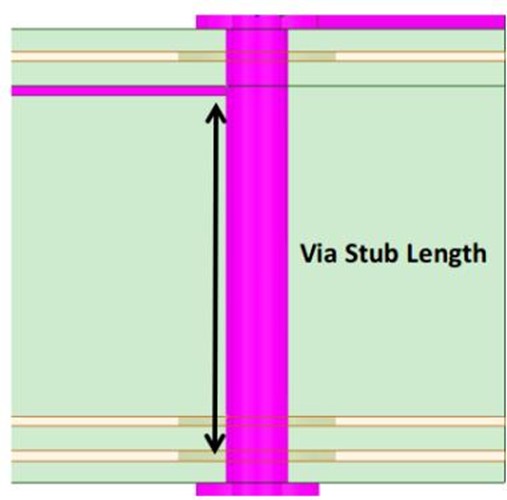

尽量减小残桩长度,建议残桩长度为零。走线残桩示意图如下所示。

-

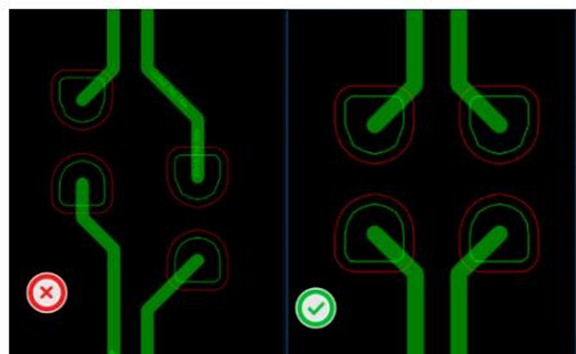

由于表贴器件的焊盘会导致阻抗降低,为减小阻抗突变的影响,建议在表贴焊盘的正下方按焊盘大小挖去一层参考层。常用的表贴器件有:电容、ESD、共模抑制电感、连接器等。参考层挖空示意图如下所示。

-

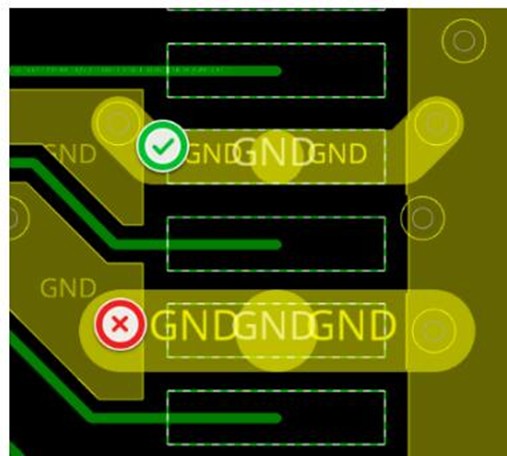

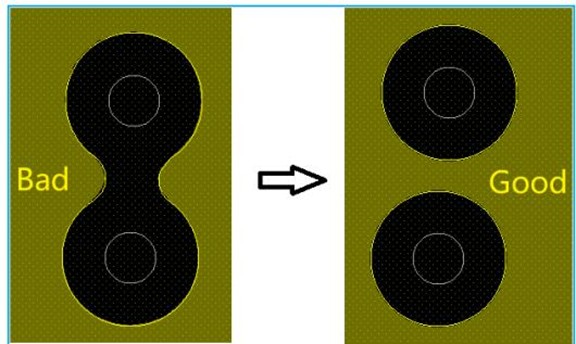

连接器位置铺铜时,注意地铜皮不要超过地焊盘。焊盘铺铜示意图如下所示。

-

建议在高速连接器的每个地焊盘至少打一个地通孔,并且通孔要尽量靠近焊盘。连接器焊盘通孔示意图如下所示。

-

避免过孔残桩效应,尤其是残桩长度超过 12mil 时,建议通过仿真来评估过孔残桩对信号完整性的影响。过孔尾桩示意图如下所示。

-

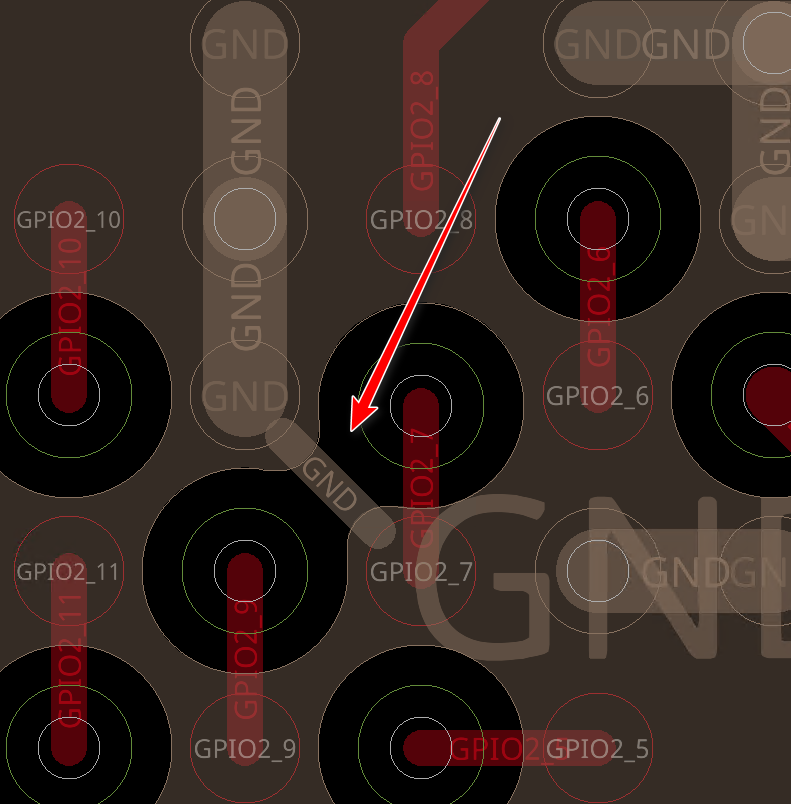

建议在 IC(如 eMMC颗粒、FLASH 颗粒等)的每个 GND Pin 各打 1 个地通孔。地通孔示意图如下。

-

建议 ESD 器件的每个 GND Pin 都打一个地通孔,且通孔要尽量靠近焊盘。ESD 器件焊盘加地�通孔示意图如下所示。

-

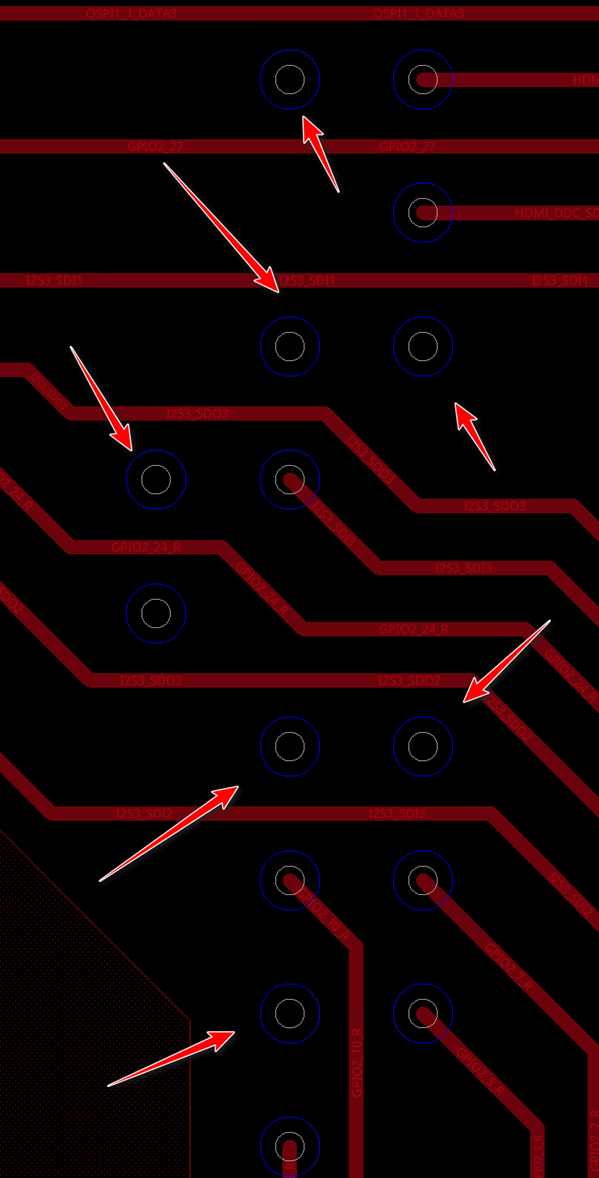

换层且换层前、后参考层为地平面时,需要在信号过孔旁边放一个伴随过孔,以保证回流路径的连续性。单端信号,建议在信号过孔旁边放置一个回流过孔以降低过孔之间的串扰。单端信号换层过孔示意图如下所示。

-

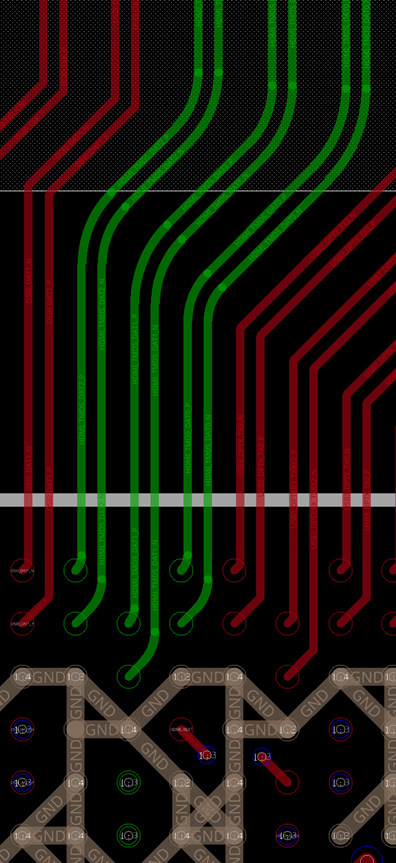

有些重要的高速单端信号,比如时钟信号、复位信号等(如 emmc_clk、emmc_datastrobe、RGMIL_CLK 等等)建议包地。包地线每隔 500mil 至少要打一个地孔。单端信号包地示意图如下所示。

-

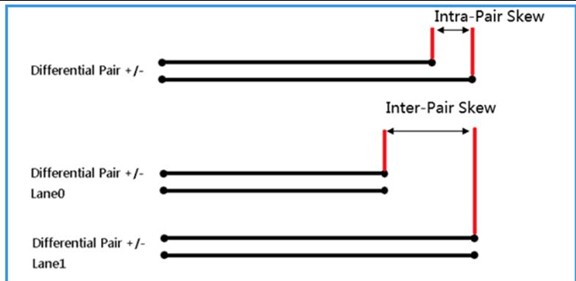

差分对内时延差是指同一对差分信号的 2 根走线之间的时延差,而差分对间时延差是指不同差分对之间的时延差。信号间距是指空气间距。差分对时延差示意图如下所示。

-

走线应有完整且连续的参考层平面。不完整参考平面示意图如下所示。

-

当走线的参考平面有跨电源层时,建议在 2 个电源层分别加对地电容以提供完整的回流路径。跨电源平面示意图如下所示。

-

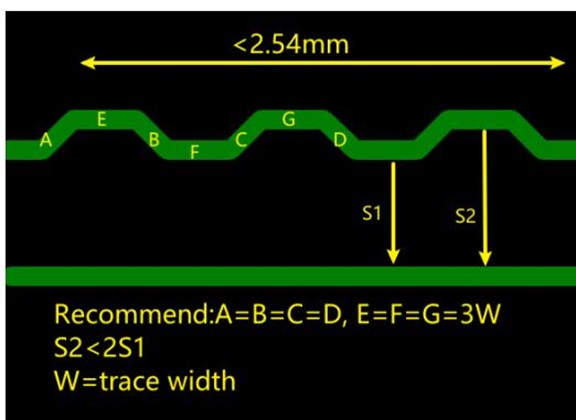

差分信号要求对内等长,即P、N之间的时延差要尽可能小。因此,当差分线P、N之间出现时延差时,就近绕线补偿。绕线尺寸需要特别注意,应满足如下图所示要求,以降低阻抗突变带来的影响。绕线补偿示意图如下所示。

-

差分信号走线换层,且换层前后参考层为地平面时,需要在信号过孔旁边放一个伴随过孔,以保证回流路径的连续性。且信号过孔、回流过孔均应对称放置。信号过孔与伴随过孔示意图如下所示。

-

差分对走线应对称。对称走线示意图如下所示。

5GT/s 及以上高速信号布线建议

A210-1DIE-FCBGA 部分接口的信号能工作在 5GT/s 及以上速率,由于速率很高,PCB设计要求会更严格。在Layout走线建议章节基础上,需要按本章节的要求来布线。

-

BGA 焊盘区域挖参考层。建议在 A210-1DIE-FCBGABGA 区域,挖掉这些信号正下方的 L2 层参考层焊盘参考第三层,以减小焊盘电容效应以及阻抗控制。挖空尺寸 R 约为 7mil。焊盘参考层挖空示意图如下所示。

-

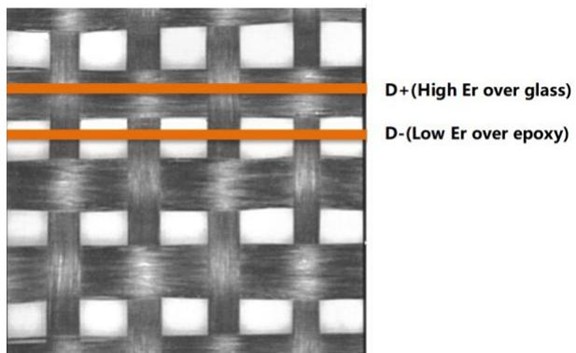

避免玻纤编织效应。玻纤编织效应是指 PCB 基板是由玻璃纤维和环氧树脂填充压合而成,这两种材料的介电常数不一样。当差分线的 D+ 走线的下方是树脂填充而 D- 走线下方是玻璃纤维作为填充时,会导致 D+ 和 D- 走线的特性阻抗不同,两条走线的时延也会不同,导致差分对内的时延差进而影响眼图质量。玻纤编织效应示意图如下所示。

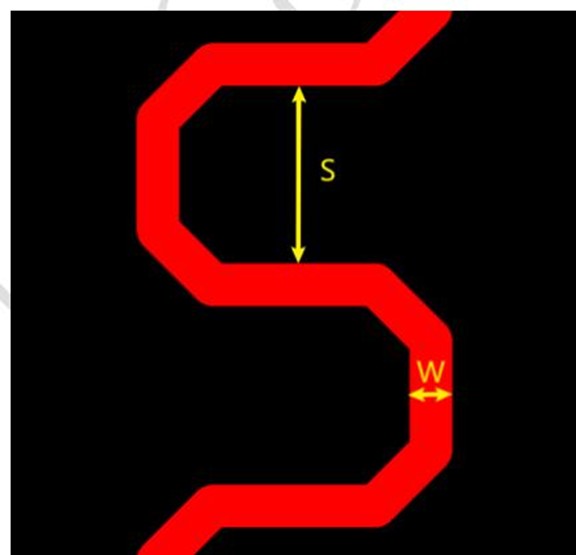

当接口的速率达到 5GT/s 且走线长度超过 2inch,需谨慎处理好玻纤编织效应。建议采用以下方��式来避免玻纤编织效应带来的影响。使用 10 度走线时,下图中的 W 至少要大于 3 倍的玻纤编织间距。推荐值 W=60mil θ=10°,L=340mil。 L 至少要大于 240mil,以跨越任何可能的玻纤编织结构。10度走线示意图如下。

模块 PCB 设计建议

- 各个接口/功能模块布局时,除非结构限制及等长需求,各个接口尽量靠近 A210-1DIE-FCBGA 放置,走线尽量短,少换层,不交叉。

- 建议最小系统包含 A210-1DIE-FCBGA、LPDDR4/4x 以及 PMIC 的布局布线完全拷贝我司提供的参考设计。

- 在不影响电源平面的前提下,A210-1DIE-FCBGA(SoC)下方的各个功能区域应尽量多的打回流地过孔。

- 各个接口电路/功能模块的所有信号尽量按组走在一起,并整组包地,与其它模块的信号做隔离,降低相互间的干扰,包地的地过孔间距 ≤300mil ,所有信号的参考层尽量为完整的地平面,避免出现连续的过孔阻断信号的回流路径的情况。

- 信号需要换层时,建议在小于 30mil 距离的位置添加回流地孔,差分信号的两个回流地孔需要对称放置。

- A210-1DIE-FCBGA(SoC)下方相应的电源域的去耦电容务必靠近对应的电源管脚放置,每个电容尽量配对一比一及以上的电源孔和地孔,电源 Fan-out 尽量宽,并尽量加粗到 10mil 及以上。

- 颗粒/接口电路的去耦��电容必须靠近对应的管脚放置,走线尽量短粗,需要满足各自的电流需求。

- 请参考Layout走线建议及以下各个接口的几点建议。

Clock 电路 PCB 设计

在时钟电路的 PCB 设计中,请注意以下几点。

- 晶体电路布局需要优先考虑,布局时应与芯片在同一层并尽量靠近放置以避免打过孔,晶体走线尽可能的短,远离干扰源,尽量远离板边缘。

- 晶体以及时钟信号需要全程包地处理,包地线每隔 200-300mil 至少添加一个 GND 过孔,并且必须保证邻居的地参考面完整。

- 晶体电路布局时如果与芯片不同层放置,晶体走线及必须全程包地处理,避免被干扰。

- 晶体下方投影区域禁止任何走线,避免噪声耦合进入时钟电路。

- 晶体下方的顶层,可以围绕放置地环。地环通过过孔与相邻的接地层连接,以隔离噪声。

- 晶体下方的第二层保持完整的地参考平面,避免任何走线分割,有助于隔离噪声保持晶体输出的。

A210-1DIE-FCBGA 晶体布局和走线示意图如下所示。

PMIC/Power 电路 PCB 设计

ZH70809 电源 PCB 设计

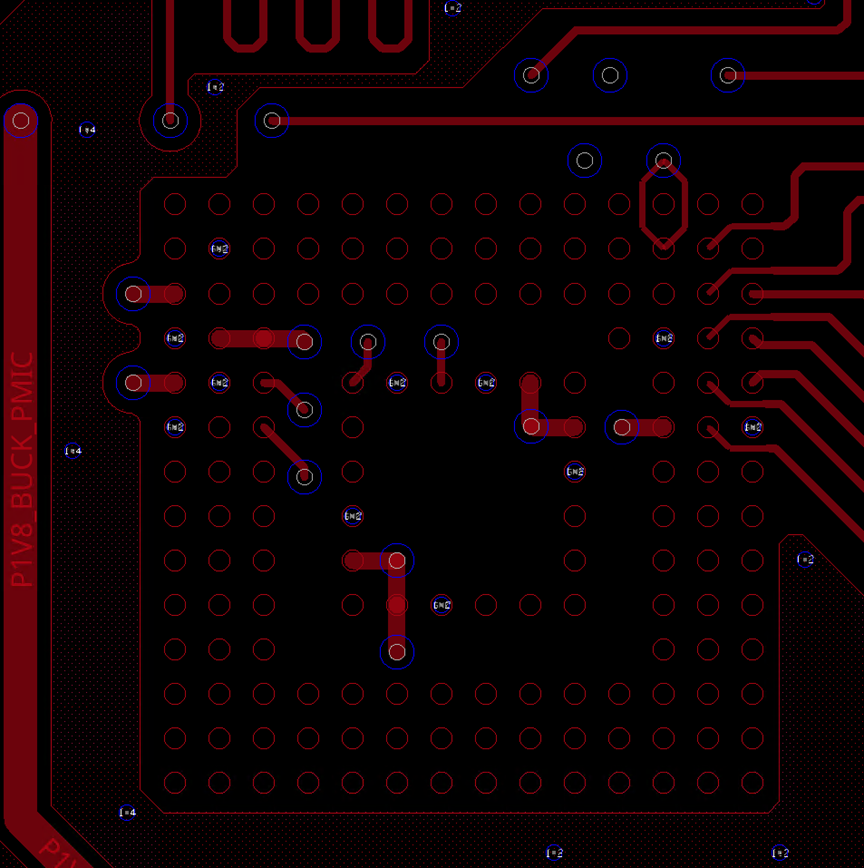

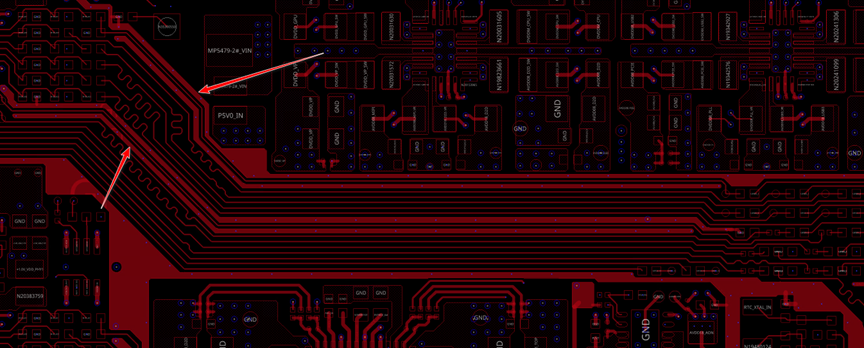

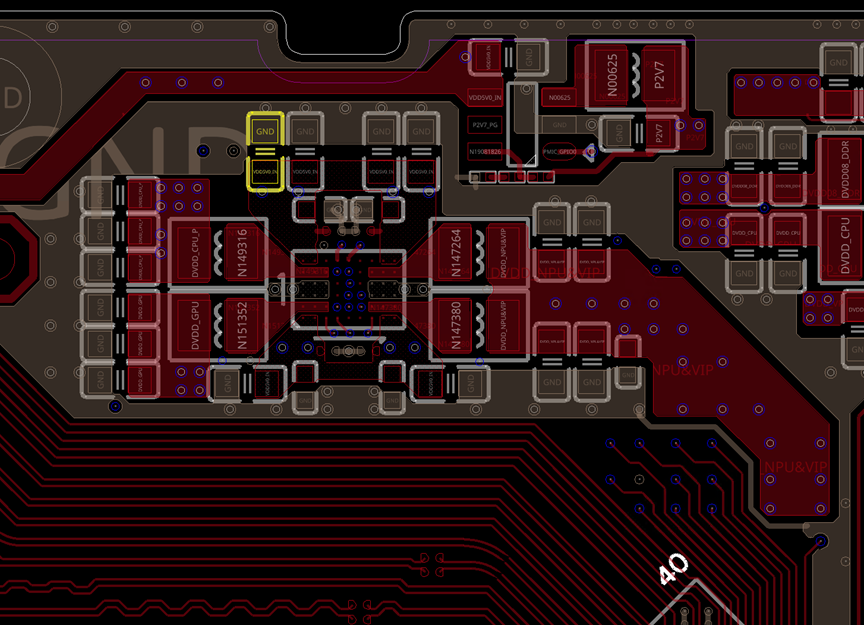

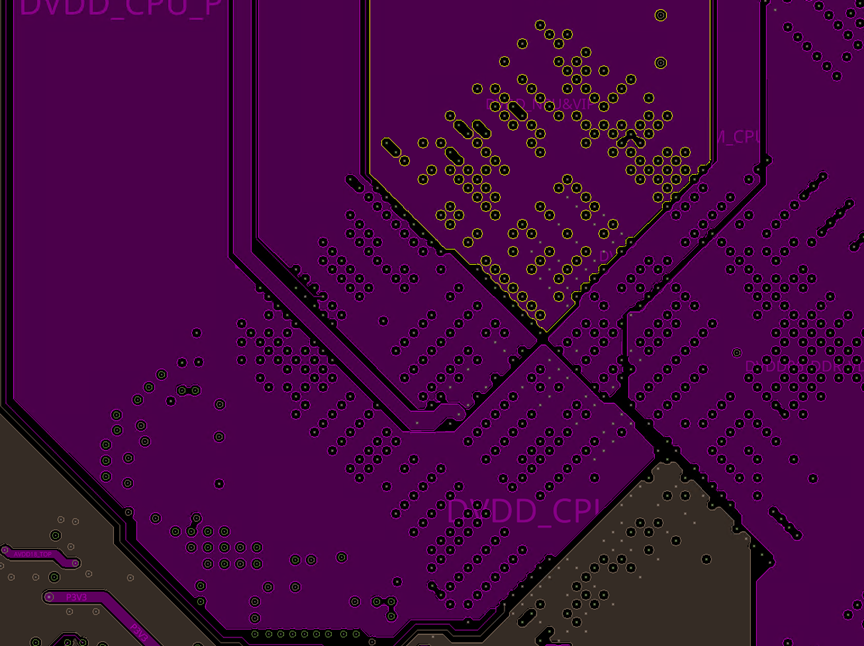

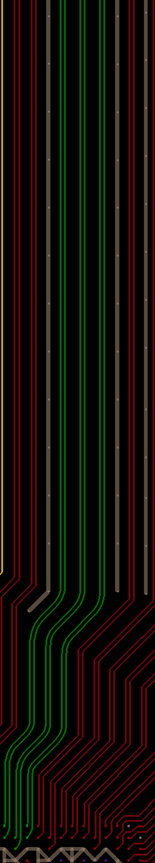

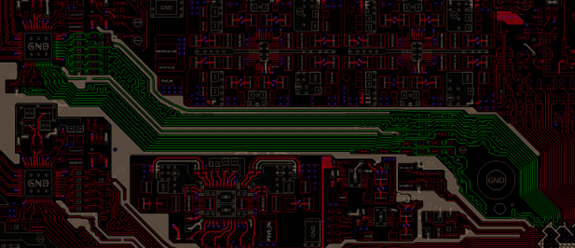

整体布局时,从电源质量角度上看 ZH70809 尽量靠近 A210-1DIE-FCBGA(考虑散热设计时,需要适当放置,不要太靠近也不能离的太远),摆放方向时,尽量优先考虑 ZH70809 的 BUCK 输出电流比较大的电源到 A210-1DIE-FCBGA的走线(覆铜)是顺的,尽量不要交叉。ZH70809 过孔分布如下图所示。

注意事项

- 大电流 BUCK 输入输出电容的负极要有和正极有一样多数量的过孔,才能起到比较好的虑波效果(很多工程师容易忽略电容负极的电源过孔)并建议将 GND 铜皮大面积连接在一起。

- 不建议电源部分器件的焊盘及或孔做“热焊盘”,应该用铺铜全部覆盖。ZH70809 的电源管脚部分建议覆铜,所有管脚通过覆铜和外面连接,覆铜和 PIN 一样宽,不得超过 PIN 宽,防止制板焊盘变大后,贴片容易连锡。

ZH70809 过孔分布示意图如下所示。

-

ZH70809 的 BUCK1-8 PCB 设计要求如下。

- 电源输入过孔要求:对于需要打过孔的地方,VCC5V 如果合并供电至少需 2 个 10Mil (内径)过孔,如果分开各自需要 1 个及以上的 10Mil (内径)过孔。

- 输入电容要求:必须离芯片尽可能近,如果输入电容放在芯片的背面,让输入电容与 VCC 和 GND 的连接环路尽可能小。

- SW 路径要求:应当保证 SW 的走线尽可能短粗,尽可能铺铜处理以提高过流能力及电源效率。

- 电源输出过孔要求:根据实际应用电流情况来确定过孔数量。

ZH70809 电源走线示意图如下所示。

ZH70300 电源 PCB设计

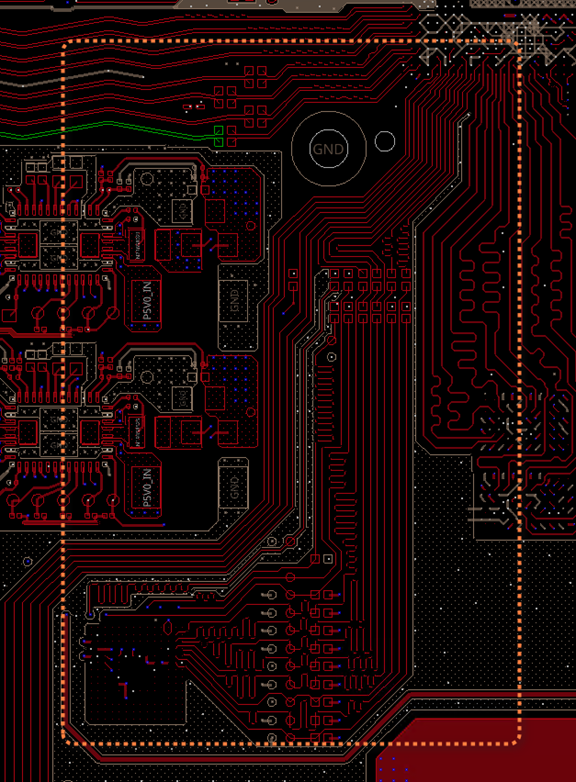

ZH70300 Fan-out 用盘中孔设计,选用 6Mil(内径)12MIL(外盘)。ZH70300 PCB Fan out 示意图如下。

DC-DC低压大电流供电反馈补偿建议

A210-1DIE-FCBGA 的 PMIC 方案中,针对几个大电流 BUCK 供电电源,结合电压、电流、纹波以及 PCB 布局情况,分为 2 类反馈补偿策略。

-

近端反馈

输出电容 Cout 靠近 DCDC,反馈采样点 (FB/VOUT) 接在输出滤波电容 Cout 的末端。近端反馈 PCB Layout 示意图如下所示。

-

远端反馈。远端反馈 PCB Layout 示意图如下所示。

电源 PDN 及电容滤波要求

| 电源类型 | PDN Ztarget for PCB (2MHz~20MHz) |

|---|---|

| DDR VDDQ | VDDQ = 5%×1.1V/1.06A = 0.052 for SoC VDDQ = 5%×1.1V/2A = 0.025 for DRAM |

| DDR VDDQLP | VDDQLP = 3%×0.6V/0.7A = 0.026 for SOC ≥ 3%×0.6/1.4A = 0.013 for DRAM |

| AVDD08_MIPI (即 DVDD08_TOP) | Ztarget=5%×0.8V / 3.6A =0.011ohm |

| DVDD_DDR | Ztarget=5%×0.8V/2.3 = 0.017 |

| DVDD08_D2D | Ztarget =5%×0.8V/2.4A =0.016 |

| AVDD08_D2D | Ztarget =5%×0.8V/0.8A =0.05 |

| C908 | Ztarget =5%×1V/ 3.522A =0.014 |

| C920 | Ztarget =5%×1V/ 5.547A =0.009 |

| NPU_VIP | Ztarget =5%×1V/ 13.768A =0.0036 |

| NPU_SS | Ztarget =5%×1V/ 2.258A =0.022 |

| GPU | Ztarget =5%×0.8V/ 1.419A =0.028 |

| VP | Ztarget =5%×0.8V/ 1.2A =0.033 |

| DVDDM | Ztarget =5%×0.8V/0.3A = 0.133ohm 对 DVDDM |

| 0.8V 外设数字、模拟电 | Ztarget= 5%×0.8V/0.4A = 0.1ohm |

| 1.8V | Ztarget=5%×1.8V/ 0.4A =0.225ohm |

| 3.3V and PLL | Ztarget=5%×3.3V / 0.1A =1.5ohm for 3.3V Ztarget= 5%×0.8V/0.1A = 4 ohm for PLL |

核心大电流电源的过孔及电容配置参考如下。

| A210-1Die-BGA 电容参考板 | |||

|---|---|---|---|

| 过孔 | 0201 电容放置于芯片下方的 PCB Bottom 层 | 其它电容,按电容封装大小,尽量靠近芯片 | |

| NPU_VIP | 12 个通孔 | 15 个 0201_1uF | 220uF+100uF+10uF |

| NPU_SS | 9 个通孔 | 6 个 0201_1uF | 10uF |

| C920(CPU_P) | 17 个通孔 | 10 个 0201_1uF | 10uF+22uF+100uF+220uF |

| GPU | 7 个通孔 | 6 个 0201_1uF | 10uF |

| VP | 6 个通孔 | 5 个 0201_1uF | 10uF |

说明:

- 建议参考小系统设计,尽量不要更改电容配置。选择更小型号的封装。

- 如使用盲埋孔,注意打孔位置不要离开太远,以最短路径连接 Ball 与 Capacitor。

- 通孔数尽量多。但注意不要把电源平面打穿。

A210-1DIE-FCBGA 其他 LDO 电源

A210-1DIE-FCBGA(SoC) 下方的其它电源,尽量每个 Ball 都有一个对应的电源过孔,在不影响电源通路情况下,电源过孔旁边尽量增加 GND 回流过孔。电源走线的相邻层最好有一层完整的 GND 回流平面。

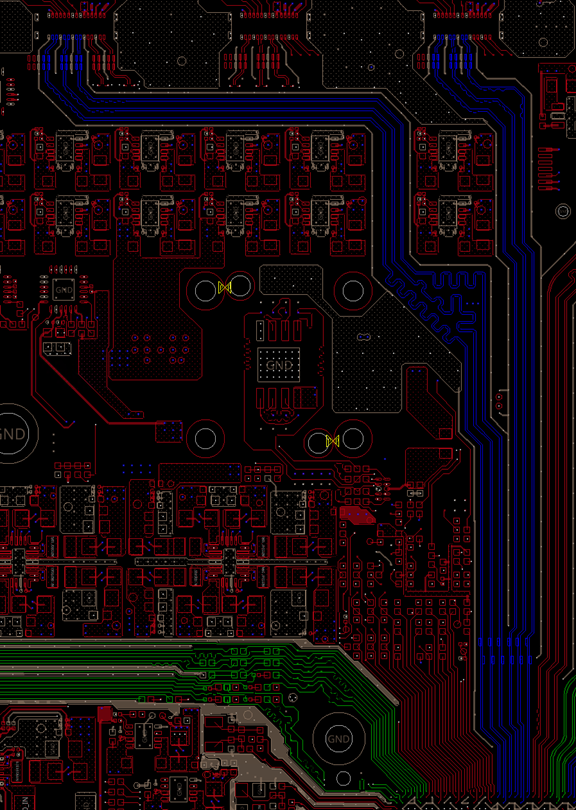

A210-1DIE-FCBGA 其它电源的去耦电容,必须靠近芯片管脚放置,背面贴时放在芯片管脚背面,尽量形成先经过电容焊盘再到芯片管脚,电容一个 GND 焊盘尽量对应的一个 GND 过孔。

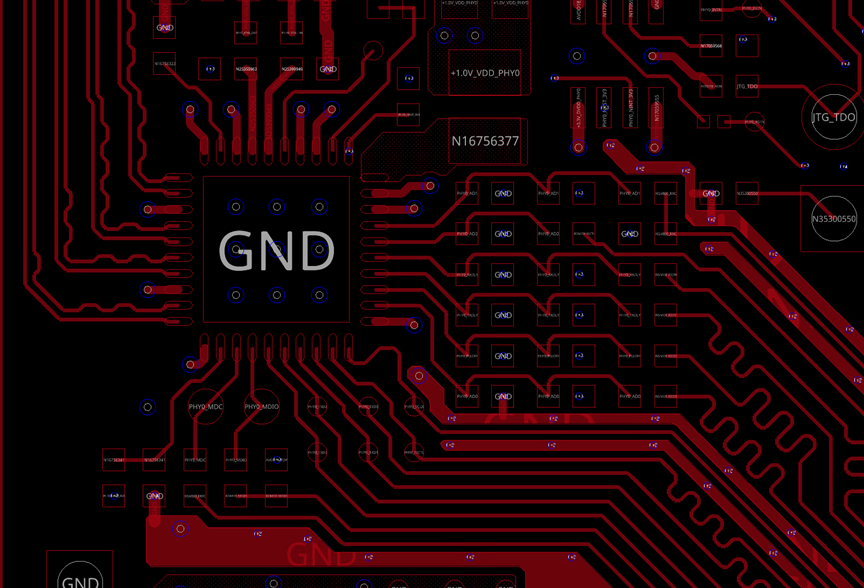

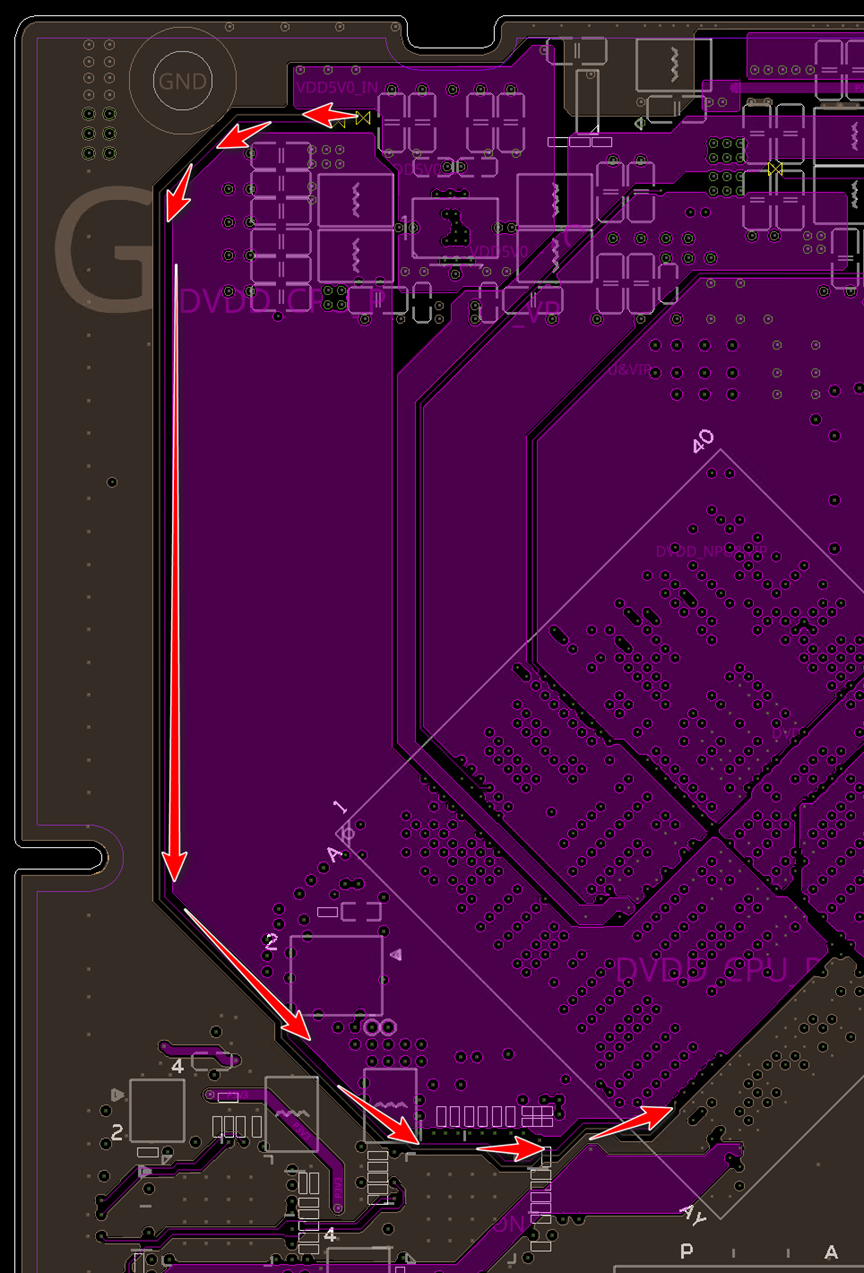

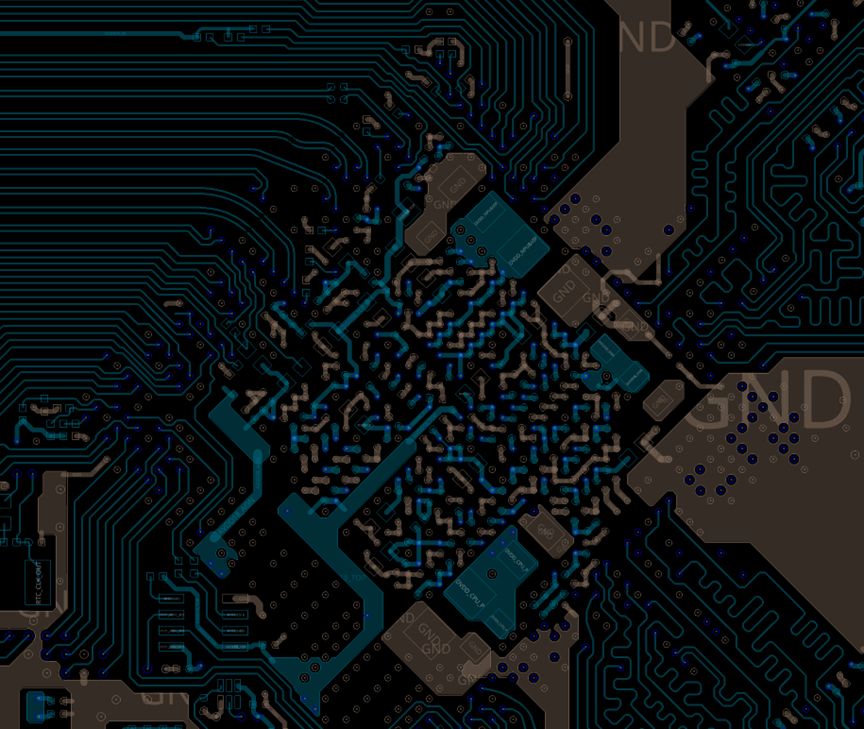

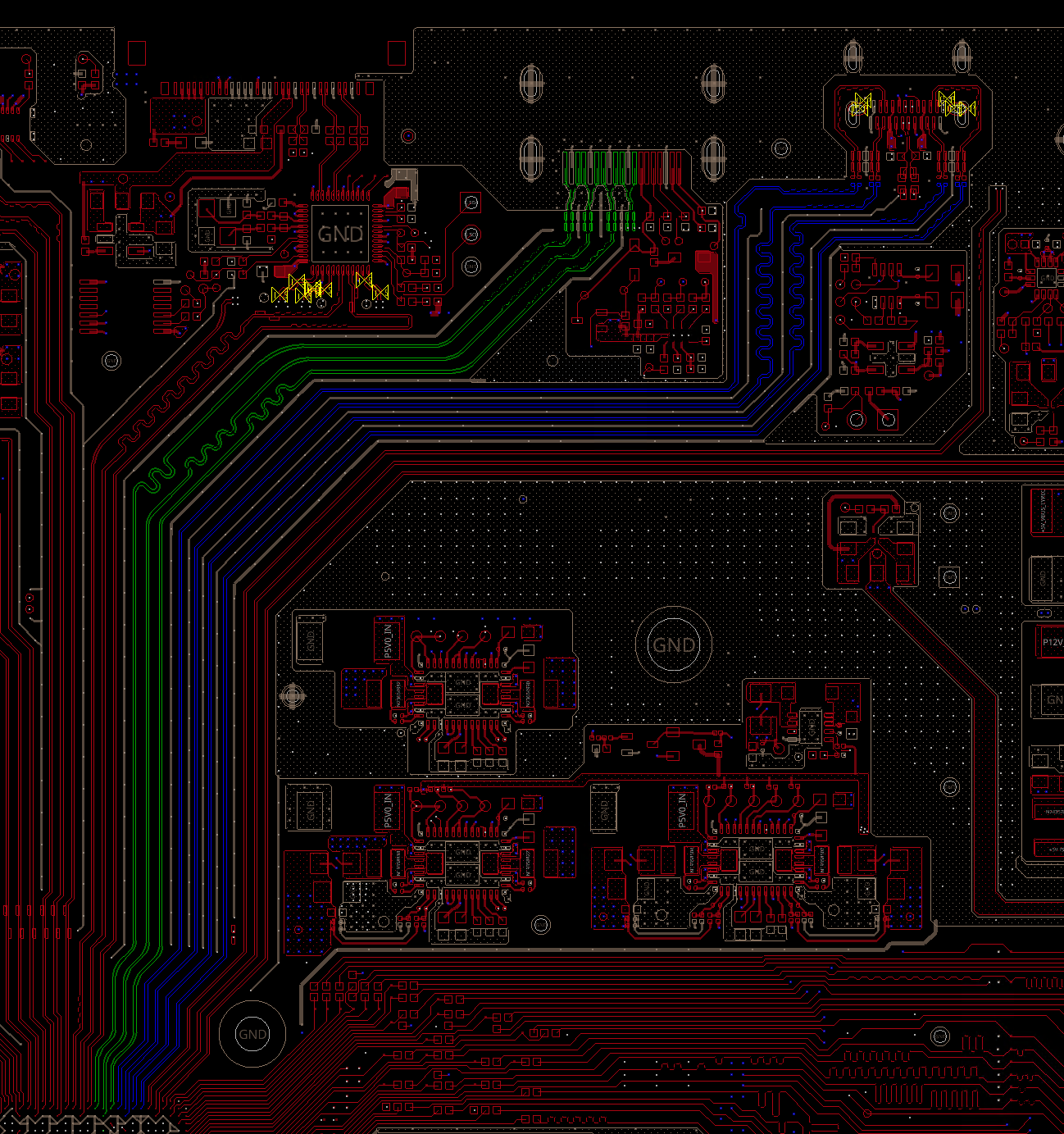

A210-1DIE-FCBGA 其它电源管脚走线和过孔如下图。

A210-1DIE-FCBGA 其它电源内层 Fan-out 如下图。

A210-1DIE-FCBGA 其它电源管脚背面去耦电容放置如下图。

A210-1DIE-FCBGA 的 VSS 管脚

建议在 A210-1DIE-FCBGA(SoC) 芯片的 VSS 管脚,不影响电源平面的情况下,尽可能多的回流地孔,在顶层走“井”字形,或者走线布满,交叉连接,建议走线线宽 10mil。

A210-1DIE-FCBGA(SoC) 芯片的相邻层必须是一个完整的 GND 平面,保证主参考地靠近 CPU 的 Ball,地过孔需要把 A210-1DIE-FCBGA 的 VSS 管脚和所有的地平面连接起来,用于保证电源完整性,提供更优的 SI、PI 条件以及加强 PCB 的散热。

A210-1DIE-FCBGA BGA 区域过孔分布如下图。

LPDDR4/4X PCB 设计

由于 A210-1DIE-FCBGA LPDDR4/4X 接口速率 4266bps,PCB 设计难度大,所以强烈建议使用我司提供的 DDR 模板。如果自行设计 PCB,请参考如下 PCB 设计建议,并通过时域眼图仿真以完成 SI 评估。

| 信号 | Constraint | LPDDR4/4x |

|---|---|---|

| Electrical | Via Count(过孔数量) | 走线 ≤2 个(含 fanout 区域) |

| Propagation Delay(长度供参考) | 走线尽量短。对于 DQ/DQS 信号,500mil~1000mil 比较合适。不超过 2inch; | |

| static phase(差分对内等长) | DQS, CK: 5mil | |

| Relative Delay(同组线等长) |

| |

| Physical | 阻抗 |

|

| Spacing | DQ | 以仿真为准,要求: PCB 走线带来的 powersum crosstalk < -40dB@0~2.1GHz 尤其注意组与组之间的距离,需要拉开 5H 以上。可能会被仿真遗漏。 |

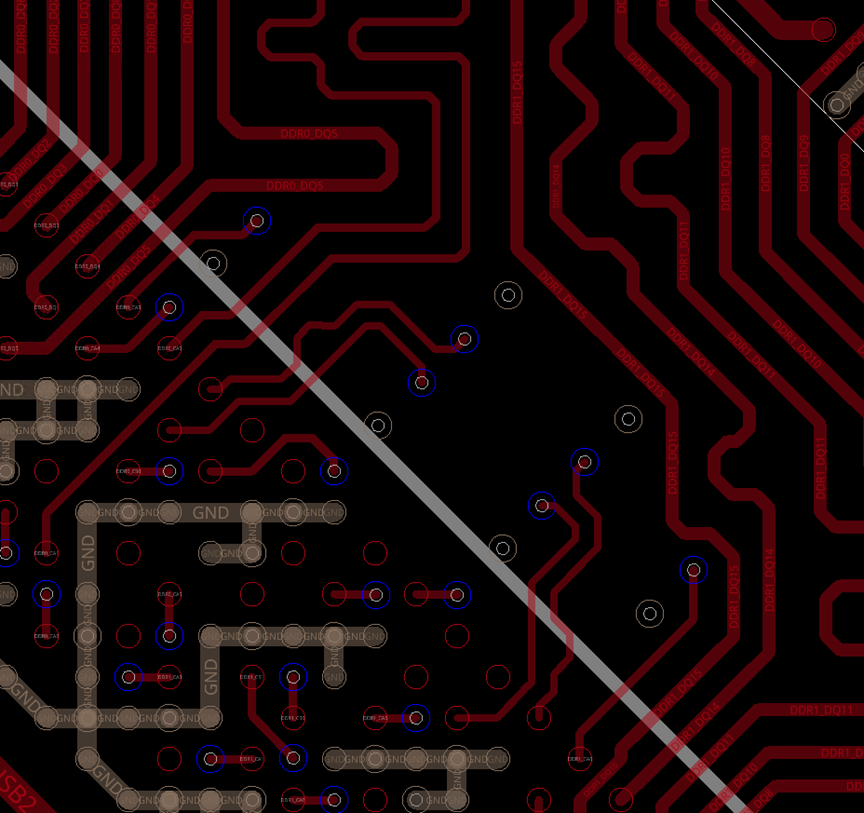

8 层通孔 PCB LPDDR4/4X区域过孔设计如下图所示。

-

信号换层前后,��参考层都是 GND 平面时,在信号过孔 25mil (过孔和过孔的中心间距)范围内需要添加 GND 回流过孔,改善信号回流路径,GND 过孔需要把信号换层前后 GND 参考平面连接起来。一个信号过孔,至少要有一个 GND 回流过孔,尽可能增加 GND 回流过孔数量,可以进一步改善信号质量。

信号过孔对应的 GND 回流过孔示意图如下。

-

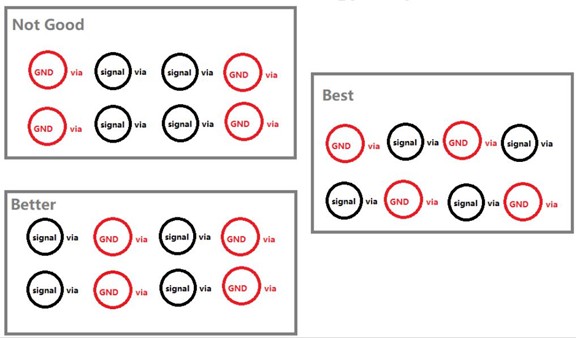

GND 过孔和信号过孔的位置会影响信号质量,建议 GND 过孔和信号过孔交叉放置如下图。如下图虽然同样是 4 个 GND 回流过孔,4 个信号过孔在一起的情况要避免,这种情况下过孔的串扰最大。

不同的过孔设计示意图如下。

-

8 层板,建议 DDR 信号走第一层、第 3 层、第 8 层。DQ、DQS、地址和控制信号、CLK 信号至少有一层完整的 GND 参考平面。数据线不建议同时参考 GND 平面和电源平面,建议全部参考地层。

-

如下 GND 走线优化参考层示意图所示,当过孔导致信号参考层破裂时,可以考虑用 GND 走线优化下参考层,改善信号质量。

-

走线距离参考层的边缘越近,信号的阻抗会越大,走线和参考层边缘的距离至�少 12mil。

-

绕线自身的串扰会影响信号延时,走线绕等长时建议 S≅3W。

-

在做等长时,需要考虑过孔的延时。过孔长度示意图如下。

-

DDR 颗粒区域,一个管脚对应一个 GND 过孔,有空间的地方尽可能增加 GND 过孔。信号 PIN 对应 GND 过孔示意图如下。

-

非功能焊盘会破坏铜皮,以及增大过孔的寄生电容,需要删除过孔的非功能焊盘。

-

调整过孔位置,优化平面的裂缝,可以改善回流路径。平面裂缝优化示意图如下。

-

LPDDR4/4X接口,DDR 颗粒的VDDQLP、VDDQ、VAA电源,建议一个管脚至少对应一个电源通孔,举例如下。

以下三图分别为:LPDDR4/4X 颗粒 VDDQ 电源过孔数量要求,LPDDR4/4X 颗粒 VAA 电源过孔数量要求,和LPDDR4/4X 颗粒 VDDQLP 电源过孔建议数量。

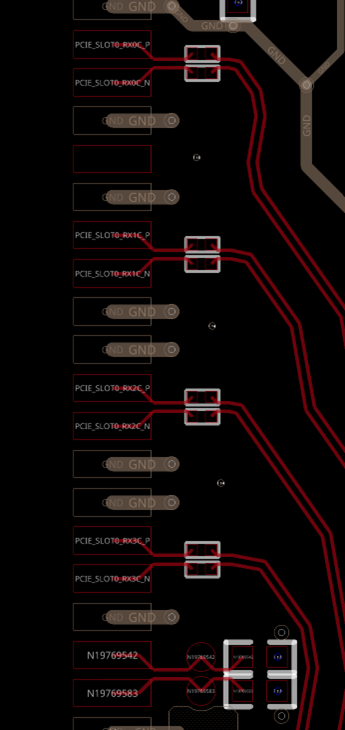

PCIe3.0 PCB 设计

| 参数 | 要求 |

|---|---|

| 走线阻抗 | 差分 85 -- 100 ohm,阻抗控制 ±10%。 说明:PCIe3.0 走线阻抗以系统设计为准。

|

| 差分对内走线误差 | 5Mil |

| 走线长度 |

其它应用需要再具体分析。 |

| 各信号所允许经过过孔数量 | 建议不超过2个。 |

| �线间距 |

其中 H 为层高。 |

SATA3.0 PCB 设计

| 参数 | 要求 |

|---|---|

| 走线阻抗 | 差分 90~100 ohm,阻抗控制 ±10%。 |

| 差分对内走线误差 | 5Mil |

| 走线长度 | A210 到 SATA 硬盘接口约 6dB@3GHz。 |

| 各信号所允许经过过孔数量 | 建议不超过2个。 |

| 线间距 |

其中 H 为层高。 |

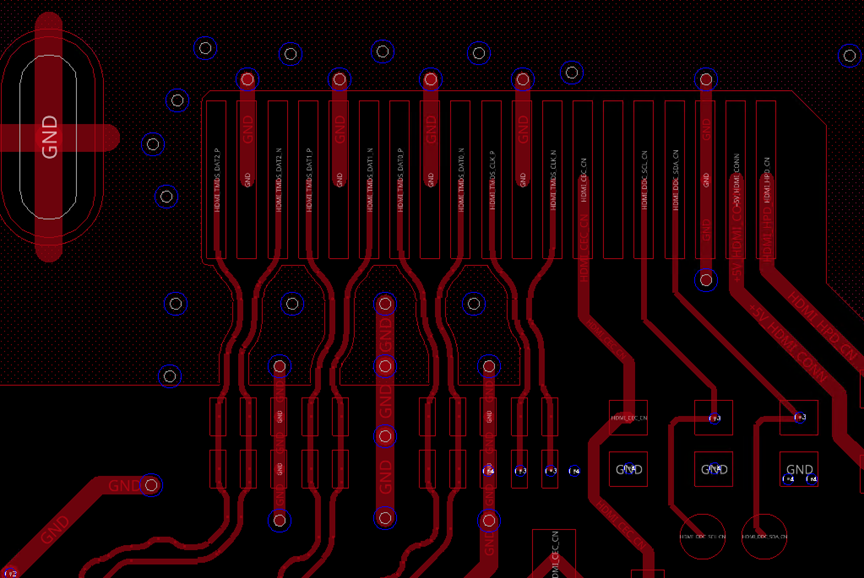

HDMI2.0 PCB 设计

| 类别 | 要求 |

|---|---|

| 阻抗 | 100 ohm。可降至 90ohm |

| Propagation Delay(长度)供参考 | 表层 4inch,可放宽 |

| Relative Delay(同组线等长) | 750mil |

| static phase(差分对内等长) | 5mil |

| TVS 寄生电容 | HDMI2.0 需要小于 0.6pF |

-

建议在 BGA 区域的以下位置加地通孔,按差分布线,建议包地处理。包地线的地孔间隔小于 150mil。

-

HDMI 设计如果是 AC 耦合模式(应用于对浪涌防护有严格要求的场合), 要在末端外加上拉电路,建议外加电路引入走线残桩长度小于 80 mil,HDMI2.0 的上拉电阻封装尽量 0201,不超过 0402。

HDMI2.1 BGA 区域扇出走线示意图如下。

USB3.1 PCB 设计

USB3.1 布线要求示意图如下。

| 参数 | 要求 |

|---|---|

| 走线阻抗 | 差分 90ohm |

| 差分对内最大时延差 | 5mil |

| 走线长度 | <5 inches M4 等级板材 |

| 线间距 | 内层间距 3xH。外层间距 11xH。 其中 H 为层高。 |

| TVS 寄生电容 | TVS 寄生电容 USB3.2 Gen2 10Gps: 小于 0.3pF。 |

USB Type C: Dp/Dn要在连接器处2面Dp0/Dp1 接起来。避免Stub。

MIPI PCB 设计

MIPI-CSI 布线要求示意图如下所示。

| 参数 | 要求 |

|---|---|

| 走线阻抗 | 差分 90ohm。 |

| 差分对内最大时延差 | <5mil。 |

| 时钟与数据之间等长 | <60mil。 |

| 走线长度 | <6 inches·M4 等级板材(具体要结合 FPC 长度应用速率进一步评估)。 |

| 各信号所允许过孔数量 | 建议不超过 4 个。 |

| 差分对间间距(airgap) | 建议大于等于 4 倍 MIPI 线宽,至少要 3 倍 MIPI 线宽。 |

| MIPI 与其它信号间距(airgap) | 建议大于等于 4 倍 MIPI 线宽,至少要 3 倍 MIPI 线宽。 |

eMMC PCB 设计

| 参数 | 要求 |

|---|---|

| 走线阻抗 | 单端 50ohm±10%。 |

| 源端匹配电阻 | 22ohm,摆放位置距离 A210 小于 500mil。 |

| 时钟与数据之间等长 | <100mil。 |

| 走线长度 | <3.5 inches。 |

| eMMC信号线之间间距(airgap) | 至少 2 倍 eMMC 线宽。 |

| eMMC与其它信号间距(airgap) | 建议 3 倍线宽,至少 2 倍 eMMC 线宽。 |

| 各信号所允许过孔数量 | 建议不超过 2 个。 |

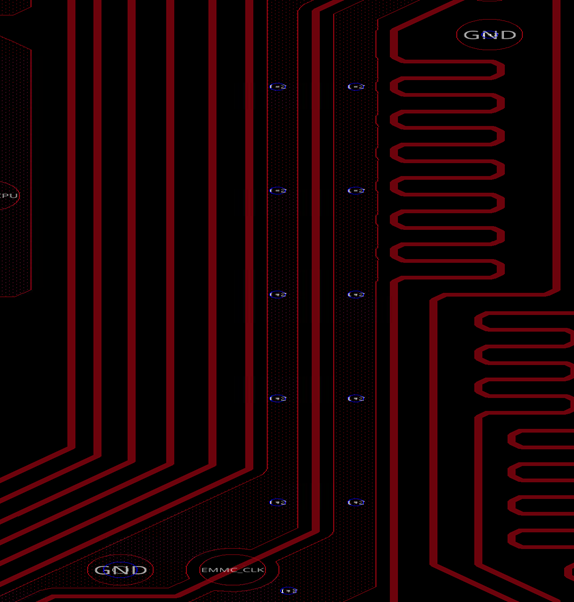

eMMC 信号换层前后,参考层建议都为地��平面,在信号过孔 30mil (过孔和过孔的中心间距)范围内建议添加地回流过孔,改善信号回流路径,地过孔需要把信号换层前后地参考平面连接起来。

eMMC 布线要求示意图如下所示。

SDIO PCB 设计

SDIO 布线要求示意图如下所示。

| 参数 | 要求 |

|---|---|

| 走线阻抗 | 单端 50ohm 。±10%。 |

| 时钟与数据之间等长 | < 120mil。 |

| 走线长度 | PCB长度(inch)× 4 + 电路上的电容值(pF),需要 <27pF。例如:线路上放 10pF 电容,那么走线长度需要 <4inch。 |

| SDMMC/SDIO信号线之间间距(airgap) | 至少 2 倍 SDIO 线宽。 |

RGMII PCB 设计

RGMII 布线要求示意图如下所示。

| 参数 | 要求 |

|---|---|

| 走线阻抗 | 单端 50ohm ±10%。 |

| 源端匹配电阻 | 22ohm,摆放位置距离 A210 小于 500mil。 |

| (TXD-3, TXEN) to TXCLK 等长 | <100mil。 |

| (RXD-3, RXDV) to RXCLK 等长 | <100mil。 |

| 走线长度 | < 5 inches。 |

| RGMI 同组TX或RX信号线之间间距(airgap) | 建议 ≥2 倍 RGMI 线宽,或者仿真后约 5 %以内的串扰量也可接受。 |

| RGMI 与其它信号间距(airgap) | 建议 5 倍 RGMI 线宽,至少 2 倍 RGMI 线宽,或者用 GND 包地隔开。注意 TX 与 RX 间的近端串扰。 |

| clk 走线 | clk 建议包地走线。 |